Fターム[5J106CC46]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | フィルタ回路 (1,598) | デジタル型 (163)

Fターム[5J106CC46]の下位に属するFターム

D/A変換器出力型 (31)

アップダウンカウンタ出力型 (28)

Fターム[5J106CC46]に分類される特許

101 - 104 / 104

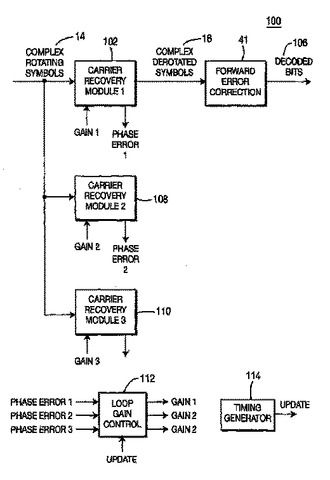

キャリア再生を向上させるシステム及び方法

キャリアを再生するシステム及び方法は、複数のキャリア再生モジュール(102、108、110)を含む。それぞれは、同じ入力シンボル(14)を処理し、それぞれは利得入力及びエラー出力を有する。ループ利得制御(112)は、キャリア再生モジュール(102、108、110)からエラーを受信し、キャリア再生モジュール(102、108、110)に利得を備える。現在の期間中のエラーに基づいて、ループ利得制御(112)は、最低のエラーをもたらしたモジュールを判定し、そのモジュールに関連した利得を最良の利得として選択する。この利得は、次の期間中に復号化するためのシンボル(16)を出力するモジュールに施される。  (もっと読む)

(もっと読む)

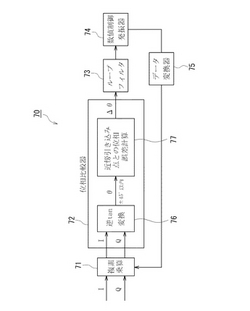

位相同期ループ回路

【課題】 ディジタル信号伝送においてキャリア引き込み特性の改善を図り、それを実現する位相同期ループ回路の構成を提供すること。

【解決手段】 位相同期ループ回路が複素乗算器71、位相比較器73、ループフィルタ74、数値制御発振器75等を備え、位相比較器73において、複素数信号の実数部及び虚数部から逆タンジェント特性を得て位相を算出する検出位相算出部76と、位相が異なる2つの直交ディジタル位相変調の信号点配置パターンにおける近傍引き込み点の位相と、上記で算出した受信信号の検出位相とのそれぞれの位相誤差を求める位相誤差計算部77とを備え、各ブロックにおけるパターン毎の位相誤差の2乗から尤度を求めて尤度の高い位相誤差の積分値を位相誤差として出力する。

(もっと読む)

タイムスレービング装置

本発明はパケットデータ伝送ネットワークにおけるタイムスレービングのための装置に関する。各データパケットはタイムラベルを有しており、前記装置はネットワークから受信したパケットを受け取ることを目的とした一時記憶手段を有している。

本発明によれば、前記装置は、

一時記憶手段が、ネットワークの特性に依存した所定の時間(IPDV)の間に受信したデータを記録することのできる記憶容量を有している

ように構成されており、

前記装置はさらに、

入来パケットのタイムラベルに応じてローカル受信クロックを再生する手段と、

前記所定の時間(IPDV)と再生されたローカル受信クロックとに依存するある時点において一時記憶手段内のデータを読み取る手段

を有している。

(もっと読む)

サブμ技術に適したデジタル位相同期回路

本発明は、デジタル制御発振器(4)と、位相検出器(11、12、13)と、デジタルループフィルタ(14)とを含む、デジタル位相同期回路に関するものである。上記デジタル制御発振器(4)は、出力周波数を生成するためのものである。上記の位相検出器(11、12、13)は、基準周波数と発振器(4)の出力周波数との位相差を検出するためのものであり、デルタシグマ周波数決定器(11)を含んでいる。上記デジタルループフィルタは、位相検出器の下流に接続されており、デジタル制御発振器(4)を駆動するためのものである。  (もっと読む)

(もっと読む)

101 - 104 / 104

[ Back to top ]