Fターム[5J106CC48]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | フィルタ回路 (1,598) | デジタル型 (163) | アップダウンカウンタ出力型 (28)

Fターム[5J106CC48]に分類される特許

1 - 20 / 28

送受信装置

【課題】構造簡単な距離を測定可能とした送受信装置の実現

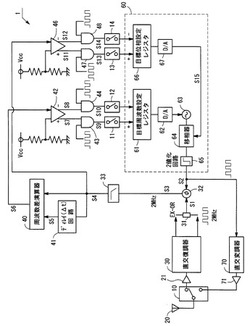

【解決手段】第1信号の受信と第2信号の送信とを共通化した送受信アンテナ20と、第1信号を復調して第1パルス信号を得る復調器30と、制御信号を入力して目標周波数を設定する目標周波数設定レジスタ61と目標位相を設定する目標位相設定レジスタ66とを有し、目標周波数設定レジスタに設定されている目標周波数と目標位相設定レジスタに設定されている目標位相とに一致した周波数と位相の第2パルス信号を出力するパルス発振器60を有する。第2パルス信号により搬送波を変調する変調器70と、第1パルス信号と、第2パルス信号との位相差を検出する位相比較器32を有する。また、位相差信号の時間変動からその時の第1パルス信号と第2パルス信号との周波数差をもとめ、その周波数差に基づいて目標周波数を制御する周波数制御装置と、位相差信号の示す位相差に基づいて目標位相を制御する位相制御装置とを有する。

(もっと読む)

半導体装置

【課題】レプリカ回路の精度を抜本的に向上する。

【解決手段】半導体装置10は、少なくともフィードバッククロック信号RCLK1に基づいて外部クロック信号CK,/CKを遅延させてなる内部クロック信号RLCLKを出力するDLL回路70と、内部クロック信号RLCLKに同期してデータを出力する複数の出力バッファ64aと、出力バッファ64aのレプリカであり、内部クロック信号RLCLKに同期してフィードバッククロック信号RCLK1を生成し、DLL回路70に供給する出力レプリカ73と、DLL回路70から内部クロック信号RLCLKを受け、複数の出力バッファ64a及び出力レプリカ73に伝送するクロックツリー72とを備え、クロックツリー72は、それぞれDLL回路70から複数の出力バッファ64a及び出力レプリカ73に至る内部クロック信号RLCLKの複数の伝送経路の信号線負荷が互いに実質的に等しくなるよう構成される。

(もっと読む)

半導体装置

【課題】再開トリガ信号を生成できないことによってリードデータの出力タイミングと外部クロック信号の同期が外れてしまうことを防止する。

【解決手段】DLL回路100には、当該DLL回路100を初期起動させるリセット信号RESETと、内部クロック信号LCLKの内部クロック信号ICLKに対する遅延量の制御を当該DLL回路100に再開させる再開トリガ信号RESTARTとが入力され、DLL回路100は、リセット信号RESET又は再開トリガ信号RESTARTが活性化されたことに応じて遅延量の制御を開始し、リセット信RESET号が活性化された後再開トリガ信号RESTARTが活性化される前には、当該DLL回路100のロック後にも遅延量の制御を継続し、再開トリガ信号RESTARTが活性化された後には、当該DLL回路100のロックに応じて遅延量の制御を停止する。

(もっと読む)

クロックアンドデータリカバリ回路

【課題】ジッタトレランスの低下、引き込み時間の増大、引き込みが不能等の問題を解消するクロックアンドデータリカバリ回路を提供する。

【解決手段】多相の抽出クロック信号で入力データをサンプリングするデータサンプリング回路11からのサンプリングデータ信号群の比較結果に基づきクロック信号の位相を進める信号(UP1)又は位相を遅らせる信号(DOWN1)、エラー検出時エラー信号(ERR)を出力する位相検出器12と、UP1/DOWN1信号を積分する第1の積分器13と、第2の積分器14と、第1の積分器の出力値(PPM)に基づき所定のパターンを生成するパターン発生器15と、第2の積分器の出力とパターン発生器の出力を合成する混合器16と、入力クロックを入力し前記混合器の出力信号に基づき位相を可変させた前記多相の抽出クロックを生成する位相補間器17から構成される。

(もっと読む)

位相補正方法、位相補正回路、及びそれを含む信号処理装置

【課題】ローカルオシレーターから出力された信号の位相補正方法を提供する。

【解決手段】方法は、同位相出力信号の位相と直交位相出力信号の位相との比較結果に相応するデジタルコードを発生させる。方法は、同位相出力信号の位相と直交位相出力信号の位相との差を90°にするために、直交位相差動入力信号とデジタルコードとに応答して、同位相出力信号の位相を調節し、同位相差動入力信号とデジタルコードとに応答して、直交位相出力信号の位相を調節する。

(もっと読む)

半導体装置

【課題】リード動作時における位相調整精度を低下させることなく、DLL回路の消費電力を低減する。

【解決手段】ODT機能を有するデータ入出力回路80と、データ入出力回路80の動作タイミングを規定する内部クロックLCLKを生成するDLL回路100とを備える。DLL回路100は、内部クロックLCLKを高精度に位相制御する第1のモードと、低消費電力で動作する第2のモードとを有し、データ入出力回路80がODT動作を行っていない場合には第1のモードで動作し、データ入出力回路80がODT動作を行っている場合には第2のモードで動作する。このように、ODT動作の有無によってDLL回路100の動作モードを切り替えていることから、厳密な位相制御が不要なODT動作時における消費電力を低減することが可能となる。

(もっと読む)

PLL回路、PLL回路無線通信機、及びPLL回路のロック検出方法

【課題】デジタル回路で構成出来、ロック検出のエラーやロストの発生を抑制することが出来ると共に、検出時間を短縮することが出来るPLL回路、無線通信機、及びロック検出方法を提供する。

【解決手段】ウィンドウ幅の異なる複数のロック検出部6b−1〜6b−nによる検出結果を用いて検出を行う。ロック判定部7は、複数のロック検出部6b−1〜6b−nによる検出結果に基づいて、ロック状態の検出を行う。

(もっと読む)

DLL回路及びこれを備える半導体装置

【課題】エイリアシングによるエイリアシングによる誤動作の発生が防止されたDLL回路を提供する。

【解決手段】外部クロック信号CLKを遅延させることによって内部クロック信号LCLKを生成するディレイライン110と、ディレイライン110の遅延量を設定するカウンタ回路130と、外部クロック信号CLKの位相に基づいて位相判定信号PD0を生成する位相検出回路140と、外部クロック信号CLKに含まれるジッタ成分が所定の周波数以上であることに応答して、位相判定信号PDに基づいたカウンタ回路130のカウント値の更新を禁止するアンチエイリアス回路200とを備える。これにより、エイリアシングによる誤動作によって内部クロック信号LCLKが誤った方向に連続制御されるという問題がなくなる。

(もっと読む)

DLL回路とその制御方法

【課題】安定的にジッタを低減する。

【解決手段】入力クロック信号CLKiを電圧制御遅延回路12を介して出力クロック信号CLKoとして出力すると共に、入力クロック信号CLKiと出力クロック信号CLKoとの位相比較結果に基づいて電圧制御遅延回路12における遅延量を制御する。位相比較結果判定回路15は、入力クロック信号CLKiと出力クロック信号CLKoとの位相比較結果を所定の期間に亘って積算し、積算結果の分布に基づいて遅延量を制御する。

(もっと読む)

DLL回路及びその制御方法

【課題】冗長な回路、配線を不要とし、回路規模の増大を回避し、デューティを変更可能とするDLLを提供する。

【解決手段】外部信号の第1遷移(Rise)を可変に遅延させる第1可変遅延回路(10R)と、外部信号の第2遷移(Fall)を可変に遅延する第2可変遅延回路(10F)と、第1可変遅延回路(10R)の出力信号と第2可変遅延回路(10F)の出力信号とを合成する合成回路(13)と、合成回路(13)の出力信号のデューティの変更と検出を行うデューティ変更検出回路(21)と、デューティ変更検出回路(21)のデューティ検出結果(DCC)に従って第1可変遅延回路(10R)又は第2可変遅延回路(10F)の遅延を可変させる遅延制御回路(15R、15F)と、を備える。

(もっと読む)

DLL回路

【課題】補間回路の最小動作周期を低減でき、DLLの最大動作周波数を向上させることができる、DLL回路を提供する。

【解決手段】位相検知回路21は、入力される基準クロック信号とレプリカ回路17から出力されるクロック信号との位相の差を検知し遅延制御回路22に出力する。遅延制御回路22は、位差の信号を基に、基準クロック信号の位相を調整する制御信号を出力する。そして、遅延制御回路22から出力される制御信号を基に、マルチプレクサ12、13は、粗調整遅延回路10からインバータ2段分の遅延差を有する信号を選択して出力し、第1の微調整遅延回路14は、マルチプレクサから入力した2段分の遅延差の信号を基に、インバータ1段分の遅延差を有する信号を出力する。第2の微調整遅延回路15は、この1段分の遅延差を有する信号に基づいてクロック信号の位相を調整する。

(もっと読む)

電圧制御発振器

【課題】ループフィルタの変化電圧範囲と電圧制御発振器との許容入力範囲を整合させるためにシフト電圧生成回路を設けるが、基準電圧電源やグランドからの電源変動が電圧制御発振器の制御入力電圧に重畳し、正確な周波数の信号を供給できない問題があった。

【解決手段】本発明の電圧制御発振器のシフト電圧生成回路は、同じ基準電圧電源から加算電圧信号と中間基準電圧信号とを作成することにより、電圧変動波形の位相を同じくし、オペアンプの差動入力にそれぞれを入力し電圧変動を除去する。また、基準電圧電源と加算電圧信号あるいは中間基準電圧信号出力との間にローパスフィルタを設け、電圧変動を抑制する。これにより、電圧変動のない制御入力電圧が電圧制御発振器に入力でき、正確な周波数の出力信号を供給可能になる。

(もっと読む)

位相検出装置、位相比較装置およびクロック同期装置

【課題】クロック同期システムに用いる位相比較器として、次段のカウンタに影響を与えることなく、クロックの同期がとれた際に確実にロックをかけること。

【解決手段】本発明は、基準クロックの位相に対する比較クロックの位相のずれを検出する第1の位相比較部K1aと、基準クロックおよび比較クロックのいずれか一方について所定時間遅延または進んだ状態での両クロックの位相のずれを検出する第2の位相比較部K1bと、第1の位相比較部K1aの出力と第2の位相比較部K1bの出力との論理積を位相ずれの検出結果として出力する論理積部AND1とを備える

(もっと読む)

周波数制御回路およびCDR回路

【課題】調整のための外部接続端子を必要とする部品や外部接続部品を必要とする部品を不要にする。

【解決手段】CDR回路は、周波数制御回路と、制御電圧に応じて発振周波数が制御されかつ入力データにより発振位相が制御される再生クロックを生成する第1のVCO2と、再生クロックによって入力データのデータ識別を行うFF1と、制御電圧に応じて発振周波数が制御される第2のVCO3とを備える。周波数制御回路は、第2のVCO3の出力信号の周波数を参照クロックの周波数と比較し、検出した周波数差に応じた信号を出力する周波数比較器4と、周波数比較器4の出力信号に応じて出力するデジタル値を上下させるアップダウンカウンタ5と、アップダウンカウンタ5の出力をアナログ信号に変換してVCO2,3の制御電圧として出力するD/A変換器6とから構成される。

(もっと読む)

DLL回路及びこれを備える半導体装置、並びに、データ処理システム

【課題】クロックの周波数が高い場合であっても、パルスの消失リスクが少ないDLL回路を提供すること。

【解決手段】DLL回路100において、CKとLCLKの各立ち上がりエッジの位相を比較して判定信号R−U/Dを生成する位相判定回路111と、CKとLCLKの各立ち下がりエッジの位相を比較して判定信号F−U/Dを生成する位相判定回路112と、判定信号R−U/Dに基づいてLCLKRのアクティブエッジの位置を調整する第1の調整回路と、判定信号F−U/Dに基づいてLCLKFのアクティブエッジの位置を調整する第2の調整回路と、LCLKRとLCLKFに基づいてLCLKを生成するクロック生成回路と、LCLKRのアクティブエッジの調整方向とLCLKFのアクティブエッジの調整方向とが互いに逆方向であることに応答して、第2の調整回路による調整動作を停止させる停止回路150とを備える。

(もっと読む)

クロック信号生成回路とクロック信号生成方法

【課題】複数系統の基準信号のいずれか、又は全てが断となってしまった場合でも、安定してクロック信号を生成することができるようにする。

【解決手段】断検出部2−A,2−Bで現用系の基準信号Aと予備系の基準信号Bの断を検出するようにし、断検出時には断検出信号を制御部8へ出力する。制御部8は、断検出部2−Aからの断検出信号を受け取ると、入力切替部1の導出を基準信号Bに切り替え、その後、断検出部2−Bからの断検出信号を通知されると、制御電圧保持部6の保持電圧の更新を停止させ、切替部7の導出を制御電圧生成部5で生成される制御電圧から制御電圧保持部6に保持される保持電圧に切り替える。

(もっと読む)

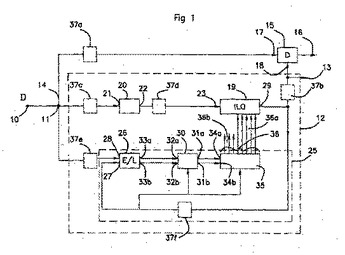

外部制御を必要としないデジタル位相ロックによるクロック抽出装置

本発明は、注入ロック発振器(19)と、デジタル位相検出器(26)を有する位相制御ループ(25)とを備えた、ベースバンドシリアル信号からクロックを抽出する装置に関する。発振器(19)はその周波数の値を制御するデジタル制御入力部(24)を備え、位相制御ループ(25)は、デジタル位相検出器(26)から供給されるデジタル信号の相対値を累算し、発振器(19)用のデジタル形態の制御信号を渡す、カウント回路(30、35)を備える。  (もっと読む)

(もっと読む)

クロックアンドデータリカバリ回路

【課題】クロックアンドデータリカバリ回路において、周波数追従ループのジッタ耐性を向上させる。

【解決手段】位相検出器210は、同期クロック信号とシリアルデータの位相を比較して比較結果に応じた位相誤差信号を出力する。積分器230は、位相誤差信号を積分してシリアルデータの位相変動に追従するための位相補正制御信号を得る。積分器240は、所定の長さの平滑期間毎に位相誤差信号を積分して平滑誤差信号を得る。パターン発生器250は、所定の長さのパターン発生期間毎に、平滑誤差信号に応じた頻度で同期クロック信号の位相を変更するパターンを発生して周波数補正制御信号として出力する。積分器240は、周波数補正制御信号がフィードバックされ、該周波数補正制御信号における頻度の変動方向に応じて、平滑化期間の長さを変更する。

(もっと読む)

クロックアンドデータリカバリ回路

【課題】クロックアンドデータリカバリ回路において、周波数追従ループのジッタ耐性を安定させる。

【解決手段】位相検出器210は、位相補間器270からの同期クロックとシリアルデータの位相を比較して比較結果に応じた位相誤差信号を出力する。第1の積分器230は、位相誤差信号を積分してシリアルデータの位相変動に追従するための位相補正制御信号を得る。第2の積分器240は、位相補正制御信号をさらに積分してアップ/ダウン信号を得る。パターン発生器250は、アップ/ダウン信号からシリアルデータの周波数変動に追従するための周波数補正制御信号を生成する。パターン発生器250のパターン長と第2の積分器240のカウント幅の積は、第1の積分器230のカウント幅が大きいほど大きくなる大きさの閾値以上である。

(もっと読む)

半導体集積回路

【課題】本発明は、Ser/Des回路において、休眠ステートからパワーアップの状態へ遷移した際の受信エラーを減少できるようにする。

【解決手段】たとえば、受信機21が、休眠ステートP1からパワーアップの状態P0に遷移したとする。すると、リセット制御回路21mは、ディレイ回路21m-1によって、PLL31からのシステムクロックのカウントを開始する。そして、ディレイ回路21m-1がXサイクルをカウントした後に、リセット制御回路21mは、ディジタルフィルタ21eおよびPI制御回路21fのリセットを解除するように構成されている。

(もっと読む)

1 - 20 / 28

[ Back to top ]