Fターム[5J106CC52]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 周波数変換回路 (1,116) | 分周回路 (990)

Fターム[5J106CC52]の下位に属するFターム

可変分周回路 (277)

Fターム[5J106CC52]に分類される特許

701 - 713 / 713

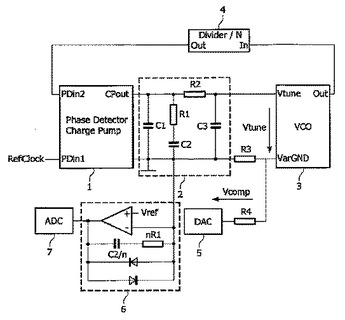

電圧制御周波数発生器における妨害を補償する装置及び方法

本発明は、電圧制御周波数発生器を有する位相同期ループにおいて妨害を補償する装置及び方法であって、周波数発生器が同調電圧Vtuneにより公称周波数に同調され、この周波数発生器の実際の周波数は周波数比較により基準周波数と比較され、周波数比較を介して偏差が検出された場合に再調整され、妨害が発生した場合に同調電圧Vtuneが妨害事象に依存する妨害電圧Vstorにより変えられ、かくして公称周波数から逸脱した周波数が発生し、該周波数偏差が位相同期ループにより再び補正されるような装置及び方法に関するもので、電圧制御周波数発生器を有する位相同期ループにおいて妨害補償をする装置及び方法を提供する目的に基づき、既知の妨害事象が起きたならば、この方法で既定の公称周波数からの偏差を避ける。この目的は、本発明により、もし既知の妨害事象が起きるならば、妨害電圧Vstorを補償する電圧Vcompが妨害電圧Vstorに同期して符号を反転して生成され、妨害電圧Vstorに重畳される、という方法により達成される。

(もっと読む)

(もっと読む)

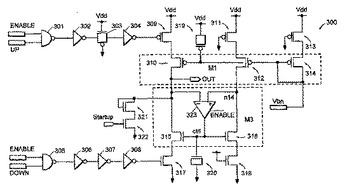

PLL/DLL用の高出力インピーダンスチャージポンプ

プルアップ回路とプルダウン回路と演算増幅器とを含む、位相ロックループ/遅延ロックループで使用するためのチャージポンプ。チャージポンプはプルアップおよびプルダウン回路の動作に関連したスタティック位相誤差を最小限にするように設計される。演算増幅器の使用はまた、低電源電圧の影響を軽減する。  (もっと読む)

(もっと読む)

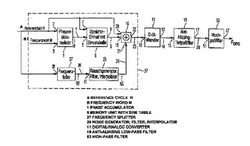

直接デジタル合成方式による周波数合成器

直接デジタル合成方式による周波数合成器は、入力(3)に存在する位相増分Mによって位相信号Pを周期的に増加するための位相アキュムレータ(1)と、位相信号Pの位相値に対応する正弦関数値を決定するため正弦関数値表をメモリーセルに記憶する記憶装置(6)と、時間対離散の正弦関数値を擬似アナログ正弦時間関数に変換するためのデジタル−アナログ変換器(11)と、擬似アナログ正弦時間関数を平滑化するためのアンチエイリアシングローパスフィルタ(16)とを備える。直接デジタル合成方式による周波数合成器はさらに、記憶装置(6)とデジタル−アナログ変換器(11)との間に接続された、時間対離散の正弦関数値に非周期的信号(NS)を重ね合わせる加算器(19)を含む。 (もっと読む)

可調周波数変換器

回路基板にマウントされた電気回路を有する可調周波数変換器が開示される。上記回路は、共振器を備える位相同期ループ(PLL)を提供するにように設計されている。柔軟な材料が回路基板と共振器の間に配置される。電導性リードにより短絡させられる少なくとも1つの受動素子が共振器に作動的に接続される。周波数変換器の共振周波数は、電導性リードを切断し、関連付けられた受動素子を活性化させることにより変更することができる。 (もっと読む)

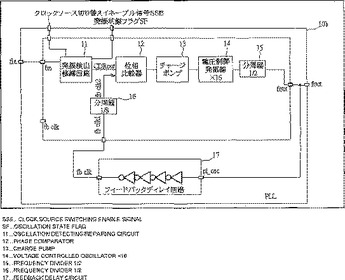

半導体集積回路装置

半導体集積回路装置におけるクロック発生器には、発振検出修繕回路11が設けられている。この発振検出修繕回路11は、外部接続されたクロック発振器が生成したクロック信号finの正常/異常を検出する。クロック信号finが正常の際には、該クロック信号finを選択して出力する。また、クロック信号finが異常の場合には、発振検出修繕回路11が生成したクロック信号を選択して出力する。クロック発生器は、発振検出修繕回路11が選択して出力するクロック信号に基づいてシステムクロックを生成する。また、クロック信号finが異常の場合、CPUは、各モジュールを停止させた後、該CPUを停止させる異常終了処理を実行する。  (もっと読む)

(もっと読む)

タイムベース用のレイアウト

【課題】シリコン共振器におけるように必ずしも温度安定性を必要としない周波数を有し、しかも周囲の熱的条件に係わらずに正確で低コストのタイムベースを得るために使用されることのできる共振器に基づいたレイアウトを提供すること

【解決手段】二つの発振器を含むタイムベースであって、その一つは、他方よりも低い周波数を有し、後者は断続的にスタンバイモードにセットされ、二つの発振器間の周波数差により第1安定時間基準(REF)、最も低い周波数を有する発振器の周波数を分周することにより得られる第2永久的時間基準(RTC)、及び、第1安定時間基準(REF)により決定される時間間隔の間に第1発振器(OSC1)により計数されるパルスに依存する除算因子を発生する。

(もっと読む)

電圧制御発振器

【課題】より適切なゲイン調整を可能とする電圧制御発振器を提供する。

【解決手段】電流源112は、第1の入力端子aへの入力電圧に応じて第1の電流を出力すると共に、入力電圧に対する第1の電流の変化量の変更制御が可能に設定される。第2の電流源114は、第2の入力端子bへの入力電圧に応じて第2の電流を出力すると共に、入力電圧に対する第2の電流の変化量の変更制御が可能に設定される。制御電圧発生回路116では、第1及び第2の電流を合成した合成電流に基づいて制御電圧を出力する。そしてリングオシレータ118では、この制御電圧に応じた周波数の出力パルスを発振する。

(もっと読む)

多層基板の実装構造、その多層基板の実装構造を用いたクロック変換器およびそのクロック変換器を備えた電子機器

【課題】多層基板構造を工夫して各機能グループのグランドの電位を安定化させ、かつ、ノイズを生じさせないようにして、ジッタの少ないクロック変換器を実現する。

【解決手段】各機能グループとして分離されたAグループ1、Bグループ2、Cグループ3、Dグループ4中の回路部品は、それぞれ対応して設けられている第1層のグランドパターンに接続され、かつスルーホールを通して第3層の電源層に接続されている。各グランド層は共通化または分離される。各機能グループの第1層のグランドパターンは他の機能グループのグランドパターンから共通化または分離されているので、その電位は常に安定している。また、各機能グループ中の部品は第2層の第1グランド層、第4層の第2グランド層から離れているのでノイズの影響を受けない。

(もっと読む)

半導体集積回路

【課題】制御電圧対発振周波数特性が調整可能なVCOを含む半導体集積回路を提供する。

【解決手段】この半導体集積回路は、リング状に直列に接続された複数のインバータと、バイアス電圧VBP1に従って電源電位VDDから複数のインバータに向けてそれぞれ電源電流を流す第1群のPチャネルトランジスタQP11等と、バイアス電圧VBN1に従って複数のインバータから電源電位VSSに向けてそれぞれ電源電流を流す第1群のNチャネルトランジスタQN11等と、バイアス電圧VBP2に従って電源電位VDDから複数のインバータに向けてそれぞれ電源電流を流す第2群のPチャネルトランジスタQP21等と、バイアス電圧VBN2に従って複数のインバータから電源電位VSSに向けてそれぞれ電源電流を流す第2群のNチャネルトランジスタQN21等とを具備する。

(もっと読む)

PLL回路

【課題】 出力信号のS/Nが高く、最大ロックアップ時間が短くかつ低廉なPLL回路を提供する。

【解決手段】 出力信号のS/Nが高くするために水晶電圧制御発振器1を用いる。また、M相位相シフト回路4が基準信号SREFを略同一周波数のM相の信号を生成し、セレクタ5が該M相の信号の中から基準信号SREFとの位相差が最小になる信号を選択して比較信号SCOMとして出力する。これにより、比較信号SCOMと基準信号SREFとの位相差が小さくなるので、最大ロックアップ時間を短縮できる。また、水晶電圧制御発振器を一つしか用いないので、コストを抑えることができる。

(もっと読む)

半導体集積回路

【課題】 高い周波数範囲と低い周波数範囲との広い範囲においてそれぞれ良好な特性を得ることの可能なPLL回路を提供する。

【解決手段】 制御電圧Vcに応じた周波数で発振動作する電圧制御発振器31を有し、発振信号を分周した比較信号φcompと基準クロックφinとの位相比較を行って、該位相比較の結果を制御電圧Vcにフィードバックさせることで基準クロックφinと発振信号φoutとを同期させるPLL回路において、電圧制御発振器31に、制御電圧Vcを制御電流Icに変換する電圧電流変換回路311と、制御電圧にほとんど依存しない補助電流Isを制御電流Icに付加する補助電流付加回路314と、制御電流Icの大きさに応じた周波数で発振動作する周波数可変発振器162と、制御電圧Vcの値に基づき補助電流付加回路314の動作状態のオン・オフを切り換える制御手段32とを設けた。

(もっと読む)

電圧制御発振器の自走周波数の自動調整機能を有する位相ロックループ回路

【課題】 高度の安定性を有する基準クロック信号を発生するための回路を必要とせず、従って、動作安定性がそのような回路の安定性によって影響されることのない、電圧制御発振器(VCO)の自走周波数の自動調整機能を有するPLL回路を提供する。

【解決手段】 PLL回路20では、位相比較器26の比較結果信号が所定レベルにある期間中にVCO22が出力するパルス信号のパルス数をカウントし、そのカウント値に基づいて、マイクロコンピュータ32がディジタルデータを更新する。DAC36がそのディジタルデータに対応したアナログ信号を発生する。このアナログ信号と、位相比較器の比較結果信号をローパスフィルタ28で平滑化した信号とを、結合器30で加え合わせ、その加え合わせた信号をVCOの周波数制御信号とすることで、VCOの自走周波数が自動調整されるようにした。

(もっと読む)

発振器及びそれを用いた位相同期ループ回路

制御信号に信号を加えることによって周波数を制御することが可能な変調機能を備えた発振器(1083)、及びそれを用いたPLL回路(108A)において、発振器は、インバータ又はバッファ及び制御信号により遅延値が制御されるカスケード接続された複数の遅延段(201〜203)を有し、反転位相により閉ループを形成するリング発振器(200)からなり、複数の遅延段の一部において制御信号に変調信号を加えることにより発振周波数を変調する変調機能を備える。 (もっと読む)

701 - 713 / 713

[ Back to top ]