Fターム[5J106CC52]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 周波数変換回路 (1,116) | 分周回路 (990)

Fターム[5J106CC52]の下位に属するFターム

可変分周回路 (277)

Fターム[5J106CC52]に分類される特許

61 - 80 / 713

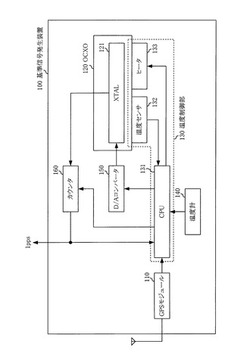

基準信号発生装置および基準信号発生方法

【課題】基準信号発生装置全体の消費電力を削減する。

【解決手段】OCXO120が、GPSモジュール110が同期信号を受信している間、当該同期信号を用いて基準信号を発生し、GPSモジュール110が同期信号を受信していない間は、あらかじめ設定された値を用いて基準信号を発生し、温度制御部130が、GPSモジュール110が同期信号を受信している間、OCXO120の温度を所定の温度よりもあらかじめ設定された温度だけ高い温度で変化させ、GPSモジュール110が同期信号を受信していない間は、OCXO120の温度をGPSモジュール110が同期信号を受信しなくなった際の温度に固定させる。

(もっと読む)

PLL回路

【課題】 基準周波数断時におけるフリーランの出力周波数の精度を向上させるPLL回路を提供する。

【解決手段】 比例積分方式のPLL回路を用いて、積分器14の後にA/D変換部15とパタン生成部16を付加した構成とし、A/D変換部15が、ロック時の積分器14の出力電圧をデジタル信号として得て、ロック外れ時はロック時のデジタル信号を保持する機能を備え、ロック外れ時で基準周波数断時には、保持したデジタル信号に応じてパタン生成部16がパタン生成し、セレクタ13によって積分器14に出力するものであり、基準周波数断時には、パタン生成の波形を積分器14に代替入力するPLL回路である。

(もっと読む)

PLL回路

【課題】 電源起動からロックまでの時間を短くすると共に、電源断時に電荷を速く放電できるPLL回路を提供する。

【解決手段】 位相の進み/遅れを検出器11で検出し、位相の進み/遅れに相当する信号を積分器12で積分し、起動パルス生成部13が、電源起動を検出し、ロックまでの時間に基づいたパルス幅のパルスをLPF5と積分器12に出力し、LPF5と積分器12が、起動パルス生成部13からのパルスによって内部のコンデンサを充電すると共に電源断で内部のコンデンサに蓄積された電荷を放電するPLL回路である。

(もっと読む)

回路装置及び電子機器

【課題】低消費電力でキャリブレーションができる回路装置及び電子機器等を提供すること。

【解決手段】回路装置は、無線による送信処理を行う送信回路100と、送信回路100を制御する制御部110とを含む。制御部110は、第1の送信期間では、送信回路100のキャリブレーションパラメーターCLPとして、第1のキャリブレーションパラメーターCLP1を設定し、送信回路100は、第1の送信期間では、第1のキャリブレーションパラメーターCLP1に基づく第1の送信処理を行う。制御部110は、第2の送信期間では、キャリブレーションパラメーターCLPとして、第1の送信処理での送信状態の検出結果に基づいて更新された第2のキャリブレーションパラメーターCLP2を設定し、送信回路100は、第2の送信期間では、第2のキャリブレーションパラメーターCLP2に基づく第2の送信処理を行う。

(もっと読む)

PLL回路

【課題】特性の向上を図ることが可能なPLL回路を提供する。

【解決手段】PLL回路は、発振信号に基づいた充放電信号に応じて、充放電電流を出力端子に流すチャージポンプを備え、出力端子に一端が接続され、ローパスフィルタを構成する可変抵抗を備え、可変抵抗の他端に一端が接続され、接地に他端が接続され、ローパスフィルタを構成する容量を備え、前記チャージポンプ電圧を電流に変換した動作電流を出力する電圧電流変換器を備え、リング状に直列に接続された複数のインバータを有し、インバータを動作させるための動作電流が供給され、動作電流に応じて発振周波数が制御される発振信号を出力する電流制御発振器を備え、可変抵抗の他端のフィルタ電圧と、第1の基準電圧およびこの第1の基準電圧よりも高い第2の基準電圧とを比較する第1の比較回路を備え、その比較信号に基づいて、電流制御発振器のインバータの段数を制御する制御回路を備える。

(もっと読む)

半導体装置

【課題】広範囲、光分解能に周波数を可変することのできるクロック信号を生成する。

【解決手段】オペアンプAMP1は、正入力部と負入力部が等しい電圧となるようフィードバックがかかり、回路ノードfbckは、参照電圧VREFIに等しい電圧となる。デコーダDECは、制御信号CNT7,CNT6をデコードし、トランジスタT2〜T5のいずれか1つをオンさせる。この構成によって、回路ノードfbckが、参照電圧VREFIと同電位となるようフィードバック制御がかかるため、トランジスタT2〜T5のON抵抗を大幅に低減することができ、周波数精度の悪化を防止することができる。

(もっと読む)

同期信号生成装置および同期信号生成方法

【課題】ホールドオーバー状態からGPSロック状態に復帰する際の基地局の状態に応じて、内部パルスおよび内部周波数信号をGPS基準パルスに同期させた状態に復帰させることができる同期信号生成装置および同期信号生成方法を提供することである。

【解決手段】本発明に係る基地局3にパルスを提供する同期信号生成装置は、GPS衛星から受信した信号からGPS基準パルスを生成するGPS受信器11と、内部周波数信号を生成する発振器15と、内部周波数信号を分周して内部パルスを生成する分周器12と、GPS基準パルスと内部パルスとを比較して前記内部パルスを前記GPS基準パルスに同期させる同期部14と、基地局3の状態に応じて、ホールドオーバー状態からGPSロック状態に復帰するときの、同期部14のループタイムを決定する制御部13と、を備える。

(もっと読む)

PLL回路

【課題】PLL回路のロック状態での定常位相誤差を抑制する。

【解決手段】PLL回路は,レファレンスクロックとフィードバッククロックの位相を比較し,当該位相の差を示す位相比較信号を出力する位相比較器と,位相比較信号が示す位相の差に応じた期間,第1のチャージポンプ電流と第2のチャージポンプ電流とを出力するチャージポンプ回路と,第1及び第2のチャージポンプ電流に基づく電荷を蓄積するキャパシタを有し,蓄積電荷による制御電圧を生成するループフィルタと,制御電圧に応じた周波数の出力クロックを生成する発振器と,出力クロックを分周して前記フィードバッククロックを出力する分周器とを有し,さらに,ロック状態のときに,位相比較信号が示す位相の差に応じて,当該位相の差が抑制されるように,第1または第2のチャージポンプ電流の電流値を調整するチャージポンプ調整回路とを有する。

(もっと読む)

信号伝搬遅延を補償するための装置及び方法

【課題】1以上の伝送接続上の電気信号など、1以上の信号の伝搬遅延または時間を補償する装置及び方法を提供し、実装のための複雑な演算手段を必要とせず、自動的に伝搬時間の補償を行なうことを可能とする。

【解決手段】第1伝送接続(104)の第1端(106)と第2端(108)の間を伝搬中に第1周期信号ref(t)が受ける遅延τを補償するための装置(100)であり、前記第1信号ref(t)に対応し、その位相が遅延τに等しい時間により位相前進された第2信号ref(t+τ)を生成可能な第1手段(114)と、前記第1伝送接続の前記第2端で取得され前記第1信号ref(t)に対応し、その位相が遅延τにより遅延された第3信号ref(t-τ)と、前記第2信号ref(t+τ)とから、前記第1信号ref(t)と同位相である第4信号を生成可能な第2手段(116)とを少なくとも備える。

(もっと読む)

PLL回路

【課題】平均値計算器に演算能力が比較的低い計算器を用いることが可能な技術を提供することを目的とする。

【解決手段】PLL回路は、基準クロック信号frと比較クロック信号fpとの位相比較を基準クロック信号frの周期毎に実行し、高電圧レベルの第1パルス及び低電圧レベルの第2パルスを含む信号を、前記第1及び第2パルスの当該周期単位でのパルス幅の差が当該位相比較での位相差に対応するように生成する位相比較器2と、位相比較器2が生成した信号の電圧を基準クロック信号frの周期毎に平均化する平均値計算器3とを備える。そして、平均値計算器3からの出力を基準クロック信号frの1周期分よりも長く遅延させるm周期遅延器5を備える。

(もっと読む)

無線通信装置

【課題】無線通信装置の変調精度の低下を抑制しつつ、スプリアスによる受信特性の低下を抑制する。

【解決手段】デジタル部2は、アナログ部1にて周波数変換された受信信号の復調処理を行う。PLL回路25は、前記デジタル部のクロックを発生する。PLL設定変更部24は、現在の通信状態が受信状態であり、チャネル周波数内にスプリアスが存在し、受信電力が閾値に満たない場合、クロックCKのジッタを増加させ、それ以外の場合、クロックCKのジッタを通常設定にする。

(もっと読む)

シリアルデータの受信回路、受信方法およびそれらを用いたシリアルデータの伝送システム、伝送方法

【課題】単一の伝送路で、高速なシリアルデータを伝送可能な伝送技術を提供する。

【解決手段】受信回路100は、pビットに2×q回(p、qは実数)の割合で第1レベルから第2レベルへの遷移が生ずるように生成されたシリアルデータDSOUTを受ける。VCO60は、入力された制御電圧Vcnt2に応じた周波数を有するサンプリングクロック信号CLK4を発生する。第1分周器22は、サンプリングクロック信号CLK4を分周比Mで分周する。第2分周器24は、受信したシリアルデータに応じたクロック信号CLKINを分周比Nで分周する。周波数比較器20は、第1分周器22の出力信号と第2分周器24の出力信号の位相差に応じた位相周波数差信号PFDを発生する。制御電圧生成回路42は、位相周波数差信号PFDに応じて、チャージポンプ回路40の周波数を調節するための制御電圧Vcnt2を生成する。

(もっと読む)

周波数シンセサイザおよび時間デジタル変換器

【課題】周波数シンセサイザにおいて、ループ帯域内位相ノイズの低減を小面積かつ低電流の構成で実現する。

【解決手段】周波数シンセサイザは、発振器1と、発振器1出力の分周信号CKVと参照信号Frefとの正規化された位相差を検出するTDC回路7とを備え、TDC回路7によって検出された正規化された位相差に基づいて発振器1の周波数を制御する。TDC回路7は、第2の発振器711と、第2の発振器711の出力信号OSC2の周期数をカウントするカウンタ712とを備え、カウンタ712の出力から、分周信号CKVの周期に相当するカウンタ値と、分周信号CKVと参照信号Frefとの位相差に相当するカウンタ値とを得て、これらのカウンタ値に基づいて、正規化された位相差を算出する。

(もっと読む)

注入同期発振器

【課題】逓倍数が任意の大きな数であっても、位相雑音が低減された注入同期発振器を得る。

【解決手段】注入同期発振器は、注入される注入信号に同期して自励発振周波数の信号を発振する発振器を備える注入同期発振器において、上記自励発振周波数と略同じ周波数の逓倍数分の1の周波数の基準信号が入力されるともに該基準信号にトリガーされてパルスを生成するパルス発生回路と、上記パルス発生回路で生成したパルスとタイミングが異なる少なくとも1つのパルスを生成するとともに該生成されたパルスと上記パルス発生回路で生成したパルスとを合わせて注入信号として出力するパルス数増倍回路と、を備える。

(もっと読む)

半導体装置

【課題】再開トリガ信号を生成できないことによってリードデータの出力タイミングと外部クロック信号の同期が外れてしまうことを防止する。

【解決手段】DLL回路100には、当該DLL回路100を初期起動させるリセット信号RESETと、内部クロック信号LCLKの内部クロック信号ICLKに対する遅延量の制御を当該DLL回路100に再開させる再開トリガ信号RESTARTとが入力され、DLL回路100は、リセット信号RESET又は再開トリガ信号RESTARTが活性化されたことに応じて遅延量の制御を開始し、リセット信RESET号が活性化された後再開トリガ信号RESTARTが活性化される前には、当該DLL回路100のロック後にも遅延量の制御を継続し、再開トリガ信号RESTARTが活性化された後には、当該DLL回路100のロックに応じて遅延量の制御を停止する。

(もっと読む)

クロック発生器、電子機器、及びクロックを発生するための制御方法

【課題】周波数変調機能をオフした際のロックアップタイムを短縮することが可能なクロック発生器、及びクロック発生器の制御方法、並びに電子機器を提供すること。

【解決手段】周波数変調機能を有するクロック発生器で、リファレンスクロックを元にフィードバック制御を加えて、位相の同期した出力クロックを出力する位相同期ループと、出力クロックの周波数を変動させる変調制御回路と、を備え、変調制御回路は、周波数変調機能がオフされた際に、出力クロックの周波数を所望の周波数へ収束させるタイミングを速くする構成とする。

(もっと読む)

位相同期回路及び無線機

【課題】位相同期回路のセトリング時間を短縮する。

【解決手段】位相同期回路は、制御信号に応じた発振周波数を含む発振信号を生成する電圧制御発振器と、前記発振信号を分周して分周信号を生成する分周器と、前記分周信号と基準信号との位相を比較し、比較信号を生成する位相比較器と、前記比較信号に応じた電流を出力するチャージポンプと、前記電流をフィルタリングし、前記制御信号を生成するフィルタと、前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分が極小となった場合に検出信号を生成する周波数差検出回路と、前記検出信号が生成されると、前記分周信号と前記基準信号との位相を同期させる位相調整回路とを備える。

(もっと読む)

位相同期回路および無線受信装置

【課題】サブサンプリングPLLの利点を保持したまま、フラクショナル分周を実現する。

【解決手段】電圧制御発振器は、制御電圧に応じて周波数が制御される第1信号、および前記第1信号と逆相の第2信号を生成する。サブサンプリング位相比較器は、基準信号の周期毎に、前記第1信号および第2信号の電圧を標本化して、第1標本化電圧および第2標本化電圧を生成する。電流生成回路は、供給電圧に応じて第1電流信号を生成する第1のチャージポンプと、供給電圧に応じて前記第1電流信号と反対符号の第2電流信号を生成する第2のチャージポンプとを有する。セレクト制御手段は、前記第1および第2標本化電圧を前記第2および第1チャージポンプにまたはこれと反対に供給する第1、第2供給モードを選択的に実行する。ループフィルタは、前記第1、第2の電流信号の合成電流信号を平滑化して、前記電圧制御発振器に与える前記制御電圧を生成する。

(もっと読む)

半導体集積回路および無線通信装置

【課題】小規模かつ低消費電力で発振信号を生成可能な半導体集積回路およびこれを用いた無線通信装置を提供する。

【解決手段】半導体集積回路は、デジタル制御発振器と、カウンタと、時間デジタル変換器と、加算器と、制御信号生成部と、を備える。時間デジタル変換器は、発振信号と参照信号との位相差に対応する第3のデジタル信号を生成する。前記時間デジタル変換器は、分周器と、複数のインピーダンス素子と、位相差検出部と、を有する。分周器は、前記発振信号を分周して複数の分周信号を生成する。複数のインピーダンス素子は、前記複数の分周信号を分圧して、前記発振信号を遅延させた複数の遅延信号を生成する。位相差検出部は、前記参照信号と、前記複数の遅延信号のそれぞれと、を比較することにより、前記参照信号と前記発振信号との位相差に対応する前記第3のデジタル信号を出力する。

(もっと読む)

時間計測回路およびデジタル位相同期回路

【課題】発振器の周期を基準として発振器の出力信号と基準信号との位相のずれを検出する。

【解決手段】多相化回路2は、差動発振信号P1、P2をM(Mは2以上の整数)分周することにより、位相が互いに180/M度ずつ異なる多相化信号S1〜SNを生成し、フリップフロップF1〜FNは、基準信号RCKの入力に同期して多相化信号S1〜SNをそれぞれ取り込み、デコーダ3は、フリップフロップF1〜FNの出力信号Q1〜QNをデコードする。

(もっと読む)

61 - 80 / 713

[ Back to top ]