Fターム[5J106CC52]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 周波数変換回路 (1,116) | 分周回路 (990)

Fターム[5J106CC52]の下位に属するFターム

可変分周回路 (277)

Fターム[5J106CC52]に分類される特許

101 - 120 / 713

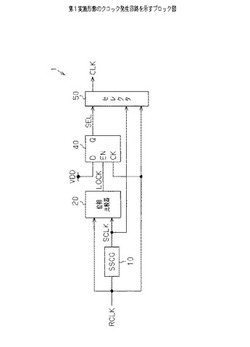

クロック発生回路

【課題】ロックアップタイムを短くすることのできるクロック発生回路を提供する。

【解決手段】クロック発生回路1は、基準クロックRCLKに基づいて、周波数を変調させた変調クロックSCLKを発生するスペクトラム拡散クロック発生回路10と、基準クロックRCLKと変調クロックSCLKとの位相の一致を検出したときにHレベルのロック信号LOCKを出力する位相比較器20とを含む。また、クロック発生回路1は、Hレベルのロック信号LOCKが出力されるまでは基準クロックRCLKを出力クロックCLKとして選択し、Hレベルのロック信号の出力に応答して変調クロックSCLKを選択するセレクタ50を含む。

(もっと読む)

同期回路

【課題】小面積で広帯域特性及び低位相雑音特性を得ることが可能な同期回路を提供する。

【解決手段】位相検出器11は、参照信号と帰還信号との位相差を検出する。電圧生成器12,13は、位相検出器の出力信号に基づき電圧を発生する。パルス発生器16は、参照信号に基づきパルス信号を生成する。電圧制御発振器14は、パルス信号に同期して、発振信号を発振する。分周器15は、電圧制御発振器からの信号を分周し、帰還信号を生成する。電圧制御発振器14は、電圧発生回路から供給される電圧レベルをシフトするレベルシフト回路14cと、電圧発生回路からの電圧とレベルシフト回路からのレベルシフトされた電圧により駆動される複数のインバータ回路14a、14bからなるリング発振器とにより構成され、インバータ回路の1つにパルス信号が供給される。

(もっと読む)

半導体装置及びその測定方法

【課題】従来の測定方法では、測定電流の精度を十分に確保できない問題があった。

【解決手段】本発明の半導体装置の測定方法は、外部端子TMと、出力信号の位相及び周波数に応じてチャージポンプ回路12を制御する位相周波数比較器11と、周波数制御電圧生成ノードVNDに対する電流を出力するチャージポンプ回路12と、チャージポンプ回路12が出力する電流に応じて周波数制御電圧を周波数制御電圧生成ノードVNDに生成するループフィルタ14と、周波数制御電圧に応じて出力信号の周波数を制御する電圧制御発振器15と、を有する半導体装置の測定方法であって、外部端子TMを介してチャージポンプ回路12の出力電流を含む第1、第2の測定電流のいずれか一方を測定し、外部端子TMに流れるリーク電流を含む第3の測定電流を測定し、第1、第2の測定電流とリーク電流との差分に基づき流出電流IS1又は流入電流IS2の電流値を算出する。

(もっと読む)

半導体装置

【課題】位相同期回路の面積を低減しつつ特性を保持するために、プロセスマイグレーションに利点のあるデジタル補償回路を適用し、位相余裕を確保する半導体装置を提供する。

【解決手段】半導体装置のデジタル補償型位相同期回路200において、発振ノードに容量を具備し、印加電圧で連続的に制御される電圧制御型発振器104を含む位相同期回路100と、入力される位相差に応じて電圧制御型発振器104の発振ノードの容量を可変に制御するデジタル補償回路201とを有する。従来方式の印加電圧によって利得が決定される電圧制御型発振器104を、デジタル補償回路201の制御信号によって利得を離散的に変化させる。デジタル補償回路201は、電圧制御型発振器104の発振ノードに、位相進みに対して負荷を印加し、位相遅れに対して負荷を減らし、最適な位相余裕が確保できるように動的に利得を制御する。

(もっと読む)

電圧電流変換回路及びこれを備えたPLL回路

【課題】電源電圧依存性が小さい電圧電流変換回路及びこれを備えたPLL回路を提供する。

【解決手段】電圧電流変換回路は、第1電圧が供給される第1導電型のトランジスタで構成され、第1電流に基づいて第2電流を生成するカレントミラー回路と、前記第1電流が流れる第2導電型の第1のトランジスタと、一端が前記第1のトランジスタのソースに接続され、他端に第2電圧が供給され、入力された制御電圧に応じて抵抗値が変化する可変抵抗と、前記第2電流が流れ、ドレインとゲートとが前記第1のトランジスタのゲートに接続され、ソースに前記第2電圧が供給され、ゲート幅Wとゲート長Lとの比W/Lが前記第1のトランジスタの比W/Lより小さい第2導電型の第2のトランジスタと、前記第1電流または前記第2電流に基づいて出力電流を出力する電流出力部と、を備える。

(もっと読む)

局部発振器

【課題】消費電力を増大させることなく、TDCレスが可能な局部発振器を提供することを目的とする。

【解決手段】発振器制御ワードに応じた発振周波数のN倍の周波数の発振信号を出力するデジタル制御発振器と、前記発振信号をN分周して、2N相のクロックを出力する分周器と、前記クロックを前記参照信号でラッチして、第1位相情報として出力する第1のフリップと、前記参照信号を遅延させて、遅延参照信号として出力する可変遅延回路と、前記クロックを遅延参照信号でラッチして、第2位相情報として出力する第2のフリップフロップと、前記可変遅延回路の遅延量を制御する遅延制御手段と、前記1および第2の位相情報に基づいて、発振器整数位相を出力するデータ変換手段と、発振器整数位相と前記発振器分数位相とを加算し、加算値を第3位相情報として出力する加算器とを備えている。

(もっと読む)

受信回路及びサンプリングクロック制御方法

【課題】1ユニットインターバルに対するサンプリング数を一定に保つことができる受信回路を提供することを課題とする。

【解決手段】1サイクル内で複数の異なる位相のクロック信号を生成するクロック発生回路(301)と、複数の異なる位相のクロック信号により入力データをオーバーサンプリングするオーバーサンプリング回路(303)と、オーバーサンプリング回路により出力されたデジタルデータの時系列の変化点を検出し、1ユニットインターバルの両端の2個のデータバウンダリを判定するデータバウンダリ判定回路(305)と、判定された2個のデータバウンダリの間の1ユニットインターバルのサンプリング数が閾値より多いときには、隣接する1ユニットインターバルのサンプリング数が一定となるようにクロック発生回路で生成するクロック信号の位相を制御するクロック位相制御回路(306)とを有する受信回路が提供される。

(もっと読む)

周波数シンセサイザ及び周波数シンセサイザの調整方法

【課題】位相雑音を改善すると共に、安定して作動する周波数シンセサイザ等を提供する。

【解決手段】電圧制御発振部から出力された周波数信号と周波数設定部から出力された周波数信号との差分を増幅して得られた差分信号を、前記周波数設定部から出力された周波数信号と直交する検波信号と直交検波して得た両周波数信号の位相差に基づいて前記電圧制御発振部の制御電圧を調整する周波数シンセサイザを立ち上げる際に、前記差分信号を得る差動増幅器から電圧制御発振部を切り離した状態で、第1の位相補正部により予め定めた補正量だけ前記検波信号の位相を補正し、第2の位相補正部により前記検波信号をクロック単位で遅らせて出力することにより、前記周波数設定部よりディジタルの周波数信号が出力された時点から前記差分信号が得られるまでのタイミングと、検波信号が得られるまでのタイミングとをそろえる。

(もっと読む)

アナログ及びデジタルフィードバック制御を備えた位相ロック・ループ(PLL)

PLL回路

【課題】ループフィルタの容量値を抑え、且つ動作を安定させることが可能なPLL回路を提供することを目的としている。

【解決手段】入力信号の位相と電圧制御発振回路の出力信号の位相とを比較し、位相差に応じた信号を出力する位相比較器と、前記位相比較器の出力信号に応じて充放電電流を生成するチャージポンプ回路と、前記チャージポンプ回路の出力を平滑し第一の制御電圧を生成するループフィルタと、前記ループフィルタから出力される前記第一の制御電圧を所定の電圧になるよう第二の制御電圧を生成する制御電圧生成回路と、を備え、前記第一の制御電圧と前記第二の制御電圧とが前記電圧制御発振回路に入力される。

(もっと読む)

PLL装置

【課題】外部からの基準周波数信号の振幅レベルの適正範囲内を特定し、その適正範囲の内外に応じて電圧制御発振器に制御電圧を供給するPLL装置において、温度により動作が不安定になることを防ぐこと。

【解決手段】制御電圧出力部に供給される信号を位相比較部と予備信号供給部との間で切り替える切り替え部と、前記基準周波数信号の信号路とアースとの間に設けられ、当該基準周波数信号の振幅レベルを規制するために、ダイオードを逆並列に接続した保護回路と、この保護回路の雰囲気温度を検出する温度検出部と、外部からの前記基準周波数信号の振幅レベルを検出するレベル検出部と、を備えるようにPLL装置を構成し、検出温度に応じて前記切り替えの基準となるしきい値を設定し、前記ダイオードの温度特性により前記振幅レベルが変わることに対応する。

(もっと読む)

電圧制御発振回路及びPLL回路

【課題】制御電圧に対する周波数の変化量を自由に調整できる電圧制御発振回路及びPLL回路を提供する。

【解決手段】制御電圧に応じて容量成分が制御される可変容量素子Cv1、Cv2と、可変容量素子に直列に接続された直列容量素子Cs1、Cs2と、可変容量素子と直列容量素子とから構成される直列回路に並列に接続された並列容量素子Cp1,Cp2と、可変容量素子と直列容量素子とから構成される直列回路に並列に接続され、誘導成分を構成する誘導素子Lとを有する電圧制御発振回路100において、直列容量素子及び並列容量素子は、各々その容量成分を切り換え可能な構成されており、直列容量素子の容量成分及び並列容量素子の容量成分を切り換えることにより、制御電圧に対する発振周波数の変化量が調整されている。

(もっと読む)

基準信号発生装置及び方法

【課題】 GPS信号の受信障害が発生しても、内蔵オシレータよりも高い周波数安定度の基準信号を発生することと、受信障害の発生前後で連続性の高い基準信号を出力することとを両立した基準信号発生装置を提供する。

【解決手段】 GPS受信機にて取得したGPS受信時刻と、そのGPS受信時刻の直前或いはその直後に標準電波受信機にて取得した標準電波受信時刻との時刻差を、予め定められた時間間隔毎に算出し、算出した時刻差と日時とを関連づけた時刻差データベースを構築する。GPS受信障害の発生を未検出のときGPS受信時刻に基づいて電圧制御発振器を制御して基準信号を発生し、GPS受信障害の発生を検出中は、時刻差データベースから取得した現在の日時に対応する時刻差に基づいて標準電波受信時刻を補正して電圧制御発振器を制御して基準信号を発生する。

(もっと読む)

クロック制御回路及びこれを備える半導体装置

【課題】高速且つ正確にDLL回路をロックさせる。

【解決手段】外部クロック信号CLKの位相に基づいて位相判定信号PD0を生成する位相判定回路140と、位相判定信号PD0の論理レベルに基づいてカウント値が更新されるカウンタ回路130と、カウント値に基づいて外部クロック信号CLKを遅延させることにより、内部クロック信号LCLKを生成するディレイライン110と、位相判定信号PD0が変化しない期間においてはカウンタ回路130の更新ピッチを最小ピッチの2倍に設定し、位相判定信号PD0が変化したことに応答してカウンタ回路130の更新ピッチを最小ピッチに設定するピッチ調整回路300と、を備える。これにより、高速且つ正確にDLL回路をロックさせることが可能となる。

(もっと読む)

クロック生成回路と半導体装置及びクロック生成方法

【課題】スペクトルの抑圧効果の高い変調波形を得ることができ、Hershey−kissによる変調方式と比べ、回路規模を小さくするクロック生成回路の提供。

【解決手段】変調波形生成部20は、SSCG変調波形として、tan波形またはtan+三角波を生成し、PLLループの低域パスフィルタ14の出力に、該SSCG変調波形を合成した信号を発振器(VCO)15に与える。

(もっと読む)

クロック切り替え回路

【課題】クロック切り替えの時間を短縮すること。

【解決手段】本発明は、光ケーブルを介して入力された光信号から抽出したクロック信号と、自回路内部のクロック源からのクロック信号との切り替えを行うクロック切り替え回路に適用される。本発明のクロック切り替え回路は、光信号からクロック信号を抽出するクロック抽出部と、前記クロック抽出部にて抽出されたクロック信号を、互いに異なる分周数で分周する複数の分周器と、前記複数の分周器にそれぞれ対応して設けられ、対応する分周器にて分周されたクロック信号のクロック周波数が所定のクロック周波数と一致する場合に同期信号を出力する複数の同期検出部と、光ケーブル接続が切断された場合、同期信号を出力した同期検出部に対応する分周器にて分周されたクロック信号から、当該クロック信号と同じクロック周波数成分を持ったクロック源からのクロック信号への切り替えを行うスイッチと、を有する。

(もっと読む)

PLL回路

【課題】 位相ノイズを低減し、設計が容易なPLL回路を提供する。

【解決手段】 PLL3が、基準周波数とVC−TCXO4からの出力を入力し、ロック動作を行い、ロック状態となると、セレクタ6は基準周波数を分周する第1の分周器2の出力を選択し、PLL3が、基準周波数入力断又はロック外れを検出すると、アラーム信号をセレクタ6に出力し、セレクタ6が、PLL3からのアラーム信号が入力されると、第1の分周器2の出力から、VC−TCXO4の出力を分周する第2の分周器5の出力に切り替えて出力し、PLL7が、セレクタ6の出力とVCXO8の出力とを入力し、ロック動作を行うPLL回路である。

(もっと読む)

半導体集積回路

【課題】複数の無線通信チャンネルについて、PLL回路全体の動作特性に基づいて電圧制御発振器の精密なキャリブレーションを行う。

【解決手段】半導体集積回路は、高周波信号を生成する電圧制御発振器を含むPLL回路と、電圧制御発振器のトランジスタに選択的に負荷される複数のキャパシタと、複数の無線通信チャンネルについて電圧制御発振器の発振周波数を補正するためのキャパシタに関する情報を格納する格納部と、キャリブレーションモードにおいて、複数の無線通信チャンネルについてPLL回路のループ特性を測定することにより補正用キャパシタに関する情報を格納部に格納し、通常動作モードにおいて、選択された無線通信チャンネルに従って、格納部に格納されている情報を読み出すことにより補正用キャパシタを決定するキャリブレーション回路とを具備する。

(もっと読む)

通信システム

【課題】製造ばらつき・温度変動に依存することなく、受信状態又は送信状態を良好に保つ事が出来る通信システムを提供すること。

【解決手段】電圧制御発振部(106)の発振周波数を制御するように、位相同期回路(100)からの周波数制御信号(c1)を用いて、第2のLCタンク回路及び第3のLCタンク回路の少なくとも1つの同調周波数を制御することで、受信周波数の同調を行い、Q値制御回路(110)からのQ値制御信号(b1)を用いて第2のLCタンク回路及び第3のLCタンク回路の少なくとも1つのQ値制御用可変抵抗の抵抗値を可変することにより、第2のLCタンク回路及び第3のLCタンク回路の少なくとも1つのQ値を制御して、受信帯域の最適化を行う。

(もっと読む)

位相検出回路およびPLL回路

【課題】2つのクロック信号の位相比較に基づき生成する2つのパルス信号の遅延時間を極力短くすることができ、かつ確実にリセットできる位相検出回路および該位相検出回路を備えたPLL回路を提供すること。

【解決手段】位相検出回路は、位相比較を行う2つのクロック信号の論理和信号と論理積信号とに基づき、進相側と遅相側の2つのパルス信号の生成に用いる一方の出力を、前記位相比較を行う準備動作状態と、前記位相比較を行った回路動作状態とに切り替えて保持するラッチ回路を備えている。

(もっと読む)

101 - 120 / 713

[ Back to top ]