Fターム[5J106CC52]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 周波数変換回路 (1,116) | 分周回路 (990)

Fターム[5J106CC52]の下位に属するFターム

可変分周回路 (277)

Fターム[5J106CC52]に分類される特許

141 - 160 / 713

信号処理装置

【課題】 外部からの基準信号の周波数変化が安定している状態であるかどうかをユーザが容易に判別可能とする。

【解決手段】 外部機器から供給された基準信号を入力する入力手段と、前記入力手段により入力された基準信号とクロックとの位相差を検出する位相検出手段と、前記位相検出手段の出力に応じた周波数の前記クロックを発生する発生手段と、前記位相検出手段の出力に基づいて前記入力手段により入力された基準信号の周波数と前記クロックの周波数との誤差を検出し、前記検出した誤差に基づいて前記基準信号の周波数変化の状態を示す情報を表示装置に表示する制御手段とを備える。

(もっと読む)

高周波発振源

【課題】3倍波を位相関係により抑圧して2倍波を出力する高周波発振源を得る。

【解決手段】2つの入力端子、第1および第2の入力端子から、同一の周波数を入力することが可能なダブルバランスミクサ21と、ダブルバランスミクサ21の第1および第2の入力端子にそれぞれ接続され、同一の周波数を出力する電圧制御発振器11,12と、電圧制御発振器11,12の位相が同相または逆相となるように制御する位相制御手段31とを備え、同一の周波数を出力する2つの電圧制御発振器11,12に0度または180度の位相差を与えてダブルバランスミクサ21に入力することで、3倍波を位相関係により抑圧して2倍波を出力することが可能となる。

(もっと読む)

PLL回路

【課題】高速かつ確実に低雑音特性を得ることができるPLL回路を得ることを目的とする。

【解決手段】相互に異なる移相量PS14,PS24,PS34がそれぞれ設定されており、N分周された発振信号の位相を設定されている移相量だけ変える移相器4−1〜4−3と、移相量の差分の関係が移相器4−1〜4−3のそれぞれに設定されている移相量の差分の関係と一致する条件の下で、相互に異なる移相量PS15,PS25,PS35がそれぞれ設定されており、R分周された基準信号Refの位相を設定されている移相量だけ変える移相器5−1〜5−3とを設ける。

(もっと読む)

電圧制御発振器及びそれを備えた無線通信装置

【課題】バイアス抵抗の抵抗値を大きい値に維持して省電力化及び発振効率の向上を図りつつ、広帯域の変調信号に対応することができる電圧制御発振器及びそれを備えた無線通信装置を提供すること。

【解決手段】

印加される電圧に応じて静電容量値が変化するバラクタM1,M2を有し、当該バラクタM1,M2に制御端子T2を介して印加される制御信号に応じて共振周波数が変化する共振回路30と、共振回路30と並列に接続された負性抵抗回路40とを備え、制御信号の逆相信号が制御端子T3を介して印加されるキャパシタC3、C4をバラクタM1,M2に接続した。

(もっと読む)

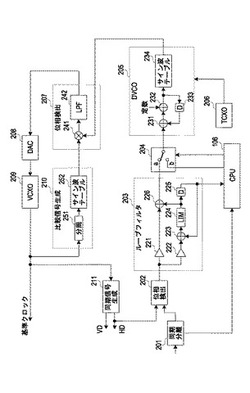

デジタルPLL回路とその制御方法

【課題】比較的簡易な回路構成で、制御時定数を短くしても超高安定な位相同期を実現する。

【解決手段】基準クロックを1/m分周器12で1/m倍し、VCXO11で発生される発振クロックを1/n分周器13で1/n倍し、両クロックを量子化位相比較器14に送り、両クロックのずれ量に相当する量子化位相差δを取得して予測制御器15に送る。予測制御器15では、入力された量子化位相差を、その極性が負から正に反転してから再び負に反転するまで、または正から負に反転してから再び正に反転するまで積分し、この積分値に-0.5倍〜-0.05倍の予測係数を掛けた値を予測重み値として求め、この予測重み値を積分値に加算して制御電圧値を予測する。この予測制御器15で予測された制御電圧値を、D/A変換器16でアナログ電圧に変換し、LPF17によって決まるループ時定数でフィルタリングして、周波数制御電圧としてVCXO11に送る。

(もっと読む)

半導体装置

【課題】デジタルDLL回路における消費電力を低減するとともに、ノイズによる電源電圧の変動の影響を軽減することが可能な半導体装置を提供すること。

【解決手段】デジタルDLL回路を備える半導体装置において、位相比較の間欠間隔を設定する間欠間隔設定回路を設ける。間欠間隔設定回路による間欠間隔の設定は、外部から入力される設定信号に基づいて制御する。これにより、ノイズによる電源電圧の変動の影響を軽減し、平均化された遅延素子の段数の調整が可能となる。

(もっと読む)

無線回路、集積回路装置及び電子機器

【課題】安定したデータ送信ができる無線回路、集積回路装置及び電子機器等を提供すること。

【解決手段】無線回路100は、電圧制御発振回路を有するPLL回路120を有し送信信号を生成して出力する送信信号生成回路110と、送信信号を増幅するパワーアンプ130と、周波数測定回路140とを含む。PLL回路120は、送信データ出力期間の前の期間ではクローズドループ動作に設定され、送信データ出力期間ではオープンループ動作に設定される。周波数測定回路140は、クローズドループ動作からオープンループ動作への切り換え時における送信信号の搬送波信号の周波数シフト量、及び送信データ出力期間における搬送波信号の周波数ドリフト量の少なくとも一方を測定する。

(もっと読む)

原子発振器

【課題】設計の自由度を向上させることにより比較的簡易な構成の原子発振器を提供すること。

【解決手段】原子発振器1は、光源10、光検出手段30、制御手段40を含む。光源10は、中心周波数をf1として周波数がΔfずつ異なる複数の周波数成分を有する第1の光と、中心周波数をf2として周波数がΔfずつ異なる複数の周波数成分を有する第2の光と、を発生させる。光検出手段30は、アルカリ金属原子を透過した第1の光及び第2の光を含む光の強度を検出する。制御手段40は、光検出手段30の検出結果に基づいて、第1の光の所定の周波数成分と第2の光の所定の周波数成分の周波数差がアルカリ金属原子の2つの基底準位のエネルギー差に相当する周波数に等しくなるように制御する。第1の光の中心周波数f1と第2の光の中心周波数f2の周波数差は、アルカリ金属原子の2つの基底準位のエネルギー差に相当する周波数と異なる。

(もっと読む)

信号処理装置

【課題】 ジッタの少ないクロックを発生させる

【解決手段】 第1の発振器と、前記第1の発振器から出力される第1のクロックの周波数とは異なる周波数の第2のクロックを出力する第2の発振器と、前記第1の発振器からの第1のクロックと前記第2の発振器からの第2のクロックのうちの一方を選択する選択手段と、前記選択手段により選択された第1のクロックまたは第2のクロックの周波数を逓倍し、出力クロックを生成する生成手段と、前記第1の発振器からの第1のクロックを逓倍する逓倍回路と、前記逓倍回路からの出力信号と前記生成手段からの出力クロックとの位相差を検出し、前記位相差を示す信号を前記第2の発振器に出力することにより前記第2の発振器からの第2のクロックの周波数を変更する位相検出手段とを備える。

(もっと読む)

送信回路、集積回路装置及び電子機器

【課題】安定したデータ送信ができる送信回路、集積回路装置及び電子機器等を提供すること。

【解決手段】送信回路100は、電圧制御発振回路190を有し、搬送波の信号を生成するPLL回路110と、送信データDTXに基づいて、電圧制御発振回路190の変調用制御電圧信号入力ノードNBに対して、変調用制御電圧信号VMを出力する変調用制御電圧生成回路120と、電圧制御発振回路190の出力信号を増幅するパワーアンプ210とを含む。変調用制御電圧生成回路120は、送信データ出力期間の前の擬似信号出力期間に、擬似制御電圧信号を変調用制御電圧信号VMとして出力する。

(もっと読む)

半導体集積回路装置

【課題】ノーマルなクロックとSSCとを生成するクロック発生回路における回路面積を低減しながら、高精度のSSCを生成する。

【解決手段】電圧制御発振器から出力されたクロック信号vco1は、分周器13によって分周され、分周クロックph0としてセレクタ15に出力される。分周器13は、制御回路12の制御信号Pconに基づいて、周期の1/mずつ位相のシフトした分周クロックph1〜phmを出力する。セレクタ15は、分周クロックph0〜phmのうち、最も近い位相シフトをもつ2つの分周クロックphj,phj+1を選択する。位相補間回路16は、制御回路12から出力される重み付けデータ信号Aに基づいて、分周クロックphj,phj+1間の位相差の間を更に細分化した位相シフト量で位相シフトさせ、出力クロックfout1として出力する。

(もっと読む)

周波数シンセサイザ

【課題】位相雑音を改善することのできる周波数シンセサイザを提供すること。

【解決手段】周波数設定部により設定された周波数の正弦波信号を設定信号出力部からディジタル信号として出力し、これをD/A変換する。ここから出力された正弦波信号と電圧制御発振部の出力周波数に対応する周波数の正弦波信号と、前記D/A変換部からの正弦波信号と、の差分を差動増幅器で増幅し、増幅された信号をA/D変換部を介して、既述の両正弦波信号の位相差を取り出す手段に入力する。この位相差を積分した信号に相当する電圧を電圧制御発振器に制御電圧として入力する。そして差動増幅器の利得をA/D変換部の位相雑音劣化の最大値よりも大きく設定し、これによりA/D変換部の位相雑音劣化をキャンセルする。

(もっと読む)

電流源、電子機器および集積回路

【課題】低電圧駆動において安定した定電流を供給する。

【解決手段】電流源1は、入力電流に応じた周波数の発振信号を出力する電流制御発振部11と、発振信号と基準信号とを比較する比較部13と、比較部13の比較結果に応じた電流を出力するチャージポンプ14と、チャージポンプ14の出力電流により充放電される平滑キャパシタ42を含むローパスフィルタ15と、平滑キャパシタ42に接続され、平滑キャパシタ42が生成する電圧に応じた電流を生成し、入力電流として電流制御発振部11へ供給するループ用変換部16と、ローパスフィルタ15に接続され、ローパスフィルタ15において生成される電圧に応じた電流を生成し、出力電流として出力する出力用変換部17とを有する。

(もっと読む)

PLL回路

【課題】低電圧動作が可能なPLL回路を提供する。

【解決手段】フィルタ用キャパシタの一端が入力される電圧制御発振器と、前記電圧制御発振器の出力が入力され、フィードバック信号を出力するn分周器と、基準信号と前記フィードバック信号との位相差に応じた電圧パルスを出力する位相周波数比較器と、前記電圧パルスに基づき、前記フィルタ用キャパシタを充放電するチャージポンプとを備え、前記チャージポンプは、前記フィルタ用キャパシタの一端に接続される充放電用容量を備える。

(もっと読む)

モータ用位相同期回路及びそれを用いたスピンドルモータ

【課題】入力信号の周波数が変化するようなモータの駆動制御において、ステップ入力などのように入力信号の位相が急激に変化した場合でも、オーバーシュートやスリップによる振動などの過渡的な振動の発生を抑制することができる多重PLL回路の構成を得る。

【解決手段】第2PLL21の第2位相比較回路24によって検出される位相差が所定範囲外である場合には、ループ加算器26を介さずに、第1PLL11を用いて第2PLL21のモータ部22を制御する一方、上記位相差が所定範囲内である場合には、上記ループ加算器26を介して上記第1PLL11と上記第2PLL21とを接続して多重PLL回路を構成するように、信号経路切換部33によって、該第1及び第2PLL11,12の信号経路を切り換える。

(もっと読む)

半導体装置

【課題】搭載された異なるPLL回路の夫々の出力信号の同期化を実現する半導体装置を提供する。

【解決手段】所定の周波数の信号を入力し、当該入力信号の整数倍の周波数の信号を当該入力信号と同期させて出力する、2つの異なるPLL回路(2、4)によって同期化された信号を夫々分周し、当該分周した信号の位相差に応じた所定の遅延量に基づいて一方のPLL回路(2)の出力信号を遅延させることで、他方のPLL回路(4)の出力信号(42)に同期させたクロック信号(41)を生成する。

(もっと読む)

デジタル位相同期回路

【課題】ホールドオーバ期間中の温度特性と経年変化に対する影響を抑え、周波数の高安定性を維持するホールドオーバ機能を有するデジタル位相同期回路を得る。

【解決手段】電圧制御型クロック発振手段の周辺の温度を測定する温度測定手段と、同期対象と同期している間、デジタルフィルタ手段からの出力で電圧制御型クロック発振手段を制御するとともにデジタルフィルタ手段からの出力と電圧制御型クロック発振手段の周辺の温度、経過時問の履歴から経過時間と電圧制御型クロック発振手段の周辺の温度と項に持つ2元多項式を求め、同期対象と同期していない間、同期対象に同期しなくなってからの経過時間および電圧制御型クロック発振手段の周辺の温度から2元多項式で電圧制御型クロック発振手段を制御する制御信号を推定するとともに推定した制御信号で電圧制御型クロック発振手段を制御するホールドオーバ手段と、を有する。

(もっと読む)

クロックリカバリ回路およびデータ再生回路

【課題】クロックジッタを低減可能なクロックリカバリ回路およびデータ再生回路を提供する。

【解決手段】シリアル入力信号を第1のクロック信号に同期させてサンプリングしたサンプリングデータを出力するサンプラ13、サンプリングデータに基づき、第1のクロック信号とシリアル入力信号のクロックとの位相関係を表すシリアル位相情報信号を出力する位相比較回路14、シリルア位相情報信号を第2のクロック信号に同期させてシリアルパラレル変換したパラレル位相情報信号を出力するシリアルパラレル変換回路17、パラレル位相情報信号に基づき、位相偏差信号と位相遅進信号を演算するデジタルフィルタ回路16、位相偏差信号と位相遅進信号とに基づいて生成した位相制御信号を第2のクロック信号より高速の第3のクロック信号に同期して出力する位相制御量処理回路20および、位相制御信号に基づき、外部から入力する基準クロック信号の位相を調整した第1のクロック信号を出力する位相補間回路12を備える。

(もっと読む)

クロック生成回路及びこれを備える半導体装置並びにデータ処理システム

【課題】クロック生成回路の消費電力を低減する。

【解決手段】内部クロック信号LCLKを生成するディレイライン110と、ディレイライン110を制御することによって内部クロック信号LCLKの位相を調整する位相制御部120と、位相制御部120の動作モードを切り替えるモード切り替え回路130とを備える。位相制御部120は、サンプリングクロック信号SYNCLK2に同期して内部クロック信号LCLKの位相を変化させる第1の動作モードと、内部クロック信号LCLKの位相を固定させる第2の動作モードを有しており、モード切り替え回路130は、リフレッシュ信号REFBなどのトリガ信号に応答して位相制御部120を第1の動作モードに遷移させ、内部クロック信号LCLKが所望の位相に達したことに応答して位相制御部120を第2の動作モードに遷移させる。

(もっと読む)

発振回路

【課題】 本発明は、出力信号の発振周波数の精度を向上させることができる発振回路を提供することを目的とする。

【解決手段】 圧電素子の周波数温度特性を補償するための補償電圧S150を生成する補償電圧生成部160と、制御電圧S130に補償電圧S150を加算することにより、補正制御電圧S160を生成する加算部150と、補正制御電圧S160に基づいて、発振周波数を変化させることにより、所望の発振周波数を有する出力信号S170を生成し出力する電圧制御発振部220とを備える。

(もっと読む)

141 - 160 / 713

[ Back to top ]