Fターム[5J106CC52]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 周波数変換回路 (1,116) | 分周回路 (990)

Fターム[5J106CC52]の下位に属するFターム

可変分周回路 (277)

Fターム[5J106CC52]に分類される特許

161 - 180 / 713

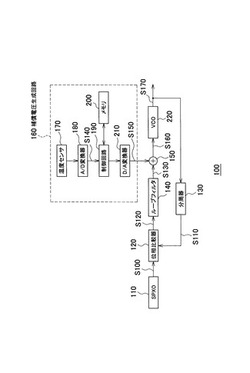

発振回路

【課題】 本発明は、出力信号の発振周波数の精度を向上させることができる発振回路を提供することを目的とする。

【解決手段】 圧電素子の周波数温度特性を補償するための補償電圧S150を生成する補償電圧生成部160と、制御電圧S130に補償電圧S150を加算することにより、補正制御電圧S160を生成する加算部150と、補正制御電圧S160に基づいて、発振周波数を変化させることにより、所望の発振周波数を有する出力信号S170を生成し出力する電圧制御発振部220とを備える。

(もっと読む)

PLL回路

【課題】拡散周波数が未知の拡散信号から拡散周波数成分を除去できるPLL回路を提供する。

【解決手段】一の信号の位相と他の信号の位相との差分に応じた差分信号を出力する位相比較器1、差分信号に応じた電流信号を生成するチャージポンプ回路2、電流信号を平滑化して信号n1を生成するループフィルタ9、信号n1をフィルタリングして信号n2、n5を生成するノッチフィルタ5、信号n1の位相と信号n2の位相との差分に基づいて、ノッチフィルタ5によって遮断される遮断周波数を調整する遮断周波数調整回路6、信号n5に基づいて所定の周波数の信号を発振する電圧制御発振回路3によってPLL回路を構成する。ノッチフィルタ5は、ループフィルタ9によって遮断される周波数よりも低い周波数の範囲に上限値と下限値が含まれる所定の範囲の周波数を遮断する。

(もっと読む)

2分周インジェクションロックリング発振器回路

【解決手段】周波数分周器は、複数のインジェクションロックリング発振器(ILRO)を含む。第1ILROは、クロスカップルされたNチャネルトランジスタの対、負荷抵抗の対、インテグレイトキャパシタ、及び電流注入回路を含む。各トランジスタのドレインは、他方のトランジスタのゲートに結合される。各負荷抵抗は、各トランジスタのドレインを回路電圧源に結合する。インテグレイトキャパシタは、各トランジスタのソースに結合する。電流注入回路は、第1周波数の発振入力信号に応答して、各トランジスタのソースから回路グランドへのパスを交互にオープン及びクローズする。これに応答して、各トランジスタのドレインの電圧状態は交互にラッチ及びトグルされて、2分周された発振信号の差動対が生成される。逆位相で駆動される第1及び第2ILROは、位相直交する2つの差動出力信号を生成する。 (もっと読む)

チャージポンプ回路及びそれを用いるPLL回路

【課題】電流供給および吸入用の定電流源と、それらの定電流源の間に設けられる2つの直列に接続されたスイッチ素子から成り第1の出力端子を持つ主出力側電流路と、同様に2つのスイッチ素子から成り第2の出力端子を持つ副出力側電流路とを備え、位相比較器からの駆動信号に応答して、主出力側電流路のスイッチと副出力側電流路との各スイッチ素子が開閉し、第1の出力端子から正負の電流パルスが出力される差動スイッチング方式のチャージポンプ回路において、ダイ面積を縮小するとともに、消費電力を削減する。

【解決手段】主出力側電流路のスイッチ素子Q7,Q8間の電位と副出力側電流路のスイッチ素子Q5,Q6間の電位との差に起因して定電流源Q3,Q4の寄生容量の充放電に伴い発生する緩慢なグリッチを補償するために、コンパレータ37と、ラッチ回路38と、コンデンサC1と、充放電器Q9,Q10とを用いてグリッチ補償回路36を構成する。

(もっと読む)

PLL回路

【課題】 エージング特性を自動補正し、外部基準信号の未接続又はアンロック時に出力周波数変動を小さくできるPLL回路を提供する。

【解決手段】 基準信号が適正範囲内でロック状態の場合に、初期調整時に、チャージポンプ出力電圧(A)の初期電圧を温度情報Tと共に読み取り、自走周波数設定用電圧(B)が電圧(A)となるようのDAコンバータ又はPWM出力回路9の設定値を調整し、温度特性初期テーブルを生成し、運用中に、温度情報Tにおける電圧(A)の最新電圧に対応する設定値を、温度特性初期テーブルを参照して特定し、初期電圧と最新電圧の設定値の差分で当該テーブルをオフセット補正して自走用温度補正テーブルを生成し、アンロック状態等になると特定された設定値による自走周波数設定用電圧(B)で自走するPLL回路である。

(もっと読む)

同期および追跡動作モードを有する位相同期ループシステム

【課題】同期モードと追跡動作モードを有する位相同期ループ(PLL)システム。

【解決手段】PLLは、所望の周波数で信号を出力する電圧制御発振器(VCO)を含む。位相検波器がVCOからの出力に結合されている。位相検波器は、VCOからの信号出力の位相を基準信号の位相と比較する。ループフィルタ601がVCOと位相検波器とに結合されている。ループフィルタ601はスイッチ603を含む。スイッチ603が垂直な位置に設定されるとき、VCO信号の位相を基準信号の位相に同期させるために、ループフィルタ601は同期動作モードとなる。スイッチ603を水平な位置に設定することにより、ループフィルタを追跡動作モードに置くことができ、追跡動作モードはVCO信号の位相を調整して、基準信号の位相を追跡する。

(もっと読む)

受信部及び局側装置並びにクロック・データ再生回路における周波数校正方法

【課題】電圧制御型発振器を用いた受信部等において、温度補償用に容量素子を増やすことなく、温度変化による電圧制御型発振器の周波数特性を補償する。

【解決手段】本発明の受信部/局側装置は、受信信号からクロック信号及びデータ信号を再生するクロック・データ再生回路11を含むものであって、クロック・データ再生回路11に含まれる電圧制御型発振器17の発振周波数を校正する校正器16と、信号受信のスケジュールを管理する機能を有し、クロック信号及びデータ信号を再生すべき受信信号(上り信号)が無い状態の持続時間が校正器16による校正の所要時間を満たす時を選んで校正器16に対してリセット信号(校正指令信号)を出力する管理部104とを備えたものである。

(もっと読む)

スペクトラム拡散クロックジェネレータ、回路装置、画像読取装置、画像形成装置、及びスペクトラム拡散クロック生成方法

【課題】周波数変調幅を高精度に合わせることができるようにする。

【解決手段】入力クロックとフィードバッククロックとの位相差を検出する位相比較器2と、位相比較器2からの位相差信号に応じて電流を供給するチャージポンプ3と、チャージポンプ3の出力を電圧に変換し、平滑化するループフィルタ4と、入力電圧に応じた周波数のクロックを発生させる電圧制御発振器6と、変調幅設定値に応じた振幅を持つ変調信号を生成する変調生成部8とを有し、ループフィルタ4の出力と変調生成部8から出力される変調信号とを加算した信号を電圧制御発振器6に印加し、スペクトラム拡散クロックを生成する際、電圧制御発振器6で生成されたスペクトル拡散クロックの変調幅を検出し、検出した変調幅と変調幅目標値を比較し、その差分を小さくするように新たに算出した変調幅設定値を変調生成部8にフィードバックする変調幅検出部10を備えた。

(もっと読む)

クロックデータリカバリ回路及び表示装置

【課題】クロックデータリカバリにおいて擬似ロック発生の検出に要する時間を短縮すること。

【解決手段】クロックデータリカバリ回路は、レシーバ回路と、PLL回路と、擬似ロック検出回路とを備える。レシーバ回路は、所定のパターンを含むシリアルデータを受け取り、クロック信号に同期してシリアルデータをサンプリングしてサンプルドデータを生成する。PLL回路は、サンプルドデータに基づいてクロックデータリカバリを行い、クロック信号を生成する。ここで、擬似ロックパターンとは、PLL回路の擬似ロックが発生している場合にレシーバ回路が上記所定のパターンをサンプリングする結果得られるパターンである。擬似ロック検出回路は、サンプルドデータに含まれる擬似ロックパターンを検出することによって、PLL回路の擬似ロックを検出する。

(もっと読む)

抵抗値調整回路

【課題】LSI内部の抵抗素子の抵抗値を精度よく且つ適時に較正する。

【解決手段】

複数の抵抗素子を有する半導体集積回路に設けられる抵抗値調整回路は、前記複数の抵抗素子のうち第1の抵抗素子に基準電圧を印加して第1の抵抗素子の抵抗値に反比例する定電流を生成し、前記半導体集積回路の外部のコンデンサに前記定電流を供給する定電流源と、前記コンデンサに前記定電流が供給されるときに、前記コンデンサの電圧が所定電圧上昇する時間を計測する充電時間計測部と、予め設定された基準充電時間と前記計測された計測充電時間の差分に基づいて前記複数の抵抗素子のうち第2の抵抗素子の抵抗値を較正するキャリブレーション部を有する。LSI外部のコンデンサは容量が既知であり、LSIの製造プロセスのばらつきに依存しないので、基準充電時間と計測充電時間の差分に基づいて、精度よく抵抗値を較正できる。

(もっと読む)

PLL回路

【課題】位相比較周波数を高く保ち、PLLの位相雑音を改善し、出力信号の精度を向上させたPLL回路を提供する。

【解決手段】基準信号をクロックとして動作し所定範囲内でサイクリックにクロックが入力する度に予め設定された値を累積加算した基準信号の位相に相当する信号を出力する第1位相アキュムレータ1、発振器の出力信号をクロックとして動作し所定範囲内でサイクリックにクロックが入力する度に予め設定された値を累積加算した発振器の出力信号の位相に相当する信号を出力する第2位相アキュムレータ2、第1及び第2位相アキュムレータの出力信号を比較して差を求め基準信号と発振器の出力信号との位相差を示す出力信号を出力する位相比較器3、位相比較器の出力信号に従って発振器への制御信号を生成する制御部4、制御部からの制御信号に応じた周波数の信号を出力する上記発振器5を有す。

(もっと読む)

送信機および通信システム

【課題】周波数の変化に対応でき、且つクロストークに起因するジッターの低減を図ることができる送信機、および通信システムを提供する。

【解決手段】送信機2は、発振回路4と、送信部5とを備える。発振回路4は、基準クロックCKrefを入力して、同一の周期を有すると共に位相が互いに異なるN相(Nは2以上の整数)のクロックCK1〜CKNを生成して出力する。送信部5は、発振回路4から出力されたクロックCK1〜CKNを入力して、このクロックCKn(nは1以上N以下の各整数)にシリアルデータ信号Snを同期させて高速シリアル伝送線路Lnを介して受信機3に送信する。

(もっと読む)

発振周波数制御回路

【課題】 自己の周波数を補正し、自走した時にも発振周波数を安定に保ち、更に外部からの固定電圧を可変にした制御電圧で発振できる発振周波数制御回路を提供する。

【解決手段】 電圧制御発振器15と、分周器16と、位相比較器12と、ループフィルタ14と、検波回路17と、PWM回路22と、メモリ21と、制御電圧可変回路26と、位相比較器12とループフィルタ14との接続をオン/オフすると共に制御電圧可変回路26からの制御電圧を選択出力する選択スイッチ13と、当該制御電圧選択の指示で当該制御電圧を優先的に選択出力し、当該指示がない場合に検波回路17で検出された外部基準信号のレベルが適正範囲内であれば選択スイッチ13をオンとし、レベルが適正範囲外であれば選択スイッチ13をオフとしてメモリ21に記憶されたパルス生成の情報をPWM回路22に出力するCPU20とを有する。

(もっと読む)

半導体集積回路装置

【課題】プロセスモニタに必要な回路面積を増加させることなく、高精度なプロセスキャリブレーションを短時間で行う。

【解決手段】ディジタル制御発振器38が任意の発振バンドを選択した後、制御部25はTDC41の信号がプロセスモニタ制御部40に入力されるようにスイッチ44を切り換える。TDC41は、信号VREFの立ち上がりエッジと最も近い信号VPREの立ち上がりエッジの期間をディジタル値に、信号VREFの立ち上がりエッジと2番目に近い信号VPREの立ち上がりエッジの期間をディジタル値に変換し、その差を算出する。プロセスモニタ制御部40は、ルックアップテーブルを参照し、算出した値と予め設定されている期待値とを比較し、プロセス値を決定する。そのプロセス値は、プロセス信号として調整制御部26にそれぞれ出力され、プロセスキャリブレーションが行われる。

(もっと読む)

信号発生装置および試験装置

【課題】ループ帯域より高い周波数のジッタを印加する。

【解決手段】指定された位相の出力信号を発生する信号発生装置であって、所定周期の基準信号と出力信号との位相差に応じた制御信号を出力する位相差検出部と、制御信号の高域成分を除去するループフィルタと、ループフィルタにより高域成分が除去された制御信号に応じた周波数の周期信号を発生する発振部と、指定された位相分、周期信号に対して位相がシフトされた出力信号を出力する位相シフト部と、を備える信号発生装置を提供する。

(もっと読む)

PLL回路

【課題】基準周波数信号がPLL回路に入力されなくなった場合に、チャージポンプ回路にループフィルタから電流が流れ続けることを防止する。

【解決手段】PLL回路1は、入力された電圧に応じた周波数のVCO信号を出力するVCO20と、入力された電流に応じた電圧をVCO20に与えるループフィルタ18と、第一入力信号と第二入力信号との位相差に応じた幅の位相差パルスを出力する位相比較器14と、位相差パルスを受けて、ループフィルタ18への電流入力を行うチャージポンプ回路16と、REF信号(基準周波数信号)が入力されていない無入力状態において、チャージポンプ回路16への位相差パルスの入力を停止させる位相差パルス停止部30とを備える。なお、第一入力信号は、REF信号自身又はそれを分周した信号であり、第二入力信号は、VCO信号自身又はそれを分周した信号である。

(もっと読む)

PLL周波数シンセサイザ

【課題】電圧制御発振器のゲイン特性の変動を抑制する。

【解決手段】電圧制御発振器11は、インダクタ100と、微調整コンデンサ101pと、粗調整コンデンサ102pとを含み、発振クロックCKoutを生成する。分周器12は、発振クロックCKoutを分周して分周クロックCKdivを生成する。直流電圧供給回路13は、粗調整モードにおいて、直流電圧V13を制御ノードNiに供給するとともに発振電圧VPの直流値に応じて直流電圧V13の電圧値を変化させる。周波数帯域選択回路14は、粗調整モードにおいて、電圧制御発振器11の発振周波数帯域が目標周波数に対応する発振周波数帯域に設定されるように、基準クロックと分周クロックとの周波数差に基づいて粗調整コンデンサ102pの容量値を切り替える。発振制御回路15は、微調整モードにおいて、基準クロックと分周クロックとの位相差に応じて制御電圧VTを増減させる。

(もっと読む)

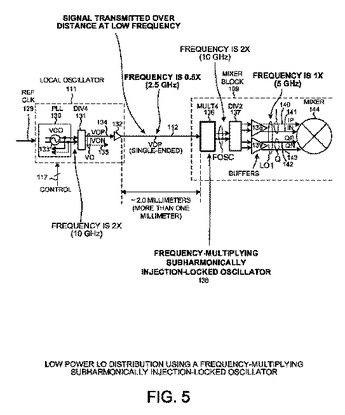

周波数逓倍サブハーモニック注入同期発振器を使用した低電力LO分配

局部発振器は、相対的に低い周波数の信号を、集積回路にわたりミキサの位置まで伝達する。ミキサの近くでは、周波数逓倍サブハーモニック注入同期発振器(SHILO)が、その信号を受信し、それからより高い周波数の信号を発生させる。SHILOがIおよびQ直交位相信号を出力する場合には、IおよびQ信号がミキサをドライブする。SHILOが直交位相信号を発生させない場合には、直交位相発生回路が、SHILO出力信号を受信し、それからミキサをドライブするIおよびQ信号を発生させる。1つの有利な態様において、局部発振器からSHILOまでの距離を越えて伝達される信号の周波数は、近くでミキサをドライブするIおよびQ信号の周波数よりも低い。距離を越えて伝達される信号の周波数を低くすることは、従来のシステムと比較すると、50パーセント以上、LO信号分配システムの電力消費を減じることができる。  (もっと読む)

(もっと読む)

発振器及び位相同期回路

【課題】十分に高い周波数帯域において、広帯域にわたって柔軟に発振周波数を調整すること。

【解決手段】信号線131は、電源から直流電圧Vdcが印加されると、電源に接続された始端を節とし、終端を腹とする4分の3波長の定在波を発生させる。ストリップ132−1〜132−nは、それぞれスイッチ133−1〜133−nを介してグランド層に接続されている。スイッチ133−1〜133−nは、切替制御部140による制御に従って、それぞれストリップ132−1〜132−nとグランド層との接続及び非接続を切り替える。スイッチ133−1〜133−nの接続及び非接続を切り替えることにより、擬似的に信号線131とグランド層の間の距離が調節され、伝送線路部130における実効誘電率が変化して、定在波の周波数を調整することができる。

(もっと読む)

発振器

【課題】 位相雑音特性を劣化させることなく可変周波数帯域の広帯域化を図ることができる発振器を提供する。

【解決手段】 可変周波数帯域の異なる複数の電圧制御発振器(15a、15b)と、複数の電圧制御発振器からの出力のいずれかを選択出力する切替器16と、パラメータに基づいて発振器出力が所定の周波数となるよう制御するデジタルPLL回路13とを備え、制御部18が、各電圧制御発振器に対応して、良好な位相雑音特性が得られるループゲイン及びダンピングファクタを記憶しておき、外部から周波数の値が入力されると、入力された周波数の値に応じて電圧制御発振器を選択し、当該電圧制御発振器からの出力を選択出力するよう切替器16を切り替え、当該電圧制御発振器に対応して記憶されているループゲイン及びダンピングファクタをパラメータとしてデジタルPLL回路13に設定する発振器としている。

(もっと読む)

161 - 180 / 713

[ Back to top ]