Fターム[5J106CC53]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 周波数変換回路 (1,116) | 分周回路 (990) | 可変分周回路 (277)

Fターム[5J106CC53]に分類される特許

201 - 220 / 277

PLL回路

【課題】 複数種類の異なった記録モードで記録するための記録信号が入力され、入力信号に含まれる雑音成分を取り除いた純度の高い信号を出力するPLL回路を実現する。

【解決手段】 入力信号を1/Lにして第1分周器41から第1周波数信号を出力し、入力信号に対応するマスタクロック信号を発振器46aで発振し、マスタクロック信号の周波数を1/Mにして第2周波数信号を第2分周器52から出力し、第1周波数信号と第2周波数信号との位相差信号を位相比較器43から出力し、第1周波数信号と第2周波数信号とが一致しているか否かをロック検出器44で検出し、一致しない場合には第1分周器のL及び第2分周器のMを可変させ、一致した場合にはL及びMを固定させる制御信号を制御回路48から出力し、マスタクロック信号を1/Nにして真の信号成分を第3分周器から出力するようにしたPLL回路を構成した。

(もっと読む)

トリガ信号発生装置

【課題】入力信号に同期し、ジッタの少ないトリガ信号を生成するトリガ信号発生装置を実現することにある。

【解決手段】入力される入力信号よりも低い周波数のトリガ信号を出力するトリガ信号発生装置に改良を加えたものである。本装置は、入力信号を分周する分周回路と、この分周回路で分周された信号を入力信号に同期させる同期化手段を有する同期化回路とを設けたことを特徴とするものである。

(もっと読む)

フェーズ・ロックド・ループのための改良されたロック検出回路

【課題】フェーズ・ロックド・ループ(PLL)のロック状態を決定する改良されたシステム及び方法を提供する。

【解決手段】ロック検出回路は、ロックの瞬間的喪失を検出するため用いられる高速ロック検出信号を発生する。ロック検出回路はまた、基準クロックとフィードバック・クロックとの位相のミスアライメントを検出するための位相アライメント検出回路を含む。更に、ロック検出回路は、基準クロック信号が検出されたかどうかを検出するための基準クロック検出回路を含み得る。全ての上記の回路からの出力信号は、増強されたロック検出信号を生成するために、論理回路へ通信される。拡張されたロック検出信号も論理回路へ通信される。

(もっと読む)

クロック生成回路、およびそれを搭載した電子機器

【課題】 第1クロックおよびそのクロックとの比率情報を所定の伝送規格にしたがい受信して、送信側で利用されている第2クロックを受信側で再生する場合にて、第2クロックの周波数を一意に求めることができない場合がある。

【解決手段】 プリスケーラ22は、電圧制御発振器20の出力クロックを所定の分周比で分周する。位相比較器14は、送信側から受信した第1クロックおよび第1比率情報をもとに生成した基準クロックと、プリスケーラ22の出力クロックおよび送信側から受信した第2比率情報をもとに生成した帰還クロックとを比較して、それらの誤差を打ち消すための制御信号を電圧制御発振器20に供給する。探索回路66は、電圧制御発振器20の発振周波数が所定期間経過してもロックしないとき、プリスケーラ22の分周比を変更して、発振周波数がロックする分周比を探索する。

(もっと読む)

発振器、PLL回路および受信機、送信機

【課題】 回路規模を縮小することができるとともに集積化に適した発振器、PLL回路および受信機、送信機を提供すること。

【解決手段】 可変容量回路230、230Aの静電容量を可変することによって電圧制御型発振器21の発振周波数が変更される。可変容量回路230は、制御信号によって静電容量が連続的に変更可能な複数の可変容量素子60〜64と、可変容量素子のそれぞれに対応しており静電容量が固定の複数のコンデンサ50〜54と、可変容量素子とこれに対応するコンデンサとからなる組合せ回路を一組として複数の可変容量素子60〜64と複数のコンデンサ50〜54のそれぞれの選択的な接続の有無を組合せ回路を単位として切り替える複数のスイッチ71〜74、81〜84とを備えている。

(もっと読む)

クロック生成回路、およびそれを搭載した電子機器

【課題】 音声帯域内の周波数に対応する周期で送信されてくる情報を利用して、送信側で利用されているクロックを再生するとき、音質を低下させる場合がある。

【解決手段】 第1分周器110は、所定の伝送規格にしたがい受信したビデオクロックを同様に受信した比率情報を用いて分周し、基準クロックを生成する。位相比較器120は、基準クロックと本クロック生成回路100の出力を起点とする帰還クロックとを比較し、それらの誤差を打ち消すための制御信号を出力する。電圧制御発振器140は、制御信号に応じた発振周波数でクロックを出力する。第2分周器150は、電圧制御発振器140の出力クロックを比率情報を用いて分周し、分周したクロックを位相比較器120に入力する。位相比較器120の基準クロックは、音声帯域外の周波数に設定される。

(もっと読む)

半導体集積回路

【課題】 トリミングを行わずに電圧制御発振回路の発振周波数を調整すること。制御回路の面積を抑え、調整誤差の少ない発振回路を内蔵した半導体集積回路を提供すること。

【解決手段】 電圧制御発振回路(VCO)の周波数を調整する可変容量素子を、プロセスや素子のばらつき調整用可変容量素子群と、周波数選択用可変容量素子群との2系統に分離して調整を行い、可変容量素子の切り替えスイッチの数と回路面積の増大を小さくする。調整誤差については、調整期待値との差分を記憶素子で記憶し、その差分値が最小となる容量素子値を求めることにより影響を最小限に押さえることが可能となる。

(もっと読む)

スペクトラム拡散発振回路

【課題】 ジッタを発生させることなくクロック信号をスペクトラム拡散させる。

【解決手段】 スペクトラム拡散発振回路10は、発生させた基準クロック信号を発生する基準発振器12とPLL回路14とを備えている。PLL回路14の可変分周器28は、拡散制御部18によって分周比が周期的に変化させられ、電圧制御発振器26の出力したクロック信号の周波数を分周して位相比較器22に入力する。位相比較器22は、基準発振器12の出力した基準クロック信号と可変分周器28の出力したクロック信号との位相差を求めて位相差信号を出力する。ループフィルタ24は、位相比較器22の出力した位相差信号に基づいた制御電圧を電圧制御発振器26に入力する。電圧制御発振器26は、制御電圧に応じた周波数のクロック信号を出力する。電圧制御発振器26の出力したクロック信号は、帯域フィルタ16を通過し、増幅器20によって増幅されて、外部に出力される。

(もっと読む)

広範囲かつダイナミックに再構成可能なクロックデータ回復アーキテクチャ

【課題】広範囲のデータレートに渡って動作可能なCDRアーキテクチャを提供する。

【解決手段】広範囲およびダイナミックにリプログラミング可能なCDRアークテクチャは、広範囲の動作周波数でシリアル入力データから埋め込まれたクロック信号を回復する。広範囲のデータレートをサポートするために、CDRアーキテクチャは、複数の動作パラメータを含む。これらのパラメータは、様々な先行/後行の分割器設定、チャージポンプ電流、ループフィルタおよび帯域幅選択、および、VCOギアを含む。パラメータは、回路またはPLDのパワーダウンなしに、ダイナミックにリプログラミングされ得る。これは、CDR回路が、様々な規格とプロトコルとの間を迅速に切り替えることを可能にする。

(もっと読む)

スペクトル拡散クロック発生器を自動的に補正する方法と装置

【課題】位相ロックループ回路内の受動素子値およびシステム利得およびチャージポンプ電流の変動を自動的に補正するスペクトル拡散クロック発生器回路を提供する。

【解決手段】位相周波数検出器122のUPおよびDOWN信号124、126のパルス幅を特定の間隔で監視し、標準パルス幅持続時間と比較して、これらのUPおよびDOWN信号124、126の偏差誤差を判別する。パルス幅持続時間の実際の値で誤差を測定した後、誤差信号の大きさと方向に応じて位相ロックループ回路100を調整する。位相ロックループ利得パラメータ、特に電圧制御発振器134の利得およびチャージポンプ電流に変化があると、位相周波数検出器122の出力に著しい影響が出て、スペクトル拡散プロファイルに沿って周波数が変化するときにUPおよびDOWN信号124、126の幅が変動する。

(もっと読む)

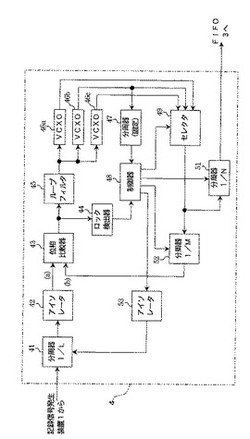

自動周波数制御ループ回路

【課題】高い精密度を有しながら周波数を広帯域で発振させることができる自動周波数制御ループ回路を提供すること。

【解決手段】基準周波数を発生させるクロック発振部と、基準周波数を第1分周比で分周する第1分周器、発振周波数を第2分周比で分周する第2分周器、第1分周器によって分周された第1分周周波数と第2分周器によって分周された第2分周周波数との間の位相差を検出する位相検出器、位相差に対応して発振周波数を発生させる電圧制御発振器と、入力周波数と発振周波数に対応して出力周波数を出力する周波数変換器を含む周波数合成部と、出力周波数を設定周波数と比較して誤差を検出する誤差検出器、誤差を積分する積分器と、積分器の積分値に対応する制御信号を計算する演算器を含む復調部とを含み、制御信号に応じて第1分周比及び第2分周比を変更して誤差を補正することを特徴とする。

(もっと読む)

電圧制御型発振回路およびPLL回路

【課題】 簡易な構成でリングVCOの発振波形の歪みおよび位相ノイズ・ジッタ性能を向上させる。

【解決手段】 等価回路10は、負荷R1、R2およびNMOSトランジスタM1、M2で構成される差動増幅部11(VCOセルC1)と、負荷R3、R4およびNMOSトランジスタM3、M4で構成される差動増幅部12(VCOセルC3)と、NMOSトランジスタM1、M2、M3、M4のソースと、定電流を出力する定電流源Iとを備えている。また、tailノードNは、NMOSトランジスタM1、M2、M3、M4のソースと定電流源Iとの接続部を構成している。

(もっと読む)

PLL回路およびICチップ

【課題】非接触ICチップに設けられる発振器の周波数を上げることなく、通信の転送レートを上げることができるようにする。

【解決手段】外部からの制御信号に従ってφの値が変更され、cosφで表される発振出力信号と、sinφで表される発振出力信号が可変型発振器71から出力される。可変型発振器71から出力された信号の掛け算、加算等が行われ、信号sin(ωt+φ)と、それを基準としてπ/2だけ位相がずれた信号である信号cos(ωt+φ)が出力される。この出力に基づいて、いまの、クロック信号との位相差などが判断され、位相差に応じた制御信号が可変型発振器71に供給されてくる。本発明は、非接触ICチップに搭載されるPLLに適用することができる。

(もっと読む)

PLL周波数シンセサイザ、半導体集積回路および通信装置

【課題】 消費電力を低減することが可能な、動作の安定性が高いPLL周波数シンセサイザ、半導体集積回路および通信装置を提供する。

【解決手段】 可変分周器は、複数段のD−FF21,22,23,・・・で構成される。D−FF21において、スイッチ回路SW1〜SW5がオフ状態のとき、トランジスタTr1,Tr3によってバイアス電流I1,I3が流れる。スイッチ回路SW1〜SW5がオン状態のとき、トランジスタTr1〜Tr4によってバイアス電流I1〜I4が流れる。また、Q端子36およびQX端子37から出力される信号の電圧振幅は、常に(Ibias×RL)/2となる。したがって、可変分周器の消費電力を低減することが可能になる。

(もっと読む)

音声処理装置

【課題】

インターフェースを介して伝送された音声データを再生する音声処理装置において、回路規模を増大させずに、伝送された音声信号を再生するための種々のオーディオクロック信号を、短いロック時間で生成できるようにする。

【解決手段】

音声情報検出部110によって、HDMI規格におけるASPと呼ばれるパケットから音声信号の周波数情報が抽出され、音声情報として分周器120に出力される。分周器120により前記音声情報に基づいて分数比が決定され、アナログPLL回路130が出力するPLLクロック信号が前記分周比で分周されて、比較クロック信号として出力される。アナログPLL回路130では、前記比較クロック信号と基準クロック信号とが同期するようにフィードバック制御が行われ、前記基準クロック信号が逓倍または分周されたオーディオクロック信号が生成される。

(もっと読む)

集積回路、再生装置及び再生方法

【課題】 本発明は、集積回路、再生装置及び再生方法に関し、例えば非接触型のICカードシステムに適用して、クロックの周波数がばらついた状態で、デューティー比が50〔%〕から変化した場合でも、正しくデータを再生することができるようにする。

【解決手段】 本発明は、ペイロードの部分に比して速く収束するようにPLL回路の動作を切り換えて、90度位相の異なる基準信号の一方を入力信号に位相同期させるようにこれら基準信号を位相制御し、他方の基準信号が入力信号に位相同期したとの位相比較結果が得られた場合に、直前の制御を継続する。

(もっと読む)

適合性の基準周波数補正による同期方式

本発明は、同期情報に対する出力信号の同期を提供するための装置および方法に関する。同期は、信号生成手段、例えば位相ロックループ装置(30)または直接デジタル合成装置をその正確な周波数へと制御する補正制御情報を、未補正の基準周波数を正しいすなわち正確な基準周波数に変換する周波数変換ユニット(90)に結合することを提供することにより達成される。これにより、信号生成手段(30)向けの未補正の基準周波数を、どのような周波数制御のための手段も持たない簡素な水晶発振器(2)によって供給することができる。信号生成手段(30)および周波数変換ユニット(90)の設定は、ユーザ装置がその基準周波数を、通信ネットワークによって発せられた同期情報に対して同期することを可能にする、所定のシーケンスで行うことができる。  (もっと読む)

(もっと読む)

PLL回路

【課題】 安価且つ簡単な回路構成で、ループフィルタのカットオフ周波数を制御電圧に応じて変化させることが可能なPLL回路を提供することを目的とする

【解決手段】 本発明に係るPLL回路は、制御電圧Vcに応じた周波数の発振信号を出力する電圧制御発振器と、基準信号と発振信号に応じた帰還信号との間の位相差を表す位相差信号を出力する位相比較器と、位相差信号に応じた電流を出力するチャージポンプ回路3と、チャージポンプ回路3の出力電流により制御電圧Vcを変化させるループフィルタ4と、を備えている。ループフィルタ4は、PINダイオードD1を有し、そのPINダイオードD1を用いてループフィルタ4のカットオフ周波数が変化するように構成されている。

(もっと読む)

クロック生成回路

【課題】

周波数変調を行うクロック生成回路において、意図に即した周波数変調を行うことが困難であった。

【解決手段】

基準クロックおよびフィードバッククロックが入力される位相比較器と、位相比較器の出力に基づいて動作クロックを生成する電流制御発振器と、動作クロックを分周率設定信号に基づいた分周率で分周してフィードバッククロックとする分周回路と、動作クロックを計数し、当該計数結果に基づいて電流制御発振器の制御電流を設定する制御電流設定信号および分周率設定信号を出力する制御回路とを有するクロック生成回路。

(もっと読む)

通信装置

【課題】 ロックアップタイムの短縮と、受信品質の向上と、を両立すること。

【解決手段】 PLL回路10を用いて受信信号の周波数変換を行う通信装置1において、PLL回路10の次数を変更する次数変更手段と、周波数変換後の受信信号の品質を示す品質情報を取得する品質情報取得手段と、を含み、前記次数変更手段は、前記品質情報により示される品質が所定条件を満たすように、前記次数を変更する、ことを特徴とする。

(もっと読む)

201 - 220 / 277

[ Back to top ]