Fターム[5J106CC53]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 周波数変換回路 (1,116) | 分周回路 (990) | 可変分周回路 (277)

Fターム[5J106CC53]に分類される特許

21 - 40 / 277

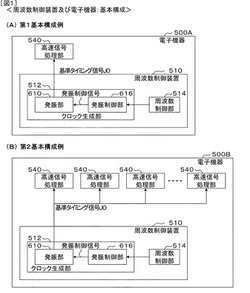

周波数制御装置、周波数制御方法、クロック生成回路、電子機器、及び、プログラム

【課題】クロック生成回路におけるハンチング現象を抑制することのできる新たな技術を提供する。

【解決手段】電子機器500は、周波数制御装置510と信号処理部540とを備える。周波数制御装置510は、出力クロック信号を生成するクロック生成回路(クロック生成部512)と、出力クロック信号の周波数を制御する周波数制御部514とを備える。クロック生成部512は、入力された発振制御信号に基づき出力クロック信号を生成する出力クロック生成部(発振部610)と、発振制御信号を生成して出力クロック生成部に供給する発振制御部616とを有する。周波数制御部514は、発振制御部616を制御して発振制御信号を徐々に変化させることにより、出力クロック信号の周波数を徐々に変化させる。

(もっと読む)

PLL回路および半導体装置

【課題】 PLL回路の発振精度の低下を抑制しつつ、ロックアップタイムを短縮する。

【解決手段】 PLL回路は、制御電圧に応じた周波数の出力信号を生成する電圧制御発振器と、出力信号を分周する分周器と、基準信号と分周された出力信号との位相差を検出し、位相差に応じて第1検出信号および第2検出信号を生成する位相比較器と、第1検出信号に基づいてオン/オフが制御される第1スイッチおよび第2検出信号に基づいてオン/オフが制御される第2スイッチを含み、制御電圧を調整するチャージポンプ回路と、チャージポンプ回路により充放電される容量素子を含み、チャージポンプ回路の出力を平滑化して制御電圧を生成するローパスフィルタと、電圧制御発振器に初期電圧を与える初期設定期間に、第1スイッチおよび第2スイッチの少なくとも一方をオンし、容量素子の充放電を制御することにより、制御電圧を初期電圧に設定する電圧供給部とを有している。

(もっと読む)

デルタシグマ変調型分数分周PLL周波数シンセサイザおよびそれを備えた無線通信装置

【課題】デルタシグマ変調型分数分周PLL周波数シンセサイザにおいて、スプリアスを抑制し、さらに、位相雑音特性を良好に保つ。

【解決手段】分周器(25)を変調することで分数分周を行うデルタシグマ変調型分数分周PLL周波数シンセサイザは、分数部データKに加算すべきシフト量Sを求め、シフト量Sと、シフト後分数部データK2とをそれぞれ出力する演算処理手段(27)と、シフト後分数部データK2を積分して量子化する第1のデルタシグマ変調器(28)と、シフト量Sを積分して量子化する第2のデルタシグマ変調器(29)と、第1のデルタシグマ変調器(28)の出力系列と第2のデルタシグマ変調器(29)の符号反転出力とを加算する第1の加算器(30)と、整数部データMと第1の加算器(30)の出力とを加算する第2の加算器(31)とを備え、第2の加算器(31)の出力により分周器(25)を変調させる。

(もっと読む)

クロック周波数制御回路及びクロック周波数制御方法

【課題】 信号の分周比を比較的少なくし、また位相雑音の増加も抑圧した上で微少な周波数変化した信号を生成するPLL回路を実現する。

【解決手段】 本発明は、所定の電圧を加減することにより出力周波数を制御する相関回路入力される電圧に応じて出力周波数が変化する電圧制御発振器と、電圧制御発振器の出力を分周する第1の分周回路と、外部から入力される基準周波数を分周する第2の分周回路と、第1の分周回路と前記第2の分周回路との出力の位相に応じたパルスを出力する位相比較器と、位相比較器の出力から低周波成分を抽出し、電圧制御発生器に入力するローパスフィルタとを有する。

(もっと読む)

小数点分周PLL回路および集積回路

【課題】ループフィルタのカットオフ周波数を低く設定することなく、スプリアスを抑制する。

【解決手段】基準発振器で生成された基準周波数を所定の基準クロックに分周する第1の分周器103と、電圧制御発振器で生成された発振周波数を所定の帰還クロックに小数点分周する第2の分周器105と、基準クロックと帰還クロックとの位相を比較する位相比較器106と、位相比較器106による比較結果に基づいて電圧制御発振器の発振周波数を制御するチャージポンプ107と、を備えた小数点分周PLL回路1において、第1の分周器103側の電源パッド1−2と、第2の分周器105側の電源パッド1−1と、位相比較器106側の電源パッド1−3と、チャージポンプ107側の電源パッド1−4とを、それぞれ別個に備える。

(もっと読む)

位相比較器

【課題】位相比較器において、2つのフリップ・フロップの出力信号がリセットされるまでの遅延時間によって両出力信号に現れる余分な成分を取り除き、それによって生じる種々の問題を解決すること。

【解決手段】本発明の位相比較器は、比較対象の2つの入力信号が入力されて第1と第2の出力信号を出力する第1と第2のフリップ・フロップと、第1と第2の出力信号を論理積処理してリセット信号を出力する論理積処理回路と、論理積処理回路と同じ遅延時間を持ち第1遅延信号と第2遅延信号を出力する第1と第2の遅延手段と、第1遅延信号と第2遅延信号がそれぞれ入力されるとともにリセット信号によってリセットされて第3と第4の出力信号を出力する第3と第4のフリップ・フロップとを備え、位相が進んだ方の入力信号を遅延させた第1もしくは第2遅延信号が入力される第3もしくは第4のフリップ・フロップの出力信号に位相比較出力信号が出力さるように構成されている。

(もっと読む)

無線通信装置

【課題】周波数シンセサイザによる周波数信号を用いる無線通信装置の消費電力を低減する。

【解決手段】受信部が、受信した無線信号に基づく信号と周波数信号とを混合する第1ミキサと、当該第1ミキサの出力とローカル信号とを混合する第2ミキサと、当該第2ミキサの出力を復調して復調信号を生成する復調段とを含み、周波数シンセサイザが、制御入力電圧の変動に応じた周波数の周波数信号を生成するVCOと、当該VCOの出力周波数信号を分周して得られた信号と基準クロック信号との位相差に応じた電圧を制御入力電圧とするフィードバック回路と、からなり、当該VCOは、バイアス電流が大となるほど高い周波数で動作可能となる可変周波数発振器であって、当該バイアス電流が当該モード指定に応じて制御される無線通信装置。

(もっと読む)

無線通信機

【課題】信号発生器の周波数設定データを複数の箇所から設定する際に、複雑なスイッチを設けることなく、周波数設定データの衝突を防止し、また、より狭い周波数偏差の要求に応える。

【解決手段】無線通信機100は、PLL回路144を構成するPLLIC128と、PLLICに出力周波数を設定する第1のデータを出力し、少なくとも、PLLICへのアクセス不実行状態と、アクセス待機状態と、アクセス実行状態との3つの状態を遷移するCPU112と、出力周波数を増加もしくは減少させるためPLLICに設定する第2のデータを出力し、少なくとも、PLLICのアクセス可能状態と、アクセス禁止状態との2つの状態を遷移するDSP118とを備え、CPUとDSPとが第1の信号と第2の信号によって互いに状態遷移に関する情報を交換し、PLLICへのアクセスの衝突を防止する。

(もっと読む)

PLL回路

【課題】周波数やロックアップ時間が変動したり、PLL特性が劣化したりするのを抑えることのできるPLL回路を提供する。

【解決手段】演算器15a,15bは、出力信号の目標の周波数を示す目標周波数設定値が変化した時、フラクショナル分周器17に対して目標周波数設定値で示される周波数と異なる周波数を示す周波数設定値を複数回設定する。そして、演算器15a,15bが周波数設定値を複数回設定した後に、演算器15a,15bから出力される周波数設定値は、目標周波数設定値と同じ値になる。これにより、周波数の引き込み動作時に、アナログスイッチング素子を用いてループフィルタの切り替えを行う必要がないため、スイッチング切り替え時に発生するノイズや、切り替え前後のループフィルタに生じる電圧差によって、発振器にノイズが発生することがない。

(もっと読む)

無線通信のためのディジタル送信機

【課題】改善された性能、低電力消費、低コストのディジタル送信機を提供する。

【解決手段】デカルト座標−極座標変換器230で、受信したデカルト座標から極座標への変換を行う。FIRフィルタ234(または、デルタ−シグマ変調器)により、前記極座標の振幅情報からエンベロープ信号を生成し、位相変調PLL250、VCOにより、前記極座標の位相情報から位相変調された信号を生成する。複数状態増幅器274(または、排他的論理和ゲート)により、前記のエンベロープ信号および位相変調された信号に基づいて、ディジタル変調された信号を生成する。電力増幅器280は、前記のディジタル変調された信号を増幅して、RF出力信号を生成する。

(もっと読む)

分周回路およびそれを備えたPLL回路並びに半導体集積回路

【課題】回路規模および消費電力を増大させることなく、回路全体の分周比の可変範囲をより拡大することのできる分周回路を実現する。

【解決手段】周期信号(s5)を2種類の分周比で分周して第1の分周信号(c1)を出力する可変分周器(2)と、第1の分周信号(c1)のサイクル数のカウント値(c2)を出力し、リセットされるとカウント動作を初期値から再開するカウンタ回路(3)と、カウント値(c2)が比較基準値(a)と一致する度にHighとLowとを反転させたパルス信号(s1)を、第2の分周信号として出力するとともに分周比の切替信号として可変分周器(2)に供給し、カウント値(c2)が比較基準値(a)と一致する度にカウンタ回路(3)にリセット信号(r)を出力する比較器(4)と、比較器(4)に比較基準値(a)を供給する制御回路(5)とを備えている。

(もっと読む)

デジタルPLL回路、情報再生装置、ディスク再生装置および信号処理方法

【課題】複数の倍速に対応できることを前提に、再生性能を落とすことなくトータルの回路規模および消費電力が小さく、しかもループ遅延が小さい安定なPLLを提供する。

【解決手段】A/D変換器は入力チャネルレートに依存せず高速なサンプリングを行い、ダウンコンバータにより必要なチャネルレートに落とす。これにより倍速数に依存せずにAAFの特性を単一化できるためアナログ回路を小型化できる。また、デジタル位相追従部は補間型完全デジタル位相追従構成とすることでループ遅延を最小化できる。一方、CAV再生時には入力レートに応じてタウンコンバータのデシメーション比Mを変更することでデジタル回路の動作クロックが必要以上に上がることを押さえ消費電力増加を防ぐ。デシメーション比Mの切り替え時はデジタル回路内部遅延を考慮してデジタル位相追従部の内部周波数切り替えタイミングを遅らせることで位相周りのないシームレスな切り替えを実現する。

(もっと読む)

フェーズロックドループの方法及び装置

【課題】2点変調を採用するフェーズロックドループを用いた通信システムを提供する。

【解決手段】フェーズロックドループは、位相検出器106の第1の入力に動作可能に接続された出力を有する主発振器100、位相検出器106の第2の入力に動作可能に接続された出力を有する従発振器102、及び位相検出器106の生誤り端末に動作可能に接続されたフォワード利得適応モジュールを含む。フォワード利得適応モジュールは、位相検出器106の生誤り端末と動作可能に接続された、フォワード利得適応モジュールの可変利得増幅器200と、前記フォワード利得適応モジュールの可変利得増幅器200と前記従発振器102とに動作可能に接続された、フォワード利得適応モジュールの積分器202とを具備する。

(もっと読む)

クロック発生回路

【課題】 PLLを動作させた状態で、同期外れを起させず、入力クロックの切り替えおよびそれに伴う分周比の切り替えを行うことが可能なクロック発生回路を提供する。

【解決手段】 タイミング制御部8は、入力クロックを指定するクロック選択情報が切り替わった後、分周器1がリファレンスクロックCLKREFを出力するのに応じて、クロック選択指令SELCKを切り替える動作と、分周器1に1個のリファレンスクロックCLKREFを出力させるための入力クロックの個数Rと、分周器6に1個のフィードバッククロックCLKFBを出力させるための出力クロックCLKOの個数Fのうちの少なくとも一方の設定を切り替え、切り替え後の設定個数Rに対応した入力クロックの分周器1によるカウント動作および切り替え後の設定個数Fに対応した出力クロックの分周器6によるカウント動作の両方を開始させる。

(もっと読む)

PLL周波数シンセサイザ、無線通信装置およびPLL周波数シンセサイザの制御方法

【課題】安価な構成とするとともに、性能を向上させることができるPLL周波数シンセサイザ、無線通信装置およびPLL周波数シンセサイザの制御方法を提供する。

【解決手段】PLL周波数シンセサイザは、基準周波数信号と分周信号との位相を比較する位相比較部101からの信号と位相誤差補償信号とに応じて、電流パルス信号を生成するCPDAC102と、電流パルス信号を電圧信号に変換するループフィルタ103と、電圧信号に応じた発振周波数の信号を出力するVCO104と、VCO104からの出力を分周して分周信号として出力する分周器105と、分数分周のための分周比のデータに基づいて、分周比制御信号を生成するデルタシグマ変調器107および加算器106と、分周比のデータから少なくとも2つの位相誤差補償用のデータを生成し、生成したデータを異なるタイミングで利用して、位相誤差補償信号を生成する制御部108とを備える。

(もっと読む)

周波数シンセサイザ装置及び変調周波数変位調整方法

【課題】2つの変調経路を有する周波数シンセサイザ装置において、DACから電圧制御発振器に出力される制御電圧の振幅を適切に調整することができる。

【解決手段】周波数シンセサイザ装置10は、入力電圧に応じた発振周波数で発振する電圧制御発振器14、電圧制御発振器14からの信号を分周するプログラマブル分周器20、分周信号と基準クロックとの位相差を電圧制御発振器14に出力する周波数位相比較器22、送信データに応じて目標周波数変位分周波数を変位させる場合の調整電圧を電圧制御発振器14に出力するDAC12、調整電圧の校正時に、電圧制御発振器14を基準電圧電源に接続するスイッチ32、任意の送信データをDAC12に出力して発振させた状態で分周信号の周波数をカウントしたカウント値に基づいて、目標周波数変位に対応する調整電圧に対応した調整データを設定する変調周波数変位校正回路30を備える。

(もっと読む)

位相同期ループ回路および位相同期ループ回路の制御方法

【課題】チップサイズの増大を抑え、広帯域の発振周波数帯域を有するPLL回路等を提供する。

【解決手段】VCO34は、制御電圧VTに応じた発振周波数fVCOを有する出力クロック信号CLKOを生成する。PLLブロック2は、制御電圧VTを生成する。ロック検出器24は、発振周波数fVCOが設定周波数fSにロックされているか否かを検出する。VT電圧検出部31は、バラクタVA1ないしVA3のうちの何れを選択するかを決定する。セレクタ部32は、出力クロック信号CLKOの粗調整段階においてはバラクタVA0を選択する。また、粗調整段階においてロック検出された旨をロック検出器24から受信することに応じて、微調整段階へ移行する。微調整段階においては、移行時点におけるVT電圧検出部31によって選択されていたバラクタの選択を維持する。

(もっと読む)

原子発振器

【課題】PLL回路の回路構成を単純化することが可能となり、調整箇所の削減と低消費

電力化を実現した原子発振器を提供する。

【解決手段】この原子発振器40のPLL回路4は、VCXO2の出力周波数を1/Rに

分周する1/R分周器5と、VCXO2に同期したマイクロ波周波数を生成する電圧制御

発振器6と、VCO6から出力されるマイクロ波周波数を分周する1/Mプリスケーラ7

と、1/Mプリスケーラ7の出力周波数をK/Lに分周するK/L分周器8と、1/R分

周器5の出力とK/L分周器8の出力との位相差を出力する位相比較器9と、位相比較器

9の出力に基づいて直流分を取り出すLPF10と、を備えて構成されている。

(もっと読む)

周波数シンセサイザ

【課題】

応答性が高く維持され、かつハードウェアの構成が簡略化されるにもかかわらず、各部の変動やバラツキに対して安定に適応できる周波数シンセサイザを提供する。

【解決手段】

位相同期ループが供給する制御情報に対応した所望の周波数で出力信号を生成する可変周波発振器を有し、前記所望の周波数となり得る目標周波数毎に、前期可変周波発振器に与えられるべき制御情報の初期値が予め登録されたテーブルと、前記所望の周波数が切り替えられたときに、前記位相同期ループの応答を規制し、かつ最新の所望の周波数に対応して前期テーブルに登録されている初期値を前記可変周波発振器に供給する初期値設定手段と、前記位相同期ループのロックアップを前記位相差に基づいて検出するロックアップ検出手段と、前記ロックアップが検出されたときに、前記応答の規制を解除し、かつ前記初期値設定手段による初期値の供給を規制する位相同期再開手段とを備える。

(もっと読む)

スペクトラム拡散クロック生成回路及びその制御方法

【課題】変調度が安定しない。

【解決手段】周波数変調した出力発振信号を出力するPLL回路を有するスペクトラム拡散信号生成回路であって、前記PLL回路は、入力した発振制御信号の値に応じた周波数で前記出力発振信号を出力する発振回路を備え、前記PLL回路によりフィードバックされたPLL信号の周波数を変調させる前記発振制御信号を生成し、この前記発振制御信号の最大値と最小値をモニタし、そのモニタ結果により前記発振制御信号の最大値と最小値を調整し、前記出力発振信号の変調度を所定の値に制御する周波数変調部を、有するスペクトラム拡散クロック生成回路。

(もっと読む)

21 - 40 / 277

[ Back to top ]