Fターム[5J106CC53]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 周波数変換回路 (1,116) | 分周回路 (990) | 可変分周回路 (277)

Fターム[5J106CC53]に分類される特許

41 - 60 / 277

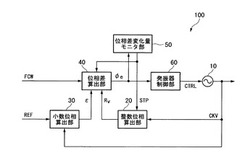

デジタルPLL

【課題】位相差情報をデジタル値で出力するデジタルPLLにおいて、消費電力を抑えたデジタルPLLを提供することにある。

【解決手段】デジタルPLL100は、発振器10、整数位相算出部20、小数位相算出部30、位相差算出部40、位相差変化量モニタ部50、および発振器制御部60を有する。PLLにおいては発振器の出力周波数が、分周比により設定された所望の周波数に近づく、即ちロック状態に近づくにつれ位相差の変化量は減少していくことから、位相差変化量モニタ部50にて位相差の変化量をモニタし、変化量が整数位相算出部20の1LSB未満である「1」未満になった時点で整数位相算出部20におけるカウンタ動作を停止する。

(もっと読む)

位相調整回路及び位相調整方法

【課題】消費電力を低減し、かつ回路面積も小さい位相調整回路を提供すること

【解決手段】位相調整回路100は、複数の遅延素子回路121〜124をリング状に結合したVCO120を有するPLL発振回路100を備える。また位相調整回路100は遅延素子回路を所望の遅延量に応じた数(125〜127)だけ有し、入力信号に前記所望の遅延量を与える位相遅延回路200、210を備える。PLL発振回路100は基準クロックの入力に応じた基準信号に、基準信号の所定周期分の遅延を与えた発振信号をVCO120において生成する。PLL発振回路100は、基準信号と、発振信号に応じた信号と、が略同位相となるように算出された遅延量に応じた遅延制御信号を遅延素子回路121〜124、及び遅延素子回路125〜127の各々に対して入力する。

(もっと読む)

クロック信号生成装置及び電子装置

【課題】目標周波数が変更されても、生成するクロック信号の周波数を短時間で目標周波数に一致させるクロック信号生成装置、及び、電子装置を提供することを目的とする。

【解決手段】第1制御部は、設定された目標周波数が第1の目標周波数から第2の目標周波数に変更されると、第1の所定のタイミングで、第1設定数として第3の数よりも小さい第5の数を前記第1カウンタに設定するとともに、第2設定数として第4の数よりも小さい第6の数を前記第2カウンタに設定し、第1の所定のタイミングの後の第2の所定のタイミングで、第3の数を前記第1カウンタに設定するとともに、前記第4の数を前記第2カウンタに設定する。

(もっと読む)

位相同期回路及びその制御方法

【課題】従来技術の位相同期回路では、入力クロックの切り替え時において、安定した出力クロックを生成することができないという問題があった。

【解決手段】本発明にかかる位相同期回路は、入力クロックを選択するセレクタ3と、入力クロックを分周する1/m分周器4と、フィードバッククロックを分周する1/n分周器5と、位相差検出器と、電圧保持回路30を有する電圧制御発振器10と、電圧保持回路31を有する電圧制御発振器11と、電圧制御発振器10,11のうちいずれかの出力を出力クロックとして出力するセレクタ13と、電圧制御発振器10,11のうちいずれかの出力をフィードバッククロックとして出力するセレクタ12と、備え、保持モードの電圧制御発振器が出力クロックfoutを生成し、通常モードの電圧制御発振器がフィードバッククロックを生成している場合に、入力クロックの切り替えが行われる。

(もっと読む)

位相同期ループ回路、半導体集積回路、電子機器、位相同期ループ回路の制御方法

【課題】位相同期ループ回路において、制御応答の改善や消費電力の低減を図る。

【解決手段】発振器制御部255と分周器制御部257は、発振制御信号と分周制御信号が、引込み過程およびロック時の双方において、ループフィルタ電圧に基づいて比例関係を持って連動して変化するようにする。発振部210と分周部220が引込み過程およびロック時の双方において連動した動作をする。引込み過程およびロック時の双方における任意のループフィルタ電圧に対応する分周部220の最高動作周波数が発振部210の発振出力信号の周波数よりも常に高くなるように各制御信号の関係を設定する。ロック時の分周制御信号は、引込み過程における発振部210の発振出力信号の最高周波数と対応するループフィルタ信号に基づくバイアス電流よりも小さなバイアス電流を分周部220に自動的に設定するようになる。このことにより、ロック時の電力消費を低減できる。

(もっと読む)

半導体集積回路及びそれを用いた電子機器

【課題】低速ディジタル回路において発生するノイズがアナログ回路に与える影響を小さくし、回路ブロック毎のレイアウト変更を容易にする。

【解決手段】半導体集積回路は、(a)第1及び第2のVCOと、第1及び第2のVCOによって生成される信号を分周する第1及び第2の分周回路と、2つの分周信号の内の一方を選択する選択回路と、選択された分周信号に基づいて制御電圧を生成する制御電圧生成回路とを含むアナログ回路ブロックと、(b)変復調回路を含む第1のディジタル回路ブロックと、(c)制御回路を含む第2のディジタル回路ブロックとを備え、アナログ回路ブロックが、基板の第1及び第2の辺に沿って配置され、第2のディジタル回路ブロックが、基板の第3及び第4の辺に沿って配置され、第1のディジタル回路ブロックが、アナログ回路ブロックと第2のディジタル回路ブロックとの間に配置されている。

(もっと読む)

PLL回路

【課題】 ノイズ特性を劣化させることなく、消費電力を抑えて信頼性を向上できるPLL回路を提供する。

【解決手段】 VCO1からの出力周波数Foutを分周して基準信号との位相を比較して位相差を制御電圧としてVCO1に帰還させるPLL IC2を備え、制御回路6が、基準周波数FrefとDDS回路5における出力周波数Fddsの双方の周波数を細かく設定可能とし、両者の組み合わせによって、Fref及びその逓倍周波数に対するFddsの折り返し信号をDDS回路5で生成し、第1のAMP7で増幅し、可変フィルタ8によって所望のFdds(desired)を選択し、第2のAMP9で増幅して基準信号としてPLL IC2に供給し、制御回路6が、分周比NもPLL IC2に供給するPLL回路である。

(もっと読む)

半導体集積回路

【課題】複数の無線通信チャンネルについて、PLL回路全体の動作特性に基づいて電圧制御発振器の精密なキャリブレーションを行う。

【解決手段】半導体集積回路は、高周波信号を生成する電圧制御発振器を含むPLL回路と、電圧制御発振器のトランジスタに選択的に負荷される複数のキャパシタと、複数の無線通信チャンネルについて電圧制御発振器の発振周波数を補正するためのキャパシタに関する情報を格納する格納部と、キャリブレーションモードにおいて、複数の無線通信チャンネルについてPLL回路のループ特性を測定することにより補正用キャパシタに関する情報を格納部に格納し、通常動作モードにおいて、選択された無線通信チャンネルに従って、格納部に格納されている情報を読み出すことにより補正用キャパシタを決定するキャリブレーション回路とを具備する。

(もっと読む)

基準周波数信号源

【課題】大幅なハードウエア変更を必要とすることなく、異なる基準信号に対応可能な基準周波数信号源を得る。

【解決手段】基準信号と基準信号の周波数fiに応じた制御信号Cとに基づいてクロック信号および局部発振信号を生成する周波数変換回路10と、クロック信号に同期して、周波数制御データに応じた周波数信号を生成するDDS2と、DDS2からの周波数信号に含まれる不要波成分を抑圧するフィルタ3と、局部発振信号と電圧制御発振器の出力信号とを周波数混合するミクサ8と、ミクサ8からの混合信号に含まれる不要波成分を抑圧するフィルタ9と、フィルタ3を介した周波数信号とフィルタ9を介した混合信号との位相差を検出する位相比較器5と、位相比較器5からの位相差信号を濾波するループフィルタ6と、ループフィルタ6を介した位相差信号に応じて出力信号を生成する電圧制御発振器7とを備える。

(もっと読む)

PLLロック検出回路、及びPLLロック検出回路を有するPLLシンセサイザ回路

【課題】適切にPLL回路ロックがなされているか否かを検出する。

【解決手段】PLL回路ロックがなされているか否かを検出するPLLロック検出回路を構築する。ここにおいて、そのPLLロック検出回路は、基準発振器から供給される基準発振周波数を示す基準発振周波数信号と、前記基準発振周波数を分周して得られたリファレンス周波数を示し位相比較器に供給されるリファレンス周波数信号と、VCOから供給される電圧制御発振周波数を分周して得られた比較周波数を示し前記位相比較器に供給される比較周波数信号とを受ける、そして、前記リファレンス周波数信号と前記比較周波数信号とに基づいて、前記PLL回路ロックを示すロック検出信号を出力する。

(もっと読む)

PLL発振回路

【課題】 アンロック状態を検査すると共に、自動的に再同期する自動リトライ機能を備えるPLL発振回路を提供する。

【解決手段】 MPU4は、外部基準信号とVCXO3からの出力信号の位相を比較してVCXO3への制御電圧を出力するPLL−IC1からのロック検出信号を入力し、ロック状態においてアンロック状態にするためのアンロックアラームテスト用データをPLL−IC1に設定し、PLL−IC1からのロック検出信号によりアンロック状態を判定すると、外部にアンロックアラーム出力信号を出力し、アンロック状態が第1の期間継続しているか否かを判定し、アンロック状態が第1の期間継続していれば、再同期を行わせるためのデータをPLL−IC1に設定するリトライを実行するPLL発振回路である。

(もっと読む)

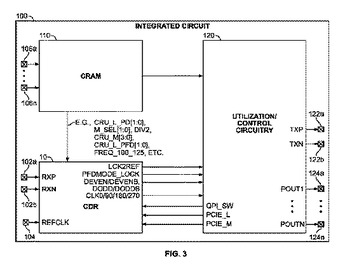

オートスピードネゴシエーションおよび他の可能な特徴を有するクロック・データ再生回路

集積回路(「IC」)は、入力データ信号からデータ情報を再生するためのクロック・データ再生(「CDR」)回路を含んでもよい。CDR回路は、参照クロックループと、データループとを含んでもよい。CDR回路によって出力される時刻変更(再生)データ信号は、その信号に含有される通信変更要求について、IC上の他の制御回路によって監視される。そのような要求に応答して、制御回路は、CDR回路の動作パラメータ(例えば、上述のループのうちのいずれか一方で使用される周波数分割ファクター)を変更することができる。これは、オートスピードネゴシエーションを採用するICサポート通信プロトコルに役立つことができる。  (もっと読む)

(もっと読む)

プログラマブルロジックデバイス回路に結合されるクロックデータリカバリ回路

【課題】プログラマブルロジックデバイス上またはこれと結合して設けられるクロックデータリカバリ回路の提供

【解決手段】プログラマブルロジックデバイス(“PLD”)が多数のCDRシグナリングプロトコルのうちの任意のものによって交信することを可能にするため、このPLDにプログラマブルクロックデータ復元(“CDR”)回路を装備する。CDR回路は、PLD内に内蔵するか、完全あるいは部分的に独立した集積回路とすることができる。この回路は、CDR入力、CDR出力、またはそれらの両方を行うことができる。CDR機能は、例えば非CDR低電圧作動シグナリング(“LVDS”)等のその他の非CDRシグナリング機能と組合わせて提供することができる。この回路は、大規模なシステムの一部とすることができる。

(もっと読む)

PLL回路および通信装置

【課題】出力周波数を切り替えた際の追従性の悪化を抑止すること。

【解決手段】分周部2は、基準信号と出力信号との位相を同期させるための信号である帰還信号を所定の分周比に分周する。そして、位相比較部3は、出力信号を用いて基準信号および帰還信号の位相を比較することで、分周部2が分周した分周比の増減に追従して、出力信号を生成するための位相比較部出力のゲインが増減する。濾波部4は、位相比較部3によって生成されたアナログ信号を濾波する。出力信号発振部5は、濾波部4によって濾波されたアナログ信号に基づいて、出力信号を生成する。

(もっと読む)

ADPLL回路、半導体装置及び携帯情報機器

【課題】ADPLL環境下またはADPLL環境に近い環境下において、ABSの精度向上手段を提供し、ABSの処理時間短縮を実現する。

【解決手段】ABS103中のデジタル周波数比較器103−1に、DPFD102の出力するDPE信号の初期位相差を格納するDFFを用意する。ABS動作開始直後に、DPFD102が出力するDPE信号はDPFD102の内部回路の初期位相差を表すものであるとしてDFFに記録する。以後デジタル周波数比較器103−1は入力されるDPE信号からDFFに記録された初期位相誤差を引いたものでABSを行い、高速かつ安定したABS動作の実現を図る。

(もっと読む)

スペクトラムアナライザおよびスペクトラム分析方法

【課題】フラクショナルスプリアスに起因するスペクトル波形の表示を阻止しつつ、迅速な測定を可能にする。

【解決手段】指定されたスパン(分析対象周波数範囲)の幅値が境界値より大きい場合、基準信号周波数を所定の基準値に設定し、RBW(分解能帯域幅)より狭いループフィルタ帯域を選択することによってフラクショナルスプリアスをRBWの内側にしてスペクトラム波形として表示されないようにする。また、指定されたスパンの幅値が境界値より小さい場合、基準信号周波数を基準値から所定値シフトさせ、そのシフト量と分周比の整数部との積に等しい分だけVCO出力信号の主信号成分とフラクショナルスプリアスとの周波数差を拡大させ、その拡大した周波数差より狭い範囲でループフィルタの帯域をRBWが含まれる領域に応じて設定してフラクショナルスプリアスのレベルを抑圧する。

(もっと読む)

クロック信号生成装置、電子装置、及び、PLL(PhaseLockedLoop)制御装置

【課題】所定のクロック信号の周波数を短時間で変更するとともに、クロック信号の周波数の変更時にクロック信号の供給先の動作が不安定になることを防止又は軽減するクロック信号生成装置等を提供する。

【解決手段】クロック信号生成装置等は、目標周波数が変更されると、第1制御部の代わりに、予め設定されている期間内に予め設定されている間隔かつ予め設定されている変更値で、クロック信号生成部に印加する電圧を順次変更し、クロック信号生成部が新たに生成するクロック信号の周波数を目標周波数に近づかせる第2制御部を備える。

(もっと読む)

冗長PLL回路

【課題】本線系と冗長系との間に生じる出力位相の偏差を抑圧し、出力切替時に出力位相の変化を抑える。

【解決手段】基準クロックによるリファレンス信号から1/n(nは任意の自然数)倍の第1の周波数信号を生成する1/n分周器11と、それぞれVCXO121,131の出力信号から1/m(mは任意の自然数)倍の第2の周波数信号を生成して1/n分周器11で生成される第1の周波数信号と位相比較し、その位相比較結果に基づいてVCXO121,131の出力周波数を制御するPLL回路部11,12と、PLL回路部11,12の出力を選択的に導出する出力選択スイッチ14とを具備する。

(もっと読む)

周波数シンセサイザ

【課題】設計が容易で、かつノイズ特性を良好にする。

【解決手段】周波数foutの出力信号Soutを生成するVCO5、周波数f1の低周波信号S1を生成する低周波信号生成部3、周波数f2の高周波信号S2を生成する高周波信号生成部4、ミキサ部6、ミキシング信号Smix中の差周波数信号Sdiを通過させる低域フィルタ部7、比較用信号S4を出力する信号処理部10、位相比較部8およびループフィルタ9を備え、信号処理部10は、周波数f2が新たに設定された際に、fout<f2のときには比較用信号S4の出力を停止し、fout≧f2で、かつ差周波数信号Sdiの絶対周波数fdiが低域フィルタ部7のカットオフ周波数fco以上のときには周波数f3(>f1)の基準信号S3を比較用信号S4として出力し、fout≧f2で、かつfdi<fcoのときには差周波数信号Sdiを比較用信号S4として出力する。

(もっと読む)

周波数測定回路及びそれを有するPLLシンセサイザ

【課題】

被測定クロックの周期または周波数を高精度に計測する周波数計測回路を提供する。

【解決手段】

周波数測定回路は,被測定クロックの被測定エッジをカウントするカウンタと,基準クロックの基準エッジに応答して,前記カウンタのカウント値を記憶するカウンタラッチ回路と,直列に接続された複数の基本遅延回路を有し,前記被測定クロックを初段の前記基本遅延回路に入力して伝搬させる遅延回路と,前記基準エッジに応答して,前記遅延回路の複数の基本遅延回路の出力をそれぞれラッチする複数の遅延ラッチ回路と,前記遅延ラッチ回路がラッチした前記複数の基本遅延回路の出力に基づいて,前記被測定クロックの前記被測定エッジの前記遅延回路内での位置を検出するエッジ検出回路と,2つの基準エッジ間の前記カウント値と,前記2つの基準エッジでの前記第1のエッジ検出回路が検出する前記被測定エッジの位置情報とから,前記被測定クロックの周期または周波数を演算する演算器とを有する。

(もっと読む)

41 - 60 / 277

[ Back to top ]