Fターム[5J106CC53]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 周波数変換回路 (1,116) | 分周回路 (990) | 可変分周回路 (277)

Fターム[5J106CC53]に分類される特許

61 - 80 / 277

位相ロックループ回路

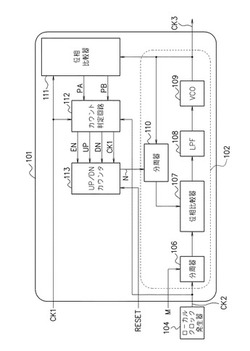

【課題】ローカルクロック信号に同期し、入力クロック信号に基づく周波数の出力クロック信号を出力することができる位相ロックループ回路を提供することを課題とする。

【解決手段】ローカルクロック信号及び第1のクロック信号の位相を比較する第1の位相比較器(107)と、第1の位相比較器により出力される信号の電圧に応じた周波数の出力クロック信号を出力する電圧制御発振器(109)と、電圧制御発振器により出力される出力クロック信号を分周し、その分周した出力クロック信号を第1のクロック信号として第1の位相比較器に出力する第1の分周器(110)と、入力クロック信号及び電圧制御発振器により出力される出力クロック信号の位相を比較する第2の位相比較器(111)と、第2の位相比較器により出力される信号に応じて第1の分周器の分周比を制御する制御部(112,113)とを有する位相ロックループ回路が提供される。

(もっと読む)

送受信装置およびその動作方法

【課題】半導体チップ面積を低減して再生データと再生クロックの生成の誤動作の可能性を軽減する。

【解決手段】送受信装置7は、クロックデータリカバリ回路11、デシリアライザ15、シリアライザ14、PLL回路13、周波数検出器12を具備する。クロックデータリカバリ回路11は受信信号RXとPLL回路13から生成されるクロック信号TXCLKに応答して、再生クロックCLKと再生データDATAを抽出する。デシリアライザ15はCLKとDATAからパラレル受信データDTを生成し、シリアライザ14はパラレル送信データDRとTXCLKからシリアル送信信号TXを生成する。検出器12は受信信号RXとクロック信号TXCLKの周波数の差を検出して周波数制御信号FCSを生成して、信号FCSに応答して周波数の記差を低減するように、PLL回路13はTXCLKの周期を制御する。

(もっと読む)

利得を自動的に設定する位相ロックループ

【課題】利得を自動的に設定する位相ロックループPLLを提供する。

【解決手段】PLL99は、第1の周波数SRと第2の周波数SNの差を表す第1の信号Aを供給する周波数弁別器130を備える。またPLL99は、周波数弁別器130に結合され、第1の信号Aを受信し、第1の信号Aからの情報に基づいて第2の信号Bを供給する比較器135を備えている。第2の信号Bは設定する位相ロックループに対する利得設定を表す。

(もっと読む)

位相同期回路

【課題】ノイズが混入した場合であっても、所望の周波数で発振信号を生成することが可能な位相同期回路を提供する。

【解決手段】位相同期回路は、低域通過フィルタからの出力電圧に応じて発振回路から出力される発振信号を、制御信号に基づいた利得で増幅する可変利得増幅回路と、可変利得増幅回路からの増幅信号の位相に応じた第1の位相と、増幅信号の基準となる基準信号の第2の位相とを比較して、第1の位相と第2の位相とを一致させるための比較信号を低域通過フィルタに出力する位相比較回路と、出力電圧に基づいて、第1の位相と第2の位相とが一致しているか否かを検出する検出回路と、検出回路の検出結果に基づいて、第1の位相と第2の位相とが一致している場合、利得が所定の値となるような制御信号を生成し、第1の位相と第2の位相とが一致していない場合、利得を所定の値より増加させるような制御信号を生成する制御信号生成回路と、を備える。

(もっと読む)

位相同期ループ回路および通信機

【課題】低消費電力化と小型化とが両立されたPLL回路を提供する。

【解決手段】PLL回路の位相比較器2は、カウンタ16と時間デジタル変換器13とを含む。カウンタ16は、参照クロック信号REFと、デジタル制御発振器の出力を分周した低周波クロック信号CLKAおよび高周波クロック信号CLKBとを受ける。カウンタ16は、高周波クロック信号CLKBのクロック数をカウントすることによって参照クロック信号REFと低周波クロック信号CLKAとの位相差を検出する。時間デジタル変換器13は、参照クロック信号REFと低周波クロック信号CLKAとを受ける。時間デジタル変換器13は、カウンタ16の出力が所定範囲になってから、参照クロック信号REFと低周波クロック信号CLKAとの位相差を、高周波クロック信号CLKBの周期よりも短い時間の精度で検出する。

(もっと読む)

スペクトラム拡散クロック生成器及び半導体装置

【課題】回路規模の大きなDACやアナログ変調回路を用いずに理想的な周波数特性を得ることが可能なスペクトラム拡散クロック生成器及びスペクトラム拡散クロック生成器を備えた半導体装置を提供する。

【解決手段】動作クロックを生成する電圧制御発振器と、動作クロックの位相と基準クロックの位相とを比較し比較結果により電圧制御発振器の発振の基準となる電圧を生成する帰還制御部と、動作クロックの周波数に変動を与える成分をデルタシグマ変調したパルス信号として生成する変調パルス生成部と、パルス信号の振幅を設定するレベル設定部と、帰還制御部が生成した電圧とレベル設定部によって振幅が設定されたパルス信号とを加算する加算部と、加算部の出力信号を濾波して電圧制御発振器に与える制御電圧を生成する低域パスフィルタと、を備える。

(もっと読む)

クロック供給システム

【課題】基準クロックが異常であるのか、電圧制御発振器が異常であるのか故障原因を特定することが可能なクロック供給システムを提供する。

【解決手段】現用系のシステム200のVCXO203の制御値Xがα<X<βにあるかを監視し、その範囲から外れた時に異常を検出する。この異常検出時にVCXO203の制御値を予め決められた制御値γに設定し、現用系のシステムで運用する。また、この運用状態で予備系のシステム210のVCXO213の制御値X’がα’<X’<β’にあるかを判定し、その範囲内にある場合には基準クロック2aの異常と判定し、現用系のまま運用する。一方、その範囲内から外れている場合には現用系のVCXO203が異常と判定し、予備系のシステムに切り替えを行う。

(もっと読む)

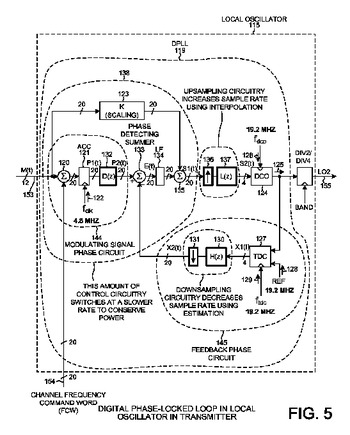

異なるサンプルレートで動作する部分を有するデジタル位相同期ループ

デジタル位相同期ループ(DPLL)は、DCO出力信号及び基準クロックを受信し及びデジタル値の第1のストリームを出力する時間−デジタル変換器(TDC)を含む。TDCを高レートでクロックすることによって量子化雑音が低減される。ダウンサンプリング回路は、第1のストリームを第2のストリームに変換する。第2のストリームは、DPLLの制御部が電力消費量を低減させるためにより低いレートで切り替わることができるようにDPLLの位相検出加算器に供給される。従って、DPLLは、マルチレートDPLLと呼ばれる。制御部によって出力されたデジタルチューニングワードの第3のストリームは、DCOをより高いレートでクロックし、それによってデジタルイメージを低減させることができるようにDCOに供給される前にアップサンプリングされる。受信機用途においては、アップサンプリングは行われず、DCOはより低いレートでクロックされ、それによって電力消費量をさらに低減させる。  (もっと読む)

(もっと読む)

無線周波数集積回路

【課題】無線周波数集積回路において位相エラーを十分に低減する。

【解決手段】無線周波数集積回路は、与えられた電圧に応じた発振周波数の発振周波数信号を生成する電圧制御発振器を有し、発振周波数信号を分周して得られる搬送波に信号波を乗せた無線周波数信号を生成する送信部と、無線周波数回路からの前記無線周波数信号を増幅する電力増幅器と電力増幅器から送信部に回り込む、少なくとも前記発振周波数の同じ周波数の高調波成分を低減する低減手段と、

を有する。

(もっと読む)

位相同期回路及び位相同期方法

【課題】低品質の入力光信号に対しても、安定して同期信号を発生するとともに、入力光信号が有するクロック信号に対する位相誤差検出感度を高くし、同期信号のタイミングジッタを低減し、製造コストを削減することである。

【解決手段】位相同期回路10は、基準信号を発生する基準信号発生部22と、入力光信号と電気信号とを位相比較して第1の位相誤差信号を生成する光位相比較部1と、第1の位相誤差信号と、基準信号と、を位相比較して第2の位相誤差信号を生成し、第2の位相誤差信号における入力光信号のクロック信号周波数に対応する周波数成分のみに応じて入力光信号の位相に同期した出力信号を発生して出力する位相同期部2と、基準信号の分周信号を用いて、位相同期部2から出力された同期信号をSSB変調して電気信号として光位相比較部1に出力する変調部3と、を備える。

(もっと読む)

FM受信機におけるジャマー検出ベースの適応PLL帯域幅調整

FM受信機内の周波数シンセサイザは、フェーズロックドループ(PLL)を用いて、局部発振器(LO)信号を生成する。LO信号は、ミキサに提供される。FM受信機は、さらに、ジャマー検出機能性を含む。ジャマーが検出されなかった場合、PLLのループ帯域幅は、比較的高い値を有するように設定され、それによって、帯域内残留FMの抑制を促進する。ジャマーが検出された場合、PLLのループ帯域幅は、比較的低い値を有するように設定され、それによって、帯域外SSB位相雑音の抑制を促進する。ジャマーが検出されたか否かに依存してループ帯域幅を適応的に変更することによって、帯域内残留FMおよび帯域外SSB位相雑音要求を満たすと同時に、PLL内のサブ回路へのパフォーマンス要求を緩和することができる。PLLのVCOが、ループ帯域幅の適応的な変更による位相雑音をより多く生成できるようにすることによって、VCO電力消費を減らすことができる。 (もっと読む)

分数分割電荷補償手段を有する周波数シンセサイザ

【課題】分数−N補償法で用いられる電荷ポンプを容易に整合し、分数分割によって導入された望ましくない周波数成分を濾波する。

【解決手段】VCO周波数分割器309と基準周波数信号303との間の位相不整合の分数−NPLLにおける補償が可変電荷ポンプ装置307により行われる。移相比較器305は、電荷ポンプ装置の電荷ポンプのいくつかを早くオンにし、残りの電荷ポンプを遅れてオンにするために補償論理501を有する。このプロセスは、部分電荷を適切に補償するために正確な時点で等価電荷をオンにする。

(もっと読む)

半導体装置

【課題】リード動作時における位相調整精度を低下させることなく、DLL回路の消費電力を低減する。

【解決手段】ODT機能を有するデータ入出力回路80と、データ入出力回路80の動作タイミングを規定する内部クロックLCLKを生成するDLL回路100とを備える。DLL回路100は、内部クロックLCLKを高精度に位相制御する第1のモードと、低消費電力で動作する第2のモードとを有し、データ入出力回路80がODT動作を行っていない場合には第1のモードで動作し、データ入出力回路80がODT動作を行っている場合には第2のモードで動作する。このように、ODT動作の有無によってDLL回路100の動作モードを切り替えていることから、厳密な位相制御が不要なODT動作時における消費電力を低減することが可能となる。

(もっと読む)

発振器および位相同期ループ

【課題】発振器の位相雑音を低減し、位相同期ループの消費電力および位相雑音を低減する。

【解決手段】発振器は、共振回路の容量値に応じて発振周波数が可変する構成であって、外部から入力する外部クロックと設定データに応じて、オーバーフロー信号を間欠的に出力するアキュムレータ11と、オーバーフロー信号の間欠入力に応じてオン・オフするスイッチ12と、スイッチ12を介して共振回路に接続される固定容量値を有する容量素子C2とを備え、設定データに応じて間欠的に出力されるオーバーフロー信号の入力によりスイッチ12がオンとなるオン時間における発振周波数と、オーバーフロー信号が入力されないときにスイッチ12がオフとなるオフ時間における発振周波数との間で、オン時間とオフ時間の時間割合に応じた平均発振周波数を可変させる。

(もっと読む)

水晶発振器

【課題】実装スペースとコストの更なる低減のため、電子機器内の水晶部品を1つに集約するためには、消費電流や周波数精度の問題があった。

【解決手段】本発明の水晶発振器は、音叉型水晶振動体と、この振動体の温度による発振周波数の変化を、時間領域で連続的に補正するための温度補償回路を含んだ発振回路とを備え、この発振回路の出力を源振として高周波クロック信号を出力する、複数のPLL(フェイズロックループ)回路を備える。このような構成にすることにより、電子機器内で必要とされる全てのクロック信号を、精度良く提供することができる。

(もっと読む)

PLL回路、PLL回路無線通信機、及びPLL回路のロック検出方法

【課題】デジタル回路で構成出来、ロック検出のエラーやロストの発生を抑制することが出来ると共に、検出時間を短縮することが出来るPLL回路、無線通信機、及びロック検出方法を提供する。

【解決手段】ウィンドウ幅の異なる複数のロック検出部6b−1〜6b−nによる検出結果を用いて検出を行う。ロック判定部7は、複数のロック検出部6b−1〜6b−nによる検出結果に基づいて、ロック状態の検出を行う。

(もっと読む)

シンセサイザと、これを用いた受信装置及び電子機器

【課題】シンセサイザにおけるデジタル的な周波数制御に起因した位相雑音性能の悪化。

【解決手段】本発明のシンセサイザは、基準発振器から出力された基準発振信号が入力される比較器と、比較器の出力側に接続されたフィルタと、フィルタの出力側に接続されて発振信号を出力する発振器と、発振器の出力信号を制御部からの制御信号に基づいて分周する分周器とを備え、比較器は、分周器からの出力信号と基準発振器からの出力信号とを比較してこの比較結果を示す信号をフィルタに出力すると共に、制御部は、温度を検出する検出器の検出結果に基づいて分周器の分周比を時間間隔Tで制御し、時間間隔Tとフィルタのカットオフ周波数fcとの関係は、1/T≧fcを満たす構成である。

(もっと読む)

リングオシレータ及びそれを用いたPLL回路

【課題】 リングオシレータで発生した高調波ノイズによる干渉を抑制できるリングオシレータ及びそのリングオシレータを備えたPLL回路を提供する。

【解決手段】 リングオシレータは、無線装置に内蔵され、複数段のインバータゲートからなる発振回路と、発振回路に接続された切り替えスイッチとを備える。発振回路が発生する高調波ノイズと無線装置の受信周波数とが干渉し、通信感度が低下する場合には、切り替えスイッチによりインバータゲートのリング状に接続される段数を切り替える。リングオシレータが発生する高調波ノイズの周波数を変えることで、無線装置の受信周波数との干渉を抑制する。

(もっと読む)

周波数合成器および周波数合成装置

【課題】基準信号の周波数の実数倍の周波数を持ちジッタの少ないデジタル信号を整数PLLとデジタル回路のみを用いて生成する。

【解決手段】実数である周期指定値をデルタ・シグマ変調器を通してジッタの低周波成分を抑制した整数分周数列を発生させ、その分周数列で基準信号を分周する。その分周出力信号に対して整数PLLによりジッタを除去することにより所望の信号を得る。また、前記デルタ・シグマ変調器では、分周器出力において理想的な信号の立ち上がりのタイミングと実際の立ち上がりのタイミングの誤差を算出し、その誤差に対してデジタルフィルタを通して分周数にフィードバック補償を行う。

(もっと読む)

複数の同調ループを有する周波数シンセサイザ

【解決手段】複数の同調ループ、例えば微同調ループと粗同調ループ、を有する周波数シンセサイザが述べられる。微同調ループは、制限された同調レンジにわたって動作し、細かい周波数分解能を有し得る。粗同調ループは、広い同調レンジにわたって動作し、粗な周波数分解能を有し得る。微同調ループは、参照周波数の参照信号を受信し、細かいステップで調整可能な第1周波数の微同調信号を生成し得る。粗同調ループは、参照信号を受信し、出力信号と微同調信号とに基づいて第2周波数の微同調信号を生成し得る。第2周波数は、粗なステップ、例えば参照周波数の整数倍で調整可能であり得る。出力周波数は、第1周波数及び第2周波数に基づいて決定され得る。 (もっと読む)

61 - 80 / 277

[ Back to top ]