Fターム[5J106CC53]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 周波数変換回路 (1,116) | 分周回路 (990) | 可変分周回路 (277)

Fターム[5J106CC53]に分類される特許

81 - 100 / 277

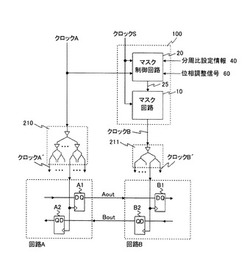

クロック分周回路、及びクロック分周方法

【課題】動作回路の通信タイミングを考慮すると共に、分周時に出力クロック信号の位相調整が可能なクロック分周回路、及びクロック分周方法を提供することである。

【解決手段】本発明にかかるクロック分周回路100は、入力クロック信号(クロックS)のクロックパルスと、通信タイミング信号26と、位相調整信号60に応じて生成されたリセット値81と、に基づき、入力クロック信号に対する通信タイミングの相対的な位相を示すカウント値55を生成し、カウント値55に基づき入力クロック信号のM個のクロックパルスのうち通信タイミング以外のクロックパルスに対してクロックパルスをマスクするマスク信号25を生成するマスク制御回路20を有する。更に、マスク信号25に応じて入力クロック信号のクロックパルスをマスクするマスク回路10を有する。

(もっと読む)

PLL回路

【課題】温度変化により電圧制御発振器を制御する制御電圧に変動が発生しても位相同期回路のロックが外れることを最小限の電圧制御発振器により防止する位相同期回路を提供する。

【解決手段】発振周波数帯域の異なる複数の電圧制御発振器を備えるPLL回路であって、ループフィルタから出力される電圧制御発振器制御電圧の温度特性と正の相関関係にある基準電圧を出力する基準電圧源回路と、電圧制御発振器制御電圧と基準電圧とを比較して判定する判定回路と、判定回路の出力信号により複数の電圧制御発振器から1つの電圧制御発振器を選択する選択回路と、を備えるPLL回路である。

(もっと読む)

周波数シンセサイザ

【課題】 AD変換器への入力レベルが変化したときに、PLL制御が正常に動作しない状況を防止して周波数ずれの発生を防止できる周波数シンセサイザを提供する。

【解決手段】 キャリアリムーブ16と、逆回転ベクトル乗算部17と、位相の時間差検出部18と、加算器19と、位相差の累積加算部20と、ループフィルタ21と、パラメータ出力部25と、振幅情報検出部26と、フィルタ27と、乗算器28とをFPGAで構成し、振幅情報検出部26で検出された振幅情報の値をアンロック検出手段が監視し、当該値が適正範囲内であれば、PLL制御におけるロック(同期)処理を行い、当該値が適正範囲外であれば、PLL制御におけるアンロックを検出し、そのアンロックの検出でアラーム検出するようにした周波数シンセサイザである。

(もっと読む)

PLL回路

【課題】感度関数と相補感度関数の両方が低減されたPLL回路を提供する。

【解決手段】本発明のPLL回路10は、一般的なPLL回路の構成を備えた第1ループ50と、相補感度関数を低減するための第2ループ52とを備えて構成されている。第1ループ50では、周波数が高い基準クロック34を用いて比較部14にて位相比較を行うことにより、感度関数を下げている。そして、第2ループ52からの出力により電流補償部16にて電流値を補完することにより、相補感度関数を下げている。

(もっと読む)

位相同期回路、および通信装置

【課題】設定される動作モードに基づいて処理信号の処理クロック周波数を動作モードに基づいて切り替え、消費電力の低減を図ることが可能な位相同期回路、および通信装置を提供する。

【解決手段】デジタル値で表される発振制御信号に基づく発振周波数の発振信号を出力する発振回路と、搬送波周波数が基準周波数で除算された分周比と動作モードを規定する制御信号とが入力され、分周比を制御信号に基づいて設定された整数値で除算する第1ビットシフト部と、発振信号に基づく信号と制御信号とが入力され制御信号に基づいて設定された整数値により発振信号に基づく信号を分周する第1分周部と、基準周波数信号の各周期において第1累積加算値と第2累積加算値および累積位相の小数部とを比較し位相比較信号を出力する位相比較部と、位相比較信号を制御信号に基づく任意の収束値に収束させ発振制御信号を出力するデータ変換部とを備える位相同期回路が提供される。

(もっと読む)

2ポイント変調と適応遅延マッチングとを用いるデジタル位相ロックドループ

適応遅延マッチングとともに2ポイント変調をサポートするデジタル位相ロックドループ(DPLL)が記述される。DPLLは、それぞれ、発振器の周波数および/または位相の広帯域および狭帯域の変調をサポートするハイパスおよびローパス変調パスを含む。DPLLは、他の変調パスの遅延と合わせるためにある変調パスの遅延を適応して調整することができる。ある設計において、DPLLは、2つの変調パスのうちの一つに、可変遅延を提供する適応遅延ユニットを含む。適応遅延ユニット内で、遅延計算ユニットは、2つの変調パスに適用される変調する信号と、DPLLにおける位相エラー信号とに基づいて、可変遅延を決定する。補正器は可変遅延の小数部分を提供し、プログラマブル遅延ユニットは可変遅延の整数部分を提供する。 (もっと読む)

PLL回路およびその制御方法

【課題】従来のPLL回路は発振周波数を精度良くかつ安定して制御することができないという問題があった。

【解決手段】本発明にかかるPLL回路は、2つのクロック信号の位相差を検出するPFD401と、PFD401の検出結果に基づいて電圧404を出力するLPF403と、電圧404に基づいて出力するVCO出力クロック406の周波数を制御するVCO405と、VCO出力クロック406を分周して出力クロック408を出力する分周器407と、電圧404に基づいて分周器407の分周比を調整する自動調整回路411と、を備える。さらに自動調整回路411は、分周器407を制御する制御信号419と基準電圧を制御する制御信号420とを出力する比較回路434と、基準電圧選択器413と、を備える。このような回路構成により、PLL回路の発振周波数を精度良くかつ安定して制御することができる。

(もっと読む)

制御回路

【課題】シンセサイザの起こり得る温度ドリフトを、連続運転間に補正する制御回路を提供する。

【解決手段】出力信号及び第1の参照信号の間の関係を示す第1の制御信号を生成し及び第1の制御信号に依存する出力信号を生成するために動作可能であり、且つ、第1の制御信号に応じて、出力信号及び第1の参照信号に間の第1の所望の関係を維持しやすいように構成される第1の制御手段と、第1の制御信号と第2の参照信号との間の第2の所望の関係を維持しやすいように、第2の制御信号を経て第1の制御信号に応じて、第1の制御手段の動作に影響を与えるように構成される第2の制御手段と、を有する制御回路。

(もっと読む)

位相検出回路

【課題】位相ロックループ周波数シンセサイザ設計における、大きな電圧制御発振器範囲(例えば、487MHz)、(例えば)1.2V電力供給電圧、および低い電力消費の要求を達成する。

【解決手段】位相検出回路は、参照信号を受信するように構成された参照入力と、フィードバック経路においてディバイダ回路からの分周信号を受信するように構成されたフィードバック入力と、参照信号と分周信号の間の周波数及び位相関係に従って位相ロックループ内のチャージポンプを制御するための制御パルスを生成するように構成されたパルス生成回路と、を有し、分周信号は、分周信号の周期の半分よりも短い長さを具備するパルスを有し、且つ、パルス生成回路は、分周信号のエッジ及び参照信号のエッジから制御パルスのエッジを定義するように、分周信号のパルスをマスクとして使用して参照信号をマスキングすることにより、制御パルスを生成するように構成されている。

(もっと読む)

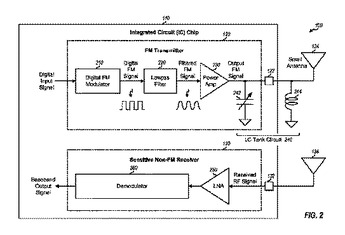

シングルチップ上に集積されたFM送信機及び非FM受信機

例示的な態様は、周波数変調(FM)送信機及び非FM受信機を含み、それらは同一のICチップ上にインプリメントされる。FM送信機は、デジタルFM変調器、ロウパスフィルタ、増幅器、及びLCタンク回路を含む。デジタルFM変調器は、デジタル入力信号を受け取り、デジタル入力信号によってFM変調を行い、デジタルFM信号を供給する。ロウパスフィルタは、デジタルFM信号をフィルタし、フィルタされたFM信号を供給する。増幅器は、フィルタされたFM信号を増幅し、出力FM信号を供給する。LCタンク回路は、出力FM信号をフィルタする。デジタルFM変調器は、PLL内のマルチモジュール分周器の可変分周比を変化させることによってFM変調を行う。デルタ−シグマ変調器は、デジタル入力信号を受け取り、可変分周比を得るために用いられる変調器出力信号を発生する。  (もっと読む)

(もっと読む)

PLL回路

【課題】PLL回路のロックアップ時間を短縮することである。

【解決手段】VCO・電流切替回路15は、外部から与えられる分周データに基づいて、複数のVCO22a〜22nの内の1つを選択するVCO選択信号を出力する。また、VCOを切り替える際に、可変チャージポンプ20の出力電流を通常(ロック時)より大きな値に変更する切替信号を出力する。VCO・電流切替回路15は、VCOの切り替えが終了したなら、可変チャージポンプ20の出力電流を通常時の小さい値に切り替える切替信号を出力する。

(もっと読む)

PLL回路

【課題】PLL回路において、アナログ回路のデジタル化によって生じる量子化雑音を抑制することができる技術を提供する。

【解決手段】基準信号REFと分周後の信号DIVとの位相及び周波数を比較してデジタル値に変換するデジタル位相周波数比較器(DPFD)101と、デジタル位相周波数比較器101の出力から高周波雑音成分を除去するデジタルループフィルタ(DLF)102と、デジタルループフィルタ102の出力のデジタル値をアナログ値に変換するデジタルアナログ変換器(DAC)105と、デジタルアナログ変換器105の出力から高周波雑音成分を除去するアナログフィルタ(AnF)106と、アナログフィルタ106の出力に基づいて周波数が制御される電圧制御発振器(VCO)103と、電圧制御発振器103の出力を分周し、分周後の信号DIVを出力する分周器(DIV)104とを備える。

(もっと読む)

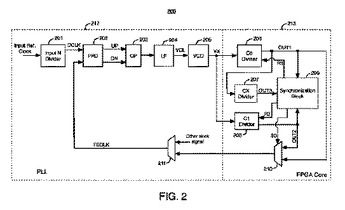

分数クロック信号を生成するための技術

回路は、位相検出回路と、クロック信号生成回路と、第1の分周器と、第2の分周器とを含む。位相検出回路は、入力クロック信号をフィードバック信号と比較して、制御信号を生成する。クロック信号生成回路は、制御信号に応答して、周期的出力信号を生成する。第1の分周器は、周期的出力信号の周波数を第1の値によって分割して、第1の分周信号を生成する。第2の分周器は、周期的出力信号の周波数を第2の値によって分割して、第2の分周信号を生成する。第1および第2の分周信号は、異なる時間間隔の間に、フィードバック信号として位相検出回路に経路指定される。  (もっと読む)

(もっと読む)

位相同期ループ回路

【課題】出力周波数レンジの広いPLL回路を提供すること。

【解決手段】本発明の一態様は、入力パルス信号と出力側からフィードバックされたフィードバックパルス信号との位相差に基づいて生成された電圧を、制御電流Icへ変換する電圧電流変換回路104と、制御電流Icに応じた周波数のパルス信号を生成する電流制御発振器105と、制御電流Icを検出する電流検出部108と、検出された前記制御電流に基づいて、電流制御発振器105から発振される出力パルス信号の周波数レンジを切り替える周波数レンジ切替回路106と、を備えた位相同期ループ回路である。

(もっと読む)

同期化制御回路、半導体装置及び制御方法

【課題】従来の回路に比較し、面積の縮小や消費電力の低減を図ることができる同期化制御回路を提供する。

【解決手段】分周回路部26において、外部クロックに対し位相の進んだ内部クロックLCLKを分周して分周クロックRSELOを生成し、分周クロックRSELOを遅延させて遅延分周クロックRSELIを生成する。外部クロックに対し位相の遅れた内部クロックPCLKに同期して外部から取り込まれた信号を、遅延分周クロックRSELIに同期してラッチ回路22に保持する。次いで、ラッチ回路22の出力信号を分周クロックRSELOに同期してラッチ回路23に読み込み、内部クロックLCLKに同期した信号として出力する。そして、分周回路部26が、変更可能な所定の分周数で内部クロックLCLKを分周する可変分周回路24を備える。

(もっと読む)

無線通信端末および無線通信制御方法

【課題】クロック信号の周波数を大きく変更することなく、クロック信号の高調波による受信信号への影響を抑制する。

【解決手段】制御部13により、受信信号に影響を与えるクロック信号16Sの高調波17Sが持つ高調波周波数が、受信搬送波周波数と一致するように、PLL回路16Aの分周比を制御して前記クロック周波数を調整する。

(もっと読む)

PLL周波数シンセサイザ

【課題】ループフィルタの帯域幅切り替え時の周波数変動を低減することによって、高速に周波数切り替えが可能なPLL周波数シンセサイザを提供する。

【解決手段】PLL周波数シンセサイザは、基準発振器と、分周器と、位相比較器と、チャージポンプと、ループフィルタと、VCOとを備えている。ループフィルタは、チャージポンプとVCOとの間に互いに並列に設けられた第1経路および第2経路と、第1経路上に設けられた第1スイッチと、第2経路上に設けられた第2スイッチとを含み、第1スイッチおよび第2スイッチの双方がオフ状態であるとしたときに、それぞれの寄生容量が互いに同じであり、第1経路および第2経路それぞれの抵抗値が互いに異なり、第1スイッチおよび第2スイッチの一方がオン状態であるとき、他方がオフ状態となる。

(もっと読む)

搬送波生成回路

【課題】広帯域にわたって周波数成分の劣化がない搬送波を生成する搬送波生成回路を提供する。

【解決手段】指定された搬送波の周波数に応じて設定を変更する機能を設け、スプリアスが発生しない設定値に切り替える。

(もっと読む)

半導体集積回路

【課題】入力された信号の位相と内部クロック信号の位相との差を所定の範囲内で吸収する能力を正確に試験することができる半導体集積回路を提供する。

【解決手段】半導体集積回路は、入力された信号の位相によって制御された位相を有する信号を生成する信号生成回路と、制御値を生成する制御値生成ブロックとを備えており、制御値生成ブロックが生成した制御値に応じて信号生成回路が生成する信号の位相を強制的にずらすことによって信号生成回路を試験する。ここで、制御値生成ブロックは、内部クロック信号に同期して動作するとともに、外部から、内部クロック信号よりも低い周波数を有する外部クロック信号に同期して目標値を受信し、受信した目標値に基づいて、内部クロック信号に同期して変化する制御値を生成する。

(もっと読む)

位相同期回路並びに記録再生装置および電子機器

【課題】位相同期回路において、ωn,ζを自由に変更可能でかつキャリブレーション可能にする。

【解決手段】ループフィルタ部106を抵抗素子162と容量素子164の直列回路で構成する。抵抗素子162は差動出力の第1ループフィルタ駆動部104_1(差動出力チャージポンプ回路DOCP)で駆動し、容量素子164はシングルエンド出力の第2ループフィルタ駆動部104_2(シングルエンドチャージポンプ回路SECP)で駆動する。発振部101は、ノードND101の電圧に基づき発振するようにする。発振部101の発振ゲインを補正するキャリブレーション部CALIB を設ける。抵抗回路や容量回路をスイッチングすることなく、ωn,ζを自由に変えられる。ループフィルタは、一方をシングルエンド、他方を差動で駆動すると、抵抗回路や容量回路の各両端に発生する電圧が独立になり、ωn,ζのキャリブレーションがし易くなる。

(もっと読む)

81 - 100 / 277

[ Back to top ]