Fターム[5J106CC53]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 周波数変換回路 (1,116) | 分周回路 (990) | 可変分周回路 (277)

Fターム[5J106CC53]に分類される特許

101 - 120 / 277

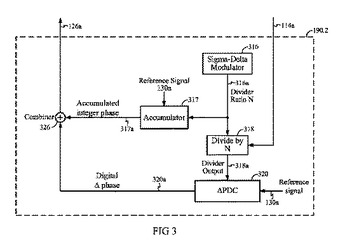

ディジタル位相ロックループにおける累算された位相−ディジタル変換

ディジタル位相ロックループ(DPLL)において信号の累算された位相をディジタル値に変換するための技術。模範的な実施形態では、信号が、分周器比Nで信号の周波数を分割するN分割モジュールと対にされる。分割された信号は、分割された信号の立ち上がりエッジと基準信号の立ち上がりエッジとの位相差を測定するデルタ位相−ディジタル変換器へ入力される。累算された分周器比群と較正された位相差群とが合算され、累算されたディジタル位相が生成される。シグマ−デルタ変調器を用いて分周器比Nを変える更なる技術が示される。  (もっと読む)

(もっと読む)

FM受信装置

【課題】ノイズの少ないFM受信装置を提供する。

【解決手段】アンテナと、発振回路と、位相比較回路と、チャージポンプ回路と、ループフィルタと、VCOと、VCO発振信号を所定の周波数ごとに分周し分周発振信号を生成する第1の分周回路と、VCO発振信号を所定の周波数ごとに分周し局部発振信号を生成する第2の分周回路とを備え、VCOはLC共振回路を含まない構成のものであり、分周発振信号を位相比較回路の入力信号とするものであって、局部発振信号と電波の信号より、複数の中間周波数信号を生成するミキサと、中間周波数信号をA/D変換するA/D変換器と、A/D変換器より出力された信号のうち、複数の中間周波数信号に対応するいずれか一つを選択し復調するデジタル復調器と、を備えたことを特徴とするFM受信装置を提供することにより上記課題を解決する。

(もっと読む)

水晶発振回路

【課題】 複数の異なる周波数信号を出力可能で、消費電力を低減し、構造が簡易で小型化できる水晶発振回路を提供する。

【解決手段】 電圧制御水晶発振器(VCXO)2からの出力を分周比に応じて分周器3で分周し、分周された信号とVCXO2から出力された信号を合成器4で合成し、予め分周比に応じて通過帯域が定められた複数のBPF5に出力し、該当するBPFのみが特定の周波数帯域の信号を通過させ、PLL6で位相制御が為されて、所望の周波数信号を出力する水晶発振回路である。

(もっと読む)

受信側デバイスの出力クロック周波数の補正回路

データ(16)およびタイムスタンプ要素(18)を受信する受信側デバイス(13)の出力クロックの周波数を補正するための出力クロック補正回路(14)は、出力クロックフィードバックループ(20)、FIFOバッファ(22)およびタイムスタンプアジャスタ(24)を含む。出力クロックフィードバックループ(20)は、タイムスタンプ要素(18)に基づいて出力クロックの位相および/または周波数を調節する。FIFOバッファ(22)は、一時的にデータを格納する。タイムスタンプアジャスタ(24)は、FIFOバッファの状態に基づいてタイムスタンプ要素を選択的に調節する。一実施形態では、前記状態が、FIFOバッファ内の実データレベルに少なくとも部分的に基づくものとなる。別の実施形態では、FIFOバッファ(22)が目標データレベル範囲を有し、FIFOバッファ内の実データレベルがこの範囲外となったときに、タイムスタンプ要素が調節される。 (もっと読む)

発振器および位相同期回路のループ帯域補正方法

【課題】安定した高周波信号を発振する発振器および位相同期回路のループ帯域補正方法を実現する。

【解決手段】基準周波数の基準信号を発生する基準信号発生部と、前記基準信号とフィードバック信号との位相差に応じた電圧を出力する位相比較部と、前記位相比較部から出力された電圧が入力され、外部制御信号により、前記位相比較部から出力された電圧のゲインを調整するループフィルタと、前記ループフィルタによりゲインが調整された調整信号に応じた周波数の出力信号を発振する電圧制御発振部と、前記出力信号を分周した分周信号を前記フィードバック信号として前記位相比較部にフィードバックする分周部とを備える。

(もっと読む)

周波数変調機能付きクロック生成回路

【課題】良好なスペクトラム拡散効果を有し、ノイズの発生が少なく周辺回路や電子部品の誤動作を低減することができる周波数変調機能付きクロック生成回路を提供する。

【解決手段】クロック生成回路1は、帰還用分周器17を有し、周波数変調されたクロックを出力するPLL回路10と、帰還用分周器17から所定の周波数のみ取り出しPLL回路10に入力するバンドパスフィルタ20と、三角波を生成する三角波生成回路40とを有し、バンドパスフィルタ20は、サイン波生成器としても機能し、所定のタイミングでサイン波を生成して三角波と合成して帰還用分周器17の分周比を変化させる。

(もっと読む)

位相同期ループ回路

【課題】ループ利得の変動を抑圧できるループ利得検出回路を備えたPLL回路を提供する。

【解決手段】PLL回路内の電圧発振器1で駆動されるカウンタ6と、その出力を周期的に積算するアキュームレータ(ACL)と、ACLのカウント値とレジスタ9に予め設定された設計値とを比較する比較演算回路部8を設け、ACLのカウント値がループ利得と反比例することを応用してPLL回路のループ利得を検出する。検出結果に基づいてチャージポンプ電流等でループ利得の補正を行ってループ利得を校正する。これにより、PLL回路は、PLLを構成する各素子の特性のばらつきに影響しない安定したループ特性を保つことができる。

(もっと読む)

位相同期ループ形周波数シンセサイザ

【課題】サイクルスリップの発生を防止して、短時間で周波数の切り換えを行うことができる位相同期ループ形周波数シンセサイザを得ることを目的とする。

【解決手段】 VCO4により発振される高周波信号Doの周波数が切り換えられる場合、位相比較器2が第1の位相比較信号Dnuと第2の位相比較信号Dndの差分を一定に保持するように構成する。これにより、サイクルスリップの発生を防止して、短時間で周波数の切り換えを行うことができる効果を奏する。

(もっと読む)

オーディオ参照クロックを生成可能な受信装置

【課題】PLL回路に入力されるリファレンス周波数を高くすることができる受信装置を提供する。

【解決手段】受信装置1は、ピクセルクロックを1/CTSで分周して、第1の信号として出力する第1の分周器11と、商CTSquoの値に対応する周期をN−CTSremに対応する回数分第1の信号の周期内に含み、かつ、CTSquo+1に対応する周期をCTSremに対応する回数分第1の信号の周期内に含む第2の信号を、ピクセルクロックの周期を制御することによって出力する周期制御部21と、周期制御部21から出力される第2の信号によって得られるリファレンス信号に基づいて、所望の周波数にロックされた信号を出力するPLL回路31とを備える。周期制御部21は、CTSremの和を随時計算し、当該和がしきい値N−1をオーバーフローするときに応じて、第2の信号の周期を制御する。

(もっと読む)

容量切り換え回路、VCO、およびPLL回路

【課題】 PLLおよびVCOの発振特性を改善できる容量切り換え回路を提供する。

【解決手段】 端子P1と端子P2との間に、コンデンサC1k(k=0〜n)と、FET(Q1k)と、コンデンサC2kとを直列接続する。FET(Q1k)のソースにFET(Q3k)のドレインを接続する。FET(Q1k)のドレインにFET(Q4k)のドレインを接続する。FET(Q3k、Q4k)のゲートは互いに接続し、それらのソースも互いに接続する。FET(Q1k)のゲートに、このFET(Q1k)をオンオフ制御する制御データbkを供給する。FET(Q4k)のソースに、少なくともFET(Q1k)がオフのときには、FET(Q3k、Q4k)をオフにするソースバイアス電圧VSkを供給する。

(もっと読む)

電圧制御型可変周波数発振回路および信号処理回路

【課題】可変容量素子の容量可変域に応じた広い周波数可変域を確保することができる電圧制御型可変周波数発振回路を提供する。

【解決手段】コイルL1,L2および可変容量素子111,112を有する共振回路101と、負性抵抗回路102とを含む発振回路部103を備える電圧制御型可変周波数発振回路である。発振回路部103と電源電位VDDとの間に第1の抵抗301を設ける。また、発振回路部と接地電位端との間には第2の抵抗302を接続するとよい。

(もっと読む)

PLL回路およびそのIC

【課題】 PLL回路としての動作を中断することなく適切な発振信号を出力できるようにする。

【解決手段】 測定時、第1の制御電圧をVCO31に供給する電圧供給回路302と、VCO31の発振周波数を測定する周波数測定回路303とを設ける。使用時、VCO31に供給される第2の制御電圧の大きさを測定する電圧測定回路304を設ける。測定時、電圧供給回路302および周波数測定回路303により、第1の制御電圧とVCO31の発振周波数の変化の割り合いとの関係を示すデータテーブルを作成する。使用時、データテーブルを参照して、電圧測定回路の測定した第2の制御電圧を発振周波数の変化の割り合い示す制御感度に変換する。可変分周回路32の分周比Nにかかわらずオープンループ時の伝達関数が一定となるように、変換結果の制御感度によりチャージポンプ回路34のチャージポンプ電流の大きさを制御する。

(もっと読む)

チャージポンプ回路およびPLL回路

【課題】 広い範囲にわたって良好な特性のチャージポンプ電流の得られるチャージポンプ回路を提供する。

【解決手段】 第1のチャージポンプ部14Aに、定電流源Q1から出力される定電流を、スイッチ回路SW1、SW2の直列回路と、スイッチ回路SW3、SW4の直列回路とに振り分ける制御信号が供給する。残るチャージポンプ部14B、14Cには、定電流源Q1から出力される定電流を、スイッチ回路SW1、SW2の直列回路と、スイッチ回路SW3、SW4の直列回路とに振り分ける制御信号と、スイッチ回路SW1〜SW4をオフにする電位とが、スイッチ回路SWA〜SWDを通じて供給される。必要とするチャージポンプ電流に大きさに対応して、スイッチ回路SW11BA〜SW14Cを制御するとともに、定電流源Q1、Q2の出力電流の大きさを変更することにより、出力端子T3に、必要とする大きさのチャージポンプ電流を得る。

(もっと読む)

発振器制御装置

【課題】安定した位相雑音特性を高速に得ることができる発振器制御装置を提供する。

【解決手段】動作電流制御信号に基づく動作電流を供給する可変電流源14を含み、発振器調整ワードに応じた発振周波数の発振信号を出力するデジタル制御発振器1と、前記発振信号と基準信号との間の位相差を算出し、位相差信号を出力する位相差算出部(2,3,4)と、前記デジタル制御発振器の発振周波数を設定するための周波数命令ワードと前記位相差信号との差分を平滑化して、前記発振器調整ワードを出力するフィルタ6と、前記発振器調整ワードを測定し、前記動作電流制御信号を出力する制御部7と、を備え、前記制御部は、前記動作電流の値を変化させるように前記動作電流制御信号を出力し、前記発振器調整ワードが極大値となる前記動作電流の値を抽出し、前記可変電流源が供給する動作電流がこの抽出した値となるように前記動作電流制御信号を出力する。

(もっと読む)

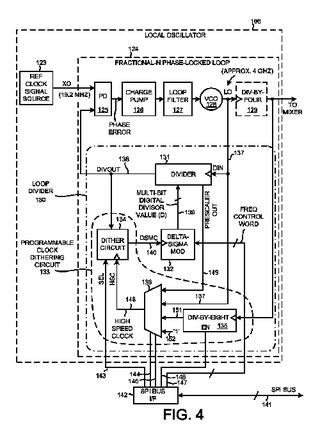

フラクショナルN位相同期回路におけるデルタ−シグマ変調器クロックディザリング

フラクショナル位相同期回路内のデルタ−シグマ変調器に供給されたクロック信号はディザ処理される。1つの例において、PLLは新しいクロックディザリング回路を含む。プログラマブルクロックディザリング回路は、いくつかの方法のうちの選択された1つで、クロック信号の位相をディザ処理するためにシリアルバスを経由して制御可能である。クロック信号が第1の方法(擬似ランダム位相ディザリング)でディザ処理される場合、デルタ−シグマ変調器によって生成されたディジタルノイズの電力は周波数帯域を通じて分散され、それによってノイズがその他の回路構成に干渉する度合を減少させる。クロック信号が第2の方法でディザ処理(ローテーショナル位相ディザリング)される場合、ディジタルノイズの電力が取り払われる周波数であり、それによってノイズがその他の回路構成に干渉する度合を減少させる。  (もっと読む)

(もっと読む)

シンセサイザと、これを用いた受信装置、および電子機器

【課題】精度の高い発振周波数を生み出す事ができるシンセサイザを提供する事を目的とする。

【解決手段】シンセサイザ1は、基準発振器2からの基準発振信号が入力される比較器4と、比較器4の出力信号に基づいて発振信号を出力する電圧制御発振器5と、この電圧制御発振器5の出力信号を制御部7からの制御信号に基づいて分周する第2分周器6とを備えており、比較器4は、第2分周器6からの出力信号と基準発振器2からの出力信号とを比較してこの比較結果を示す信号を電圧制御発振器5に出力し、シンセサイザ1を用いる電子機器の使用状態に基づいて、第2分周器6の分周比の値が決められている。これにより、温度検出部8とMEMS振動子11との間の温度差に起因したシンセサイザの発振周波数誤差を無くす事ができる。

(もっと読む)

シンセサイザと、これを用いた受信装置及び電子機器

【課題】周波数変動の大きな基準発振器を用いて、周波数変動を抑制した局部発振信号及び分周逓倍信号を出力するシンセサイザを小型に実現すること。

【解決手段】本発明のシンセサイザ2は、基準発振器3から出力された基準発振信号を基に局部発振信号を生成して周波数変換部5に入力するとともに、周波数補償部7から出力された周波数補償信号を基に局部発振信号の周波数補償を行うシンセサイザ2であって、局部発振信号を分周又は逓倍した分周逓倍信号を、周波数変換部5の出力側に接続された後段回路部6に入力する分周逓倍部2aを有する。この構成により、シンセサイザ2が周波数変動を補償した局部発振信号を出力するとともに、この局部発振信号を分周又は逓倍して分周逓倍信号を生成することにより、少なくとも1つのシンセサイザで、局部発振信号及び分周逓倍信号の周波数変動を補償することができる。

(もっと読む)

起動制御回路付き水晶発振回路および位相同期回路

【課題】 水晶発振回路が定常発振に達するまでの起動時間を短くすることができる起動制御回路付き水晶発振回路、水晶発振回路の起動時間を短くすることで間欠動作の比率を大きくし、低消費電力化に寄与する位相同期回路を実現する。

る。

【解決手段】 水晶振動子と負性抵抗回路を備えた水晶発振回路の起動制御を行う起動制御回路を含み、一定の発振周波数の信号を出力させる起動制御回路付き水晶発振回路であって、水晶発振回路は、水晶振動子を励振する励振信号を外部から入力するための信号入力端子を備え、起動制御回路は、発振周波数またはそれに近い周波数を有する励振信号を生成し、水晶発振回路の起動時に励振信号を励振信号入力端子に入力し、水晶発振回路の発振周波数が安定する前に励振信号の入力を停止する構成である。

(もっと読む)

フラクショナル−N方式位相同期ループ形周波数シンセサイザ

【課題】 位相比較器の位相差に対する検波電圧特性の非線形性によって、F−N方式PLL周波数シンセサイザ出力に発生するスプリアスの抑圧を実現することを目的とする。

【解決手段】 高周波信号を生成する電圧制御発振器と、前記高周波信号より同期信号を生成する可変分周器と、基準信号を生成する基準発振源と、前記基準信号より位相差を有する2つの基準信号を生成する基準信号生成手段と、前記それぞれの基準信号と前記同期信号を入力とし、第1と第2の位相比較信号を出力する第1の位相比較器と、第3と第4の位相比較信号を出力する第2の位相比較器と、前記第1と第2の位相比較信号を差分した差分結果と、前記第3と第4の位相比較信号を差分した差分結果を合成して平滑化した合成信号を出力するループフィルタとを備え、前記合成信号に応じて電圧制御発振器を制御することにより前記高周波信号を生成する。

(もっと読む)

半導体集積回路

【課題】クロック信号生成部をディジタル制御するレジスタへの制御情報の格納ステップを削減すること。

【解決手段】半導体集積回路は、クロック信号CLKmを生成するディジタル制御信号生成部10、ディジタル制御部20を具備するクロック生成部を含む。クロック生成部は、位相周波数比較器31、制御レジスタ22を更に具備する。比較器31には、基準信号CLKinとフィードバック信号Moutが供給される。制御レジスタ22に比較器31の出力信号FDoutが供給され、制御レジスタ22は複数ビットのディジタル制御情報を格納する。クロック生成部は、複数のロック動作のための複数の初期設定データを予め格納する制御データ記憶回路25を更に具備する。動作選択情報Minに応答して制御データ記憶回路25から初期設定データSet1〜Set5が、制御レジスタ22の上位ビットに格納される。

(もっと読む)

101 - 120 / 277

[ Back to top ]