Fターム[5J106CC53]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 周波数変換回路 (1,116) | 分周回路 (990) | 可変分周回路 (277)

Fターム[5J106CC53]に分類される特許

141 - 160 / 277

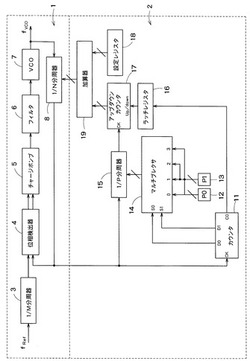

拡散スペクトラムクロック生成装置

【課題】回路規模を大きくせずにEMIを十分に低減できる拡散スペクトラムクロック生成装置を提供する。

【解決手段】拡散スペクトラムクロック生成装置は、クロック信号を生成するPLL(Phase Locked Loop)回路1と、クロック信号の周波数変調を行う周波数変調回路2とを備え、周波数変調回路2は、カウンタ11と、設定レジスタ12,13と、マルチプレクサ14と、1/P分周器15と、ラッチレジスタ16と、アップダウンカウンタ17と、設定レジスタ18と、加算器19とを有する。Hershey-kiss変調プロファイルの1周期分を8等分した各相対時刻ごとの変調ポイントを直線でつないだ変調プロファイルを用いて、1/N分周器8の分周比を1周期に8回変化させるため、Hershey-kiss変調プロファイル用の特性テーブルを設けなくても、Hershey-kiss変調プロファイルと同様の周波数変調を行える。

(もっと読む)

PLL回路

【課題】複数の分周回路を備えるPLL回路に関し、PLL回路の新たな回路構成を提案する。

【解決手段】基準クロックの位相と位相比較クロックの位相とを比較し、位相差に応じた信号を出力する位相比較回路と、前記位相比較回路により出力された前記信号をフィルタリングするループフィルタと、前記ループフィルタによりフィルタリングされた前記信号に応じた周波数のクロックを出力する電圧制御発振回路と、前記クロックを分周して前記位相比較クロックを生成する第1の分周回路と、前記クロックを分周して出力クロックを生成する第2の分周回路と、前記第1の分周回路の分周数と前記第2の分周回路の分周数とを制御する分周制御回路とを備えることを特徴とするPLL回路。

(もっと読む)

直接変換プロセスにおける局部発振器漏洩制御

【課題】直接変換プロセスにおける局部発振器の漏洩制御。

【解決手段】ゼロ中間周波数(IF)受信機あるいは送信機における、局部発振器(LO)周波数を発生するためのシステムおよび方法が与えられる。電圧制御発振器(VCO)から信号が受信される。信号はVCO周波数を有している。VCO周波数は分周された周波数を有している信号を生成するために数値Nによって分周される。VCO周波数を有している信号はそこで、出力周波数を有している出力信号を生成するために、分周された周波数を有している信号と混合される。局部発振器漏洩が減少される。したがって、受信機あるいは送信機は、複数の無線通信帯域およびモードで動作し、そして組み合わせられた規格を満足することが可能である。

(もっと読む)

分周回路および分周方法

【課題】50%デューティ・サイクルを有するプログラマブル整数クロック分割の回路お

よび方法。

【解決手段】整数分割値により入力信号の周波数を分割する回路および方法。回路は一般

的に(a)入力信号を受信する第1の複数の直列接続された遅延要素および第1の設定可

能なフィードバック・ネットワークを含む第1周波数分割器、(b)入力信号の逆転を受

信する第2の複数の直列接続された遅延要素および第2の設定可能なフィードバック・ネ

ットワークを含む第2周波数分割器、(c)第1および第2周波数分割器の出力を選択し

および/あるいは組み合わせ、周波数分割出力信号を形成するよう構成される設定可能な

論理、および(d)第1および第2の設定可能なフィードバック・ネットワークおよび設

定可能な論理を選択可能な形で設定するよう構成されるプログラマブル回路、を含む。

(もっと読む)

周波数掃引発振回路

【課題】温度変化等の環境条件の変化やデバイス自体の特性変動要因があっても、掃引される周波数の安定度が高く、また高速な周波数掃引ができるようにする。

【解決手段】VCO26に電子同調電圧を入力し、周波数掃引を行う周波数掃引発振回路で、上記VCO26の出力周波数を分周器31で分周した周波数信号と基準信号源32で得られた基準(絶対)周波数信号とにおける両方の位相及び周波数をPFD33で比較し、このPFD33の出力に基づき上記分周器出力周波数が基準周波数と一致したときのVCO26の電子同調電圧を求め、この電圧によって掃引周波数を校正する。例えば、上記基準周波数を24GHz帯の占有帯域幅の中心周波数に設定し、この中心周波数の校正により占有帯域幅での安定した周波数掃引が行われる。また、幅設定回路を設け、掃引のためのサンプリングポイント数を一定に保ちながら、掃引幅を変えることができる。

(もっと読む)

シンセサイザ装置及びこれを備える携帯通信端末

【課題】デュアルシンセサイザ装置において、基板の定在波比が劣化しても、簡単な構成でアイソレーションの低下を防止する。

【解決手段】プリント基板13上には第1及び第のPLLシンセサイザ部11及び12が配置され、第1及び第2のPLLシンセサイザ部には基板に形成された配線パターン13aを介して基準発振器14から基準信号が与えられ、選択スイッチ(SW)45によって第1及び第2のPLLシンセサイザ部からの出力信号のうちいずれか一方が選択される。配線パターンのインダクタンスとこのインダクタンスと対向するアースパターンからなる第1及び第2のコンデンサとによってローパスフィルタが構成される。

(もっと読む)

PLL回路

【課題】目標周波数の変更に応じて、制御電圧が所定の許容範囲内に収まるようにVCO特性が切り替えられるものであって、かかる切替を極力早いタイミングで実行し得るPLL回路を提供する。

【解決手段】複数のVCO特性に切替可能である電圧制御発振部と、位相比較器と、制御電圧と所定の許容範囲との比較結果に応じてVCO特性の切替を行うVCO切替部と、を備え、現時点で目標周波数に設定されている周波数のクロックを出力するPLL回路であって、VCO切替部は、サンプリングされた電圧が許容範囲内に収まっているか否かを検出するとともに、該検出結果に応じて、前記VCO特性の切替えを行うものであり、このサンプリングのタイミングは、目標周波数が切り替えられた時から、予め定められた時間である第1時間が経過したタイミングとされているPLL回路とする。

(もっと読む)

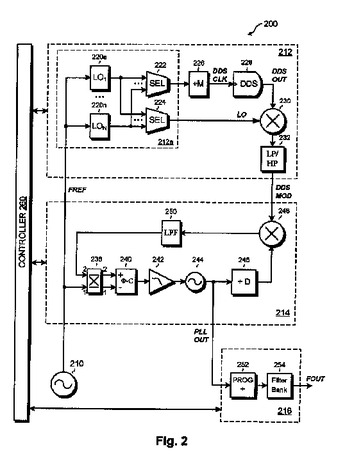

コスト的に有効な低ノイズの単一ループシンセサイザー

低コストで低位相ノイズのマイクロ波シンセサイザーは、DDS変調回路と位相ロックループを含む。DDS変調回路はDDSの出力を高周波数に変調する。位相ロックループはDDS出力をダウンコンバートし、ダウンコンバート信号を比較的低周波数の固定されたリファレンスにロックする。  (もっと読む)

(もっと読む)

タイミングクロック生成装置、データ処理装置及びタイミングクロック生成方法

【課題】 好適なタイミングでデータを読み込むことができるクロックを簡単に生成することができるタイミングクロック生成装置を提供する。

【解決手段】 基準となるシステムクロックをデータの入力タイミングに同期させる第1PLL回路21と、システムクロックの周波数を所定倍に逓倍した逓倍クロックを生成する第2PLL回路23及び2分周回路24と、逓倍クロックの遷移タイミングのうち、データの取込みに使用するタイミングを選択する制御部5と、選択された遷移タイミングに同期し、システムクロックと同一周波数を有するデータ取込み用クロックを生成する位相調整・分周回路26と、を有している。

(もっと読む)

周波数シンセサイザ及びこれを用いた無線通信装置

【課題】インダクタの使用による面積増大や、製造ばらつきによる歩留まり低下を防ぎつつ、動作周波数範囲を拡大する。

【解決手段】制御電圧によって制御される周波数で発振して発振信号を出力する電圧制御発振器106と;発振信号を分周して第1の分周信号を出力する、自走周波数が制御可能なプリスケーラ107と;第1の分周信号を分周して第2の分周信号を出力するプログラマブル・ディバイダ102と;第2の分周信号の位相と基準クロック信号の位相を比較して位相差に対応する信号を出力する位相比較器108を含み、位相差に対応して制御電圧を生成する制御電圧生成部と;第2の分周信号の周波数と基準クロック信号の周波数を比較して周波数差に対応した信号を出力する周波数比較器103と;周波数差に対応した信号に従って周波数差を最小化するように自走周波数を制御する制御部109と;を具備する。

(もっと読む)

無線受信回路および入力妨害波低減回路

【課題】広い周波数領域に渡って妨害波を低減できる入力妨害波低減回路の小型化、およびそのような入力妨害波低減回路を備える無線受信回路の小型化を図る。

【解決手段】受信信号は、トランジスタQ1のゲートに与えられる。トランジスタQ1はトランジスタQA〜QDに接続され、トランジスタQ1、QA〜QDにより4個の増幅器が構成される。トランジスタQA〜QDには、それぞれ調整回路13A〜13Dが接続されている。調整回路13A〜13Dは、LC共振回路であり、その共振周波数は調整信号および微調整信号により調整される。選択信号は、4個の増幅器の中から使用すべき増幅器を選択する。選択された増幅器の利得周波数は、対応する調整回路(13A〜13D)の共振周波数に応じて決まる。選択された増幅器により増幅された信号が出力される。

(もっと読む)

分数分周PLL装置、およびその制御方法

【課題】設定すべきパラメータ数が減ぜられて使い勝手の向上が図られると共に、回路の簡略化を図ることが可能な分数分周PLL装置、およびその制御方法を提供すること

【解決手段】第1分周信号fprの初期のAサイクルの期間は、第2分周信号fAがハイレベル、第3分周信号fBがローレベルに維持される。3モジュラスプリスケーラ13は(M+1)分周値となる。引き続くBサイクルでは、第2分周信号fAがローレベル、第3分周信号fBがハイレベルである。3モジュラスプリスケーラ13は、ΣΔ変調器8から出力される擬似乱数の符号に合わせて、負値の場合に(M−1)分周値、正値の場合に(M+1)分周値となる。その後は、M分周となる。比較分周器4では、擬似乱数値Bxを含む(MN+A+Bx)の分周値が得られる。負値を含む擬似乱数をそのまま使用してΣΔ変調による分数分周を実現できる。

(もっと読む)

受信装置

【課題】異なるリファレンスクロックを共有し、リファレンス信号を分周してローカル信号として利用する場合にスプリアスが発生するという問題があった。

【解決手段】ローカル信号を出力する電圧制御発振器101と、ローカル信号と基準クロック信号とを入力し、フラクショナル分周器102によってローカル信号を、複数の分周数を時分割で切り替え、その平均の分周数で分周した信号と、基準クロック信号との位相を位相比較器104において比較し、比較した位相が同期するように電圧制御発振器101を制御する同期部107と、固定された分周数でローカル信号を分周して出力する固定分周器108と、を備える。

(もっと読む)

PLL制御システム

【課題】VCOのバンド毎にチャージポンプ電流を設定しても、ループ帯域のばらつきを抑圧することができるPLL制御システムを提供する。

【解決手段】PLL制御システムにおいて、TCXO8と、分周器B8と、複数のバンドを有するVCO4と、分周器A5と、分周器A5と分周器B8の2つの分周信号を比較する位相比較器6と、VCO4への電圧を出力するループフィルタ2と、位相比較器6の比較信号に応じてループフィルタ2へ電流を供給するチャージポンプ回路3と、ループフィルタ2に対してプリチャージするプリチャージ回路1と、制御部9とを備え、制御部9は、プリチャージ回路1によるプリチャージを、複数のバンドに対応して予め設定された離散的な情報に基づいて離散的に制御する。

(もっと読む)

PLLシンセサイザ

【課題】 高速起動性、低消費電力性、定常状態における低スプリアス性を同時に満足し、かつ性能を左右するパラメータを最適化する。

【解決手段】 分数分周モードと整数分周モードとを切り換える構成であり、PLL起動時から収束に至るまでの収束時間Tacq を設定し、その収束時間Tacq が、制動係数ζ、固有周波数ωn 、初期周波数差Ω0 に対して、

Tacq =Ω02/(2ζωn3) …(a)

で表されるときに、制動係数ζを0.5 ≦ζ≦1とし、PLL起動時に固有周波数ωn が (a)式を満たすように分数分周モードの分周比を設定し、収束したと見なすタイミングTs(=Tacq)で、ループフィルタを切り換えることなく、整数分周モードの分周比に切り換える構成である。

(もっと読む)

周波数シンセサイザ及びフェーズロックループ、並びにクロック生成方法

【課題】従来構成のPLLを用いることなく、高精度の分周を回路増加を抑えつつ実現可能な周波数シンセサイザ及びクロック生成方法を提供する。

【解決手段】周波数シンセサイザは、リファレンスクロック発生器501からのN相のクロックを基に複数の周波数のクロックを生成する位相選択合成器502、503を備える。位相選択合成器502、503において、クロック選択手段504は、N相クロックと位相番号(j:0から(N−1)までの整数)を入力し、位相番号に対応したクロックを選択することで(N/M)fのクロックを生成する。位相番号生成手段505は、(N/M)fのクロックと分周分母M及び分周分子Nを入力し、(N/M)fのクロックに同期して、分周分母M及び分周分子Nから算出される値(M−N)を累算し、累算値ACCをNで割った剰余を位相番号(j)とする。

(もっと読む)

時間デジタル変換装置およびデジタル位相同期ループ装置、受信機

【課題】広帯域の周波数範囲に対応可能で、量子化ノイズ成分を増大させることなく低消費電力化を図る。

【解決手段】時間デジタル変換器104は、発振周波数を制御する周波数制御信号16を用いて、入力周波数に応じて動作する遅延回路10−1〜10−nの段数を切り替えるスイッチング素子12−1〜12−nを備えている。入力周波数の周期に応じて必要な段数の遅延回路だけが動作することとなるため、広帯域の周波数範囲に対応しながらも系全体の低消費電力化を図ることが可能となり、特に高い入力周波数において低消費電力化を図ることができる。

(もっと読む)

圧電振動子の駆動装置および超音波美顔装置

【課題】本発明は、所望の駆動周波数に容易に設定可能な圧電振動子の駆動装置及び超音波髪処理装置を提供する。

【解決手段】本発明の圧電振動子の駆動装置は、制御電圧の電圧値に応じて発振周波数が制御されるVCO114と、VCO114から出力された出力信号を固定の第1分周比で分周し分周信号として出力する固定分周器115と、第1基準信号を生成する基準発振部111Aと、分周信号の位相と第1基準信号の位相との差に応じた誤差信号を出力する位相比較器112と、この誤差信号を濾波し制御電圧として出力するLPF113とを備え、基準発振部111Aが、第2基準信号を生成する発振器1111と、第2基準信号を可変の第2分周比で分周し第1基準信号として出力する可変分周器1112と、第2分周比の設定を受け付けてこの第2分周比で発振器1111の第2基準信号を分周するように可変分周器1112を制御する分周制御部1113とを備える。

(もっと読む)

信号発生装置

【課題】IC化が可能なように、VCOの出力の位相雑音のうち、中心周波数から所望の離調周波数における位相雑音を軽減化した信号発生装置を提供することである。

【解決手段】基準信号を出力する基準信号源1と、発振周波数を電圧制御可能な可変信号源3aを有し、可変信号源の出力信号を基準信号に位相同期させる複数のPLL手段31、32、・・3)と、各PLL手段の該各可変信号源の出力信号を合成する合成手段2と、各可変信号源の出力信号の位相が前記合成手段により合成後に同一となるように各可変信号源の出力信号の位相を調整する移相手段41、42、・・4Mとを備えた。

(もっと読む)

FM受信機

【課題】高速ロックアップ時から安定化期間(ロック状態)へ移行する際に発生する音揺れを無くし、聴感悪化を回避する。

【解決手段】PLL回路100がアンロック状態ではPLL回路100がチャージポンプ回路200のチャージポンプ電流が大レベルである高速応答状態となり、PLL回路100がロック状態ではPLL回路100がチャージポンプ回路200のチャージポンプ電流が高速応答状態より少ない小レベルである低速応答状態となる。PLL回路100がアンロック状態からロック状態へ移行するロックアップ時において、PLL回路100が高速応答状態から、チャージポンプ回路200のチャージポンプ電流が高速応答状態より少なく低速応答状態より多い中レベルである中速応答状態を経由して、低速応答状態へ移行する。

(もっと読む)

141 - 160 / 277

[ Back to top ]