Fターム[5J106CC53]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 周波数変換回路 (1,116) | 分周回路 (990) | 可変分周回路 (277)

Fターム[5J106CC53]に分類される特許

161 - 180 / 277

信号発生装置

【課題】本発明では、汎用DDSを使用した周波数可変の信号発生装置において、ジッター発生を抑制し、高精度の周波数可変の矩形パルス信号を発生する。

【解決手段】周波数可変の信号発生装置は、設定値に応じて変更される周波数のアナログ信号を出力するDDS1と、該アナログ信号から該周波数の第1矩形パルス信号を生成するコンパレータ3と、第1矩形パルス信号を設定される分周比で分周した第2矩形パルス信号を出力するプログラマブル分周器41と、制御部4とを備える。該周波数を高周波数領域側に変更の場合、該分周器に対し第1矩形パルス信号を出力信号Soとする。該周波数を低周波数領域側に変更の場合、DDSに対して設定値を分周比倍の値に変更制御して該分周比倍の周波数を有する第1矩形パルス信号を発生させ、分周器において当該分周比で分周した当該周波数の第2矩形パルス信号を出力信号Soとする。

(もっと読む)

寄生低周波生成の除去をした広帯域周波数シンセサイザ

広帯域周波数シンセサイザ(1)が、高周波出力信号(FS)を供給するための電圧制御発振器(4)と、デュアルモード分周回路(5)と、分周回路の分周モードを選択するための手段(9)と、位相検出器(2)と、ローパスフィルタ(3)とを含む。位相検出器(2)は、基準周波数信号(Fref)を分周回路の分周した周波数信号(Fdiv)と比較して、発振器(4)の電圧を制御するためのフィルタリングした信号を供給する。分周回路(5)は、第1のモードM1における第1の分周係数N1で、又は第2のモードM2における第1の係数N1とは異なる第2の係数N2で、出力信号の周波数を分周して、分周した周波数信号(Fdiv)を供給する。選択手段(9)は、第1及び第2の分周係数N1及びN2により定められる周波数帯域において、分周回路の第1又は第2の分周モードを、プログラムした出力信号の周波数の関数として所定の時間により選択する。この周波数が周波数帯域の中心に近い場合、デュアルモード分周回路が、選択手段(9)のプログラミングに基づいて、第1のモードM1における第3の係数N3で、又は第2のモードM2における第3の係数N3とは異なる第4の分周係数N4でもって出力信号の周波数を分周する。少なくとも第3の分周係数N3又は第4の分周係数N4は、第1又は第2の分周係数N1又はN2とは異なる。この結果、第3及び第4の係数N3及びN4により定まる周波数帯域の中心が、プログラムした出力信号の周波数に対してシフトされる。 (もっと読む)

シグマデルタ変調器およびフラクショナル周波数シンセサイザ

【課題】出力信号の増加および減少の振幅を小さくする。

【解決手段】入力信号をシグマデルタ変調した出力信号を出力するシグマデルタ変調器であって、直列に接続された複数の累算器と、それぞれの累算器が出力する比較結果信号に基づいて、出力信号を生成する出力信号生成部とを備え、それぞれの累算器は、入力される信号の値を積分し、積分値が基準値以上となった場合に、所定の値の比較結果信号を出力すると共に、積分値から比較結果信号の値を減算し、初段の累算器には、入力信号の値が入力され、他の累算器には、前段の累算器の積分値が入力され、少なくとも一つの累算器は、積分値の波形の所定の高周波成分を除去するローパスフィルタを有するシグマデルタ変調器を提供する。

(もっと読む)

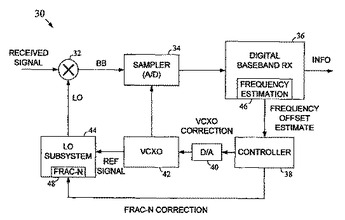

周波数修正を効率的に適用するための方法および装置

【課題】

電圧制御発振器によって駆動される分数分周方式シンセサイザを有する構造において、周波数精度を維持する。

【解決手段】

このために、最初に、分数分周方式シンセサイザを使用することで、大きな周波数誤差を修正する。つぎに、分数分周方式シンセサイザから電圧制御発振器へ、修正値を毎回少しずつ、ゆっくりと移動させる。  (もっと読む)

(もっと読む)

位相同期発振器

【課題】 位相同期発振器において、感度の不安定領域を解消するために不感帯以外の部分でパルスを発生させることにより、位相差に比例してパルス幅が変化し、不感帯で感度が出ない位相状態でも位相情報を検知することができるようにした位相同期発振器を提供する。

【解決手段】電圧制御発振器4の出力信号の一部を可変分周器5を経由して位相比較器2の一方の入力に接続し、基準信号を固定分周器1を介して前記位相比較器2のもう一方の入力に接続し、前記位相比較器2の出力をローパスフィルタ3を介して前記電圧制御発振器4の入力に接続することによりループを形成し、前記可変分周器5を変化させて位相差に比例したパルス幅を発生させて位相情報を検知する。

(もっと読む)

マルチモジュラス・デバイダ・リタイミング回路

マルチモジュラス・デバイダ(MMD)がMMD入力信号を受信しかつMMD出力信号SOUTを出力する。MMDはモジュラス・デバイダ・ステージ(MDSs)のチェーンを含む。各MDSは入力信号を受信し、それを2又は3で割り、そしてその結果を出力信号として出力する。各MDSは、それが2で割るか又は3で割るかを制御するそれ自体のモジュラス制御信号に応答する。1つの実例では、順次論理素子がSOUTを出力する。前記チェーンの第1のMDSステージのうちの1つのロージッタ・モジュラス制御信号が、順次論理素子を第1の状態に置くために用いられる。前記チェーンの中間におけるMDSステージうちの1つの出力信号が、前記順次論理素子を第2の状態に置くために用いられる。前記順次論理素子は前記MMD入力信号の高い周波数でクロックされないので、電力消費は低い。  (もっと読む)

(もっと読む)

AM/FM受信機用PLLシンセサイザ回路とその切り替え方法

【課題】AM受信時とFM受信時の交差周波数を制御することでS/N特性を向上させるPLLシンセサイザ回路を提供する。

【解決手段】基準信号とPLLシンセサイザ回路の出力信号を分周した分周信号との間の位相差に応じた位相差信号を生成する位相比較回路と、位相差信号に基づいて電流制御をするとともに、AMで使用する場合とFMで使用する場合で電流制御を切替えてチャージポンプ信号を生成するチャージポンプ回路と、AMで使用する場合とFMで使用する場合で、チャージポンプ回路の電流制御を切り替えるためのレジスタ回路と、チャージポンプ信号を入力し平滑化して制御電圧として制御電圧信号に応じた周波数で発振して局部発振信号を出力するVCO回路と、局部発振信号を分周して分周信号として出力する分周回路と、を具備するAM/FM受信機用PLLシンセサイザ回路である。

(もっと読む)

シンセサイザモジュール

【課題】 周波数設定者の利用形態に応じて発振周波数の設定を容易できるシンセサイザモジュールを提供する。

【解決手段】 CPU10は、ロータリーSW11の状態を判断し、ロータリーSW11で設定されたCH番号が有効な値であれば、スイッチによる周波数設定を行い、有効な値でなければ、パワーオフ直前の最終設定周波数を再設定し、その後にシリアルバス13から入力されたシリアル信号による周波数設定を行うものであり、ロータリーSW11による設定とシリアル信号による設定をぶつかることなく周波数設定者の利用形態に応じて適正に行うことができるシンセサイザモジュールである。

(もっと読む)

低電力のモジュラス分周器ステージ

モジュラス分周器ステージ(MDS)は、第1と第2のステージを含んでいる。MDSは、MDSが2分割モードまたは3分割モードのいずれで動作するかを決定するモジュラス除数制御信号Sを受信する。MDSのステージは、他のMDSからフィードバック・モジュラス制御信号も受信する。MDSは、2分割モードの場合、フィードバック・モジュラス制御信号にかかわらず、2で分割(分周)する。電力を節約して使用するため、MDSステージが2分割モードで動作するとき、第1のステージには電力が供給されない。MDSは、3分割モードの場合、フィードバック・モジュラス制御信号に依存して2または3のいずれかで分周する。電力消費をさらに減らすため、MDSステージが3分割モードにあるにもかかわらず2分割動作を行っているとき、第1のステージには電力が供給されない。第1のステージが電力供給されていないとき、電力ダウントランジスタは、第1のステージの出力を適正な論理レベルに維持する。 (もっと読む)

PLLシンセサイザおよびロック検出器

【課題】 高速起動性、低消費電力性、定常状態における低スプリアス性を同時に満足することができるPLLシンセサイザおよび同期引き込みを検出するロック検出器を提供する。

【解決手段】 切換型可変分周器を用いた位相同期ループ(PLL)構成により、電圧制御発振器の出力信号の周波数および位相の同期引き込みを行うPLLシンセサイザにおいて、電圧制御発振器の制御電圧Vvco をモニタし、その変動量ΔVvco が所定の範囲よりも大きいか小さいかを判定し、制御電圧の変動量ΔVvco が所定の範囲よりも小さくなったときに同期判定信号を出力するロック検出器を備える。

(もっと読む)

通信用半導体集積回路

【課題】送受信動作に使用する周波数シンサセイザとしてフラクショナルN PLL回路を含むRF通信用半導体集積回路において、PLL回路のチャージポンプ回路CPCのソース電流注入トランジスタとスィンク電流放出トランジスタとのミスマッチに起因する非線型性の影響を軽減する一方、PLL回路の位相ノイズを低減するための補償回路の回路規模を小さくして補償回路の制御も単純化すること。

【解決手段】受信動作と送信動作とに使用する周波数シンサセイザFrct_SynthとしてフラクショナルN PLL回路のクローズドループ帯域を、数十KHzのオーダーの狭帯域とする。チャージポンプ回路CPCの2つのトランジスタのミスマッチに起因する非線型性の影響の軽減を最も段純な方法であるオフセット回路MN2、MN3によるループフィルタLFCへのdc直流電流Ioffsetの注入もしくはLFCからのIoffsetの放出によって実現する。

(もっと読む)

PLLシンセサイザ

【課題】 高速起動性、低消費電力性、定常状態における低スプリアス性を同時に満足させるPLLシンセサイザを構成する。

【解決手段】 可変整数分周器と可変分数分周器としての機能を有し、外部からの切換信号によりこの2つの分周器の機能を切り換える手段を含む切換型可変分周器と、外部からの切換信号により分周比の切り換えが可能な切換型基準分周器と、切換型可変分周器を可変分数分周器として機能させ、かつ切換型基準分周器の出力信号の周波数が電圧制御発振器の出力信号の周波数チャネル間隔より大きくなるようにその分周比を設定する分数分周モードと、切換型可変分周器を可変整数分周器として機能させ、かつ切換型基準分周器の出力信号の周波数が電圧制御発振器の出力信号の周波数チャネル間隔に等しくなるようにその分周比を設定する整数分周モードを切り換える切換制御回路を備える。

(もっと読む)

PLL回路、PLL回路の干渉防止方法及びこのPLL回路を搭載した光ディスク装置

【課題】PLL回路間の相互の干渉を抑える。

【解決手段】検出器30は、入力信号の周波数がスイープされるPLL回路20の出力信号周波数と所定の周波数との差が第1の閾値以下であるか否かを検出する。分周比設定回路40は、この差が第1の閾値以下である場合にPLL回路10の出力信号周波数を変更するように制御する。所定の周波数とは、PLL回路10の出力信号周波数に基づいて予め設定した固定の周波数である。PLL回路10は、PLL回路10の出力信号周波数を定める分周器11、16、17を備え、分周器の分周比を分周比設定回路40の制御によって変更可能となるように構成する。分周比設定回路40の制御によって変更された出力信号周波数と変更される前の出力信号周波数との差が第2の閾値以下となるように分周器の分周比を決定する。

(もっと読む)

ディジタル処理装置のノイズ低減方式

【課題】ディジタル信号処理回路によってPLLや周波数シンセサイザ等を構成するディジタル処理装置のノイズ低減を確実、容易にする。

【解決手段】PLLの位相比較演算を行うディジタル処理デバイス115をディジタル信号処理回路115A〜115Cで構成する周波数シンセサイザにおいて、ノイズ低減部115Dは、多数の論理回路要素がほぼ同時にオン/オフ動作するディジタルローパスフィルタ115Bと同等のオン/オフ動作になる回路構成にし、かつフィルタ115Bのオン/オフ動作と逆のオン/オフ動作させることでノイズを低減する。

(もっと読む)

デジタル放送受信装置およびデジタル放送システム

【課題】本発明は、可変周波数の水晶発器(VCXO)を用いること無く、基地局と受信装置間の時間情報および基準クロックの同期を実現することができる、デジタル放送受信装置等を提供する。

【解決手段】水晶発振子22は、所定の固定周波数のクロックを発振する。可変デジタル分周回路24は、固定周波数を分周比によりデジタル分周し、分周比を変更することができる。システムでコーダ5は、基地局からの基準時間情報を検出する。基準カウンタ18は、受信装置20の時間情報を生成する。位相比較器13は、基準時間情報と時間情報との差分を検出する。分周比制御回路25は、前記差分に基づいて前記分周比の変更を制御する。また、基準カウンタ18は、可変デジタル分周回路24により分周された周波数を有するクロックに基づいて時間情報の生成を行い、時間情報を位相比較器13にフィードバックさせている。

(もっと読む)

半導体集積回路

【課題】フラクショナル−N PLL回路のサイクルトゥサイクルジッターを低減すること。

【解決手段】フラクショナル−N PLL回路は、位相周波数比較器PFD、チャージポンプ回路Ch_Pmp、ループフィルタLp_Flt、電圧制御発振器VCO、フラクショナル分周器DIV、ΣΔ変調器ΣΔModを含む。基準クロック信号RCLKと出力帰還信号VCLKとの位相差の検出動作に基づくループフィルタLp_Fltの出力電圧VCNTの電圧生成動作が時間差を有する複数の動作により実行されるように位相周波数比較器とチャージポンプ回路との一方が構成されている。

(もっと読む)

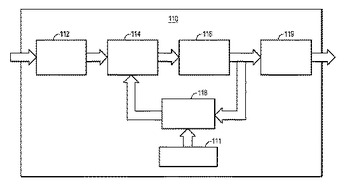

位相同期回路を設定する方法およびシステム

位相同期回路(PLL)設定は、種々の方法および装置を用いて実行される。1つの実施例によれば、1組の所望の位相同期回路特性を満たすPLL回路について低電力設定が決定される。PLL回路(110)は、第1の分周器(112、119)、フィードバック分周器(118)およびフラクショナル−Nモード(111)を有している。  (もっと読む)

(もっと読む)

位相同期ループ形周波数シンセサイザ

【課題】位相比較器のフリップフロップ間の誤差に起因するスプリアスを抑圧することができる位相同期ループ形周波数シンセサイザを得ることを目的とする。

【解決手段】位相比較器33から出力された位相比較信号Dnu(t)を第1の利得値αnuで電圧増幅するとともに、その位相比較器33から出力された位相比較信号Dnd(t)を第1の利得値αnuと異なる第2の利得値αndで電圧増幅し、電圧増幅後の位相比較信号Dnu(t)と電圧増幅後の第2の位相比較信号Dnd(t)との差分信号を出力する減算回路33を設ける。

(もっと読む)

PLL回路、復調回路、ICカード及びICカード処理装置

【課題】本発明は、PLL回路、復調回路、ICカード及びICカード処理装置に関し、例えば非接触により種々のデータを入出力するICカードと、このICカードとデータ通信するICカード処理装置に適用して、簡易な構成で、入力信号が劣化した場合でも確実に入力信号を処理することができるようにする。

【解決手段】90度位相の異なる発振出力信号による位相比較結果の正負を基準にして制御方向を決定し、この制御方向に発振出力信号を制御する。

(もっと読む)

ディジタルPLL装置

【課題】入力信号の周波数が変動してもジッタを低減させることが可能なディジタルPLL装置を提供する。

【解決手段】本発明の一実施形態に係るディジタルPLL装置は、入力信号に対する再生クロックの位相遅れ、位相進みを検出する位相検出器と、位相検出器からの出力信号を積分し、積分値に応じて位相ずれ信号を発生するランダムウォークフィルタ部と、入力信号の周波数値に応じた値を有する周波数信号を生成する周波数検出器と、位相ずれ信号の値と周波数信号の値とを加算した値を有する制御信号を生成する加算器と、制御信号の値を分周比として、マスタークロックを分周した再生クロックを生成する制御分周部と、を備える。制御分周部における分周比の中心値N(Nは自然数)は、周波数信号の値によって定められることを特徴とする。

(もっと読む)

161 - 180 / 277

[ Back to top ]