Fターム[5J106DD01]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | 波形・レベル変換回路 (375)

Fターム[5J106DD01]の下位に属するFターム

Fターム[5J106DD01]に分類される特許

1 - 20 / 34

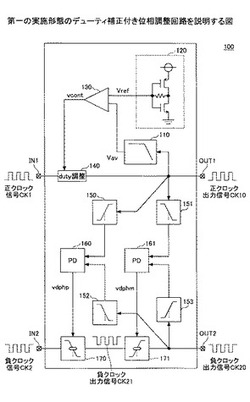

デューティ補正付き位相調整回路及びシリアライザ

【課題】クロックのばらつきが引き起こすジッタを抑制することが可能なデューティ補正付き位相調整回路及びシリアライザを提供することを目的としている。

【解決手段】正クロック信号及び負クロック信号が入力され前記正クロック信号と前記負クロック信号のデューティ及び位相を調整した正クロック出力信号及び負クロック出力信号を出力する。

(もっと読む)

アナログデジタル変換器及び無線受信機

【課題】アナログデジタル変換器のサンプリングクロックのジッタの影響を、低消費電力でデジタル補正する。

【解決手段】アナログデジタル変換器のサンプリングクロックを、サンプリングクロックよりも低周波数かつ低ジッタの基準クロックを源振とする位相同期ループ(PLL)により生成する。サンプリングクロックと基準クロックが同期するタイミングにおけるタイミング誤差を時間デジタル変換器(TDC)によりデジタル値に変換する。なお、基準クロックが存在しないサンプリングタイミングにおけるタイミング誤差については、検出されたタイミング誤差を補間して生成する。これにより、各サンプリングタイミングにおけるサンプリングクロックのジッタ値を取得する。当該ジッタ値からサンプリング電圧誤差を算出し、アナログデジタル変換器の出力をデジタル補正する。

(もっと読む)

周波数制御装置、周波数制御方法、クロック生成回路、電子機器、及び、プログラム

【課題】クロック生成回路におけるハンチング現象を抑制することのできる新たな技術を提供する。

【解決手段】電子機器500は、周波数制御装置510と信号処理部540とを備える。周波数制御装置510は、出力クロック信号を生成するクロック生成回路(クロック生成部512)と、出力クロック信号の周波数を制御する周波数制御部514とを備える。クロック生成部512は、入力された発振制御信号に基づき出力クロック信号を生成する出力クロック生成部(発振部610)と、発振制御信号を生成して出力クロック生成部に供給する発振制御部616とを有する。周波数制御部514は、発振制御部616を制御して発振制御信号を徐々に変化させることにより、出力クロック信号の周波数を徐々に変化させる。

(もっと読む)

PLL周波数シンセサイザ

【課題】位相雑音特性の劣化を回避し消費電力を低減するデジタルPLL周波数シンセサイザを提供する。

【解決手段】デジタルPLL周波数シンセサイザ101において、ロック検出後に第1の発振信号位相情報から、前回の発振信号位相情報と位相差εとから推定部20にて推定した第2の発振信号位相情報に切り替えることにより、通常状態(ロック状態)において誤差を持つ危険を抱えた第1の発振信号位相情報を使用せず、また、従来のリクロックのための高速動作するラッチ回路も不要とする。これにより、位相雑音特性の劣化を回避しつつ、従来に比べて消費電力を低減する。

(もっと読む)

基準信号発振器

【課題】優れた長期安定度を有する高安定発振器を用いた基準信号発振器において、高安定発振器に短時間の障害が発生したときにおいても、継続して安定して基準信号を出力すること。

【解決手段】高安定発振器としてルビジウム発振器やセシウム発振器を用い、これら発振器に比べて長期間の周波数安定度が劣るが、短期間の周波数安定度が高い準安定発振器であるOCXOをバックアップとして用いる。高安定発振器に異常が発生してからの経過時間と、両発振器の使用の重み付け(利用比率)とを対応させたテーブルを用意し、このテーブルを用いることで、高安定発振器が復帰した後、初めは準安定発振器の発振周波数を100%利用するが、その後段階的に準安定発振器の使用の重み付け(利用比率)を小さくし、高安定発振器の利用比率を大きくする。

(もっと読む)

DLL回路およびそれに使用されるレプリカ回路

【課題】 レイアウト的な制限がないDLL回路を提供すること。

【解決手段】 DLL回路に使用されるレプリカ回路は、第1の電源電圧が供給され、クロックバッファへの入力クロック信号が入力され、レプリカクロック信号を出力する遅延回路を含む。遅延回路は、第1乃至第MのCMOSインバータ回路および第(M+1)乃至第NのCMOSインバータ回路が縦続接続された回路である。複数のトランジスタは、遅延回路の後段側の第(M+1)乃至第NのCMOSインバータ回路のnチャネルMOSトランジスタのソースにそれぞれ接続されている。ローパスフィルタ回路は、第1の電源電圧と異なる第2の電源電圧を低域通過濾波して、その低域濾波した電源電圧を複数のトランジスタの制御端子へ供給する。

(もっと読む)

PLL回路

【課題】 安定した位相雑音特性を得ることができるPLL回路を提供する。

【解決手段】 基準発振器4からの基準周波数(Fref)信号のレベルを検波回路7で検出し、制御回路5が、検出したレベルが特定値に比べて小さい場合は可変ATT6の減衰量を小さくし、検出したレベルが特定値に比べて大きい場合は可変ATT6の減衰量を大きくする制御信号を可変ATT6に出力し、可変ATT6では制御回路5からの制御信号に従って基準周波数信号の減衰を行い、PLL IC2への基準周波数信号の入力レベルを安定化させ、位相雑音特性の劣化を防止し、更にアンロックを防止できるPLL回路である。

(もっと読む)

DPLL回路

【課題】入力データに混入したノイズの幅がクロック周期程度にまで大きくなり、ノイズ位置が入力データの中間位置に発生した場合にも、入力データからノイズを除去できる。

【解決手段】1ビットを4クロック幅で構成する入力データからノイズフィルタで雑音を除去し、この雑音を除去した入力データと同期したクロックを生成するDPLL回路において、ノイズフィルタは、入力データに対して、4段縦続接続のシフトレジスタを設け、このシフトレジスタのレジスタ11,12,13のクロック同期した出力の一致・不一致状態に応じて最終段のレジスタ16の入力を切り替える入力ロジック17を設ける。

さらに、ノイズフィルタでは除去しきれない入力データの歪みを歪み除去回路で除去する。

(もっと読む)

半導体装置

【課題】出力ドライバのスイング能力を変化させた場合に生じるリードデータのスキューをキャンセルする。

【解決手段】リードデータDQを外部に出力する出力ドライバ90と、出力ドライバ90のスイング能力を設定するモードレジスタ53とを備える。出力ドライバ90によって駆動されるリードデータDQの遷移開始タイミングは、モードレジスタ53に設定された出力ドライバ90のスイング能力が相対的に大きく設定されている場合には相対的に早められ、モードレジスタ53に設定された出力ドライバ90のスイング能力が相対的に小さく設定されている場合には相対的に遅らせる。これにより、出力ドライバ90のスイング能力に関わらず、リードデータDQがしきい値レベルを超えるタイミングを所望のタイミングに一致させることが可能となる。

(もっと読む)

位相同期回路

【課題】位相誤差および周波数精度等の性能に優れ、かつ低価格で、広い制御電圧入力範囲を持つ電圧制御発振器を利用したPLL回路を提供する。

【解決手段】位相比較器11とチャージポンプ12は、低電圧トランジスタで構成され、電源電圧VLの可変電圧源16と電源電圧VDC(=VL+VCC1)の可変電圧源17から与えられる差の電圧VCC1(例えば、5V)で動作する。チャージポンプ12の出力電流をループフィルタ14で積分して生成された制御電圧VCは、0〜VCC2(例えば、16V)を制御電圧入力範囲とする電圧制御発振器15に与えられる。このとき、制御電圧VCの変化範囲は5V以下となるが、可変電圧源16,17の出力電圧VL,VDCを制御することで変化範囲を0〜16Vに拡大し、電圧制御発振器15から所望の周波数の出力信号OUTを出力させることができる。

(もっと読む)

位相誤差検出装置、位相誤差検出方法、集積回路及び光ディスク装置

【課題】周波数誤差が生じているときでも±180度を越える位相誤差の検出を可能とし、PLLの安定性を向上させることができる位相誤差検出装置を提供する。

【解決手段】アナログ入力信号をサンプリングクロックに基づいてAD変換してデジタル再生信号を生成するAD変換部1の出力より位相誤差を検出する位相誤差検出装置は、AD変換部1の出力より前記位相誤差を生成する位相誤差生成部2と、位相誤差を補正する位相誤差補正部3とを含み、位相誤差補正部3は、過去の位相誤差により位相誤差検出範囲を決定し、位相誤差生成部2が生成した位相誤差が位相誤差検出範囲外であった場合に当該位相誤差を補正する。

(もっと読む)

半導体集積回路

【課題】リアルタイムクロック用の半導体集積回路の消費電力をさらに低減すると共に、生成されたクロック信号を周辺回路においても利用できるようにする。

【解決手段】この半導体集積回路は、外部から供給される電源電圧に基づいて、第1の電源電圧及び第2の電源電圧を生成する定電圧回路と、第2の電源電圧が供給され、発振動作を行うことにより原振クロック信号を生成する発振回路と、第2の電源電圧が供給され、原振クロック信号を分周することにより複数種類の分周クロック信号を生成する分周回路と、第1の電源電圧が供給され、分周回路によって生成される少なくとも1種類の分周クロック信号に基づいて計時情報を管理するロジック回路と、原振クロック信号と所定数の分周クロック信号との内の1つを選択するセレクタ回路と、選択されたクロック信号を出力端子に供給する出力回路とを具備する。

(もっと読む)

位相同期ループの出力VCOにおいて50%デューティサイクルを達成するための方法および装置

【課題】PLLの出力において所望のデューティサイクルを達成するための方法および装置を提供する。

【解決手段】本方法は、制限差動増幅器214を使用して、差動コモンモードクロック信号からデューティサイクルを有するシングルエンドクロック信号を発生させるステップと、シングルエンドクロック信号213のデューティサイクルに応じて差動バイアス電流信号229、230を発生させるステップと、差動バイアス電流信号を制限差動増幅器に与えることによって、シングルエンドクロック信号のデューティサイクルを所望のデューティサイクルに修正するステップとを含む。CML−CMOS変換器回路は、制限差動増幅器214と、シングルエンドクロック信号のデューティサイクルの測定値を発生するための低域フィルタと、(i)測定値を基準電圧と比較し、(ii)比較に応じて差動バイアス電流信号を発生するための第2の差動増幅器とを含む。

(もっと読む)

PLL制御装置及びPLL制御方法

【課題】大規模なPLCシステムに用いても、PLLの受信ダイナミックレンジ拡大、雑音耐力向上が実現でき、アナログ素子の特性のバラツキなどに影響されずに安定して動作し、広範囲な安定したジッタ特性が得られるようにする。

【解決手段】PLL制御装置は、入力信号からタイミング位相ベクトル信号を抽出するタイミング抽出回路と、供給される制御係数に基づき基準信号の位相及び/又は発振周波数を制御するVCXOと、タイミング位相ベクトル信号の位相及び位相差に基づき制御係数を出力する2次PLL回路とを備える。この2次PLL回路は、タイミング位相ベクトル信号に基づき制御係数を発生する制御係数発生回路と、制御計数発生回路からの制御係数につき6dB単位での対数軸上におけるレベル調整を行う第1のレベル調整回路と、第1のレベル調整回路からの制御係数について±6dBレベルの微調整を行う第2のレベル調整回路とを有する。

(もっと読む)

PLL方式発振回路、ポーラ送信回路及び通信機器

【課題】VCO101の変調感度のばらつきを低減し、高速、高精度に所望の出力振幅を得ることができるPLL方式発振回路を提供する。

【解決手段】振幅検出器103は、VCO101の出力振幅を検出する。振幅制御部105は、振幅検出器103が検出したVCO101の出力振幅が所望の振幅になるように可変電流源109の電流値を制御する。LPF108は、振幅制御部105と可変電流源109との間に接続される。スイッチ107は、LPF108を振幅制御部105と可変電流源109との間に接続するか否かを切り替える。振幅制御部105は、LPF108又は切り替えスイッチ107のいずれか一方を介して、可変電流源109と接続される。

(もっと読む)

パルス発生回路及びパルス発生回路を備えた電子機器

【課題】PVTに依存せずに安定した周波数を出力する。

【解決手段】出力する第1の出力信号Vf1の周波数を第1の制御電圧VC1で制御する第1の電圧制御発振器11と、第1の出力信号Vf1及び基準信号CLKに基づき第1の出力信号Vf1の周波数を一定に維持する第1の制御電圧VC1を生成する制御電圧生成部13と、を含む位相同期回路10と、出力する第2の出力信号Vf2の周波数を第2の制御電圧VC2で制御する第2の電圧制御発振器20と、第1の制御電圧VC1に基づき第2の出力信号Vf2の周波数を一定に維持する第2の制御電圧VC2を生成する制御電圧変換部30と、を含むパルス発生回路1。

(もっと読む)

電圧制御発振器及びこれを用いた位相同期回路

【課題】インバータセルを構成するMOSトランジスタが飽和領域のみならず、線形領域で動作する場合にも位相雑音を低減する。

【解決手段】ダミーインバータセル110からの信号と、基準信号との電位差を増幅した増幅信号を出力する演算増幅器120と;第2MOSトランジスタ102に接続され、増幅信号を受ける第1MOSトランジスタ101と、インバータ入力部及びインバータ出力部として機能する第2MOSトランジスタ102及び第3MOSトランジスタ103と、第3MOSトランジスタ103に接続され、発振信号の周波数を制御するための制御信号を受ける第4MOSトランジスタ104とを含むインバータセル100を環状に接続したリング・オシレータと;インバータセル100と同一の構造を備え、インバータ出力部がインバータ入力部に短絡されたダミーインバータ110と;を具備する。

(もっと読む)

同期損失防止方法及び同期損失防止装置

【課題】CDR回路側の原因による接続ノード間の同期化の非成立を抑制し、接続失敗を抑制することができる同期損失防止方法及び同期損失防止装置を提供する。

【解決手段】受信データから同期化クロックを生成するCDR(Clock Data Recovery )回路と、受信データの受信開始から同期化検出時間Nを経過しても同期化クロックに基づく接続ノード間の同期化が非成立のときに、接続失敗処理を行う接続失敗処理段階(S15)と、受信データの受信開始から同期化リトライ判定時間(N/2)を経過しても同期化クロックに基づく接続ノード間の同期化が非成立のときに、CDR回路の動作を補正処理する補正処理段階(S13)とを備える。

(もっと読む)

位相差検出回路、PLL回路、位相差検出方法及び位相差検出プログラム

【課題】 ゼロクロスポイント検出用のハードを用いることなく、位相差の検出機能を実現する。

【解決手段】 位相差検出回路は、検出信号と内部基準信号の位相差を検出するための回路であって、d−q軸変換ユニット5と、1周期全加算ユニット6と、位相差算出ユニット7とを備えている。d−q軸変換ユニット5は、内部基準信号を用いて検出信号をd−q軸変換することで、瞬時値有効分dと瞬時値無効分qとを算出する。1周期全加算ユニット6は、瞬時値有効分dを1周期全加算することで有効分Dを算出して、さらに瞬時値無効分qを1周期全加算することで無効分Qを算出する。位相差算出ユニット7は、有効分Dと無効分Qを用いて位相差を算出する。

(もっと読む)

電圧制御発振回路

【課題】電圧電流変換部の制御電圧入力用MOSトランジスタにデプレッション型を使用した際に発生する発振周波数(バイアス電流)オフセットの製造プロセスばらつきが補正された電圧制御発振回路を提供する。

【解決手段】電圧制御発振回路1は、制御力電圧がゲートに入力される第1のデプレッション型MOSトランジスタ13と、その第1のデプレッション型MOSトランジスタ13のゲート・ソース間電圧が0Vのときのオフセットを補償する第2のデプレッション型MOSトランジスタ15を有し、制御電圧に応じたバイアス電流を発生する電圧電流変換回路3を備える。

(もっと読む)

1 - 20 / 34

[ Back to top ]