Fターム[5J106DD11]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | 合成・分配回路 (405)

Fターム[5J106DD11]の下位に属するFターム

Fターム[5J106DD11]に分類される特許

1 - 20 / 42

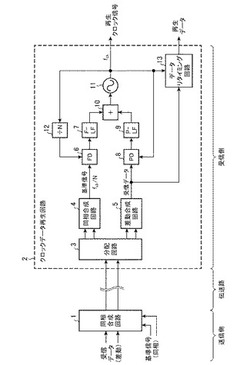

信号伝送システム、信号送信装置およびクロックデータ再生回路

【課題】良好な通信品質で、高速な位相同期ループを得る。

【解決手段】送信側は、一方が差動信号であり他方が同相信号であるデータ信号および基準信号を同相合成し、一対の伝送路を通じて伝送する同相合成回路1を備え、クロックデータ再生回路2は、同相合成回路1からの信号からデータ信号および基準信号を分離する信号分離手段(分配回路3、同相合成回路4および差動合成回路5)と、データ信号と位相が同期した再生クロック信号を生成する再生クロック信号生成手段(位相比較回路8、位相同期ループ用ループフィルタ9および電圧制御発振器11)と、再生クロック信号を分周し、当該分周した信号の周波数を基準信号の周波数に同期させる制御信号を生成し、当該制御信号により再生クロック信号の周波数を制御する再生クロック信号収束手段(周波数比較回路6、周波数同期ループ用ループフィルタ7、電圧制御発振器11およびN分周回路12)とを備えた。

(もっと読む)

発振回路およびそれを用いた電子機器

【課題】スペクトルのピークを抑制する。

【解決手段】発振回路2は、基準クロック信号CKREFを受け、出力クロック信号CKOUTを生成する。プログラマブル分周器18は、その分周比が少なくとも2値で切りかえ可能に構成され、出力クロック信号CKOUTを設定された分周比で分周し、分周クロック信号CKDIVを生成する。位相比較器10は、基準クロック信号CKREFと分周クロック信号CKDIVの位相差に応じた位相差信号S1を生成する。ループフィルタ12は、位相差信号S1を平滑化する。VCO(電圧制御発振器)14は、ループフィルタ12から出力される位相差信号S2に応じた周波数で発振し、出力クロック信号CKOUTを生成する。制御部20は、プログラマブル分周器18の分周比を、時分割的に切りかえることにより出力クロック信号CKOUTのスペクトルを拡散させる。

(もっと読む)

半導体集積回路装置、及び、クロックデータ復元方法

【課題】インターポレータ方式のクロックデータ復元回路において、インターポレータ回路の広帯域化を行わず、マルチレートに対応したクロックデータ復元回路を実現する。

【解決の手段】インターポレータ回路の生成クロックを分周し、リカバリクロックを生成する。また、インターポレータ回路が生成するクロックの位相を制御するポインタは分周前のクロックを使い、その他の回路は分周後のリカバリクロックを使い動作する。

(もっと読む)

信号処理回路

【課題】内部回路の内部クロックと内部回路の入力信号との位相関係により内部回路の出力が変動する場合であっても、安定した回路動作とすることができる信号処理回路を得る。

【解決手段】入力信号と位相制御信号とを受け、前記入力信号及び前記位相制御信号の位相差に基づき位相比較信号を出力する位相比較手段と、前記位相比較信号を受け、前記位相比較信号に基づく周波数で発振する発振信号を出力する発振手段と、前記発振信号を受け、前記位相制御信号を出力する位相制御信号発生手段とを備え、同時に前記位相制御信号を出力信号とし、該位相制御信号を内部クロックとして供給することを特徴とする位相差制御回路である信号処理回路等を提供する。

(もっと読む)

信号多重化回路

【課題】データ信号とクロック信号との位相関係を適応的に制御できる信号多重化回路を提供する。

【解決手段】信号多重化回路は、第1のクロック信号の第1の位相位置に同期したデータ遷移をする第1のデータ信号と第1のクロック信号の第1の位相位置から180度位相がずれた第2の位相位置に同期したデータ遷移をする第2のデータ信号とを受け取り、第2のクロック信号に応じて第1及び第2のデータ信号を順次選択して出力するセレクタ回路と、第1及び第2のデータ信号と第1及び第2のクロック信号とに基づいて、第2のクロック信号とデータ遷移との位相関係を示す位相制御信号を出力する位相検出器と、位相制御信号に応じて位相関係を制御する位相制御器とを含む

(もっと読む)

PLL回路

【課題】ループフィルタの回路面積を削減すると共に、電圧制御発振器の動作の安定化やノイズ感度の低減が可能なPLL回路を提供することである。

【解決手段】本発明のPLL回路は、位相比較器3の出力信号に応じて出力電圧を制御する第1及び第2のチャージポンプ回路4、5と、第1のチャージポンプ回路4の出力に基づく信号から所定の周波数成分が除去された第1の電圧信号を出力する第1のフィルタ6と、第2のチャージポンプ回路5からの電流を入力し、所定の一定電圧を第2の電圧信号として出力する第2のフィルタ7と、第1のフィルタ6からの第1の電圧信号と基準電圧との比較結果に基づき第3の電圧信号を出力する電圧制御部30と、第1及び第2の電圧信号を低ゲイン入力、第3の電圧信号を高ゲイン入力とし、当該第1乃至第3の電圧信号に基づき発振周波数を生成する電圧制御発振器10を備える。

(もっと読む)

集積回路、集積回路システム、シリアルパラレル変換装置およびスキュー調整方法

【課題】簡単な回路または簡単な処理によりスキュー調整する。

【解決手段】集積回路3は、入力された外クロック信号を遅延させた内クロック信号を出力するクロック遅延回路43と、入力されたデータ信号を内クロック信号によりラッチするラッチ回路45と、クロック遅延回路43に対して、外クロック信号に対する内クロック信号の遅延量として、複数の遅延量を設定する遅延量設定回路58と、複数の遅延量それぞれの設定の下でのラッチ回路45の出力信号を判定するラッチ判定回路52と、ラッチ判定回路52による複数の遅延量それぞれについての複数の判定値を記憶する記憶部53と、記憶部53に記憶された複数の判定値とクロック遅延回路43に設定した複数の遅延量との関係から、クロック遅延回路43による内クロック信号の遅延量を取得する遅延量取得部とを有する。

(もっと読む)

クロック供給装置

【課題】運用系および待機系システムクロックの位相を、バックボード間の配線遅延量、温度変化および電圧変動に起因するバッファ遅延の変化量を含め一致させたシステムクロック供給装置を提供する。

【解決手段】システムクロック1に位相同期した運用系および待機系システムクロック6を出力する冗長構成とされた運用系および待機系システムクロック供給部200と運用系および待機系システムクロックを装置内各部へ分配するためのバックボード8を有する。システムクロック1に位相同期したクロック22を生成するPLL210は、運用系システムクロックを基準とし、待機系システムクロックの位相を制御する位相差調整部211を含んだ構成とする。

(もっと読む)

半導体装置

【課題】リード動作時における位相調整精度を低下させることなく、DLL回路の消費電力を低減する。

【解決手段】ODT機能を有するデータ入出力回路80と、データ入出力回路80の動作タイミングを規定する内部クロックLCLKを生成するDLL回路100とを備える。DLL回路100は、内部クロックLCLKを高精度に位相制御する第1のモードと、低消費電力で動作する第2のモードとを有し、データ入出力回路80がODT動作を行っていない場合には第1のモードで動作し、データ入出力回路80がODT動作を行っている場合には第2のモードで動作する。このように、ODT動作の有無によってDLL回路100の動作モードを切り替えていることから、厳密な位相制御が不要なODT動作時における消費電力を低減することが可能となる。

(もっと読む)

水晶発振器

【課題】実装スペースとコストの更なる低減のため、電子機器内の水晶部品を1つに集約するためには、消費電流や周波数精度の問題があった。

【解決手段】本発明の水晶発振器は、音叉型水晶振動体と、この振動体の温度による発振周波数の変化を、時間領域で連続的に補正するための温度補償回路を含んだ発振回路とを備え、この発振回路の出力を源振として高周波クロック信号を出力する、複数のPLL(フェイズロックループ)回路を備える。このような構成にすることにより、電子機器内で必要とされる全てのクロック信号を、精度良く提供することができる。

(もっと読む)

DLL回路及びこれを備える半導体装置

【課題】エイリアシングによるエイリアシングによる誤動作の発生が防止されたDLL回路を提供する。

【解決手段】外部クロック信号CLKを遅延させることによって内部クロック信号LCLKを生成するディレイライン110と、ディレイライン110の遅延量を設定するカウンタ回路130と、外部クロック信号CLKの位相に基づいて位相判定信号PD0を生成する位相検出回路140と、外部クロック信号CLKに含まれるジッタ成分が所定の周波数以上であることに応答して、位相判定信号PDに基づいたカウンタ回路130のカウント値の更新を禁止するアンチエイリアス回路200とを備える。これにより、エイリアシングによる誤動作によって内部クロック信号LCLKが誤った方向に連続制御されるという問題がなくなる。

(もっと読む)

DLL回路及びその制御方法

【課題】冗長な回路、配線を不要とし、回路規模の増大を回避し、デューティを変更可能とするDLLを提供する。

【解決手段】外部信号の第1遷移(Rise)を可変に遅延させる第1可変遅延回路(10R)と、外部信号の第2遷移(Fall)を可変に遅延する第2可変遅延回路(10F)と、第1可変遅延回路(10R)の出力信号と第2可変遅延回路(10F)の出力信号とを合成する合成回路(13)と、合成回路(13)の出力信号のデューティの変更と検出を行うデューティ変更検出回路(21)と、デューティ変更検出回路(21)のデューティ検出結果(DCC)に従って第1可変遅延回路(10R)又は第2可変遅延回路(10F)の遅延を可変させる遅延制御回路(15R、15F)と、を備える。

(もっと読む)

DLL回路及びその制御方法

【課題】クロックのパルス幅が狭い場合、及び広い場合において、合成回路の誤動作を回避し、動作周波数の高速化に対応可能とするDLLの提供。

【解決手段】外部クロック(CK)の第1遷移(Rise)に対応して互いに異なる遅延時間の信号を出力し、CKの第2の遷移(Fall)に対応して互いに異なる遅延時間の信号を出力する第1の可変遅延回路20と、第1の可変遅延回路からの信号をそれぞれ受ける第2の可変遅延回路10R、10Fからの出力信号を合成して出力する第1の合成回路30とを備え、第2の可変遅延回路は第1の可変遅延回路からの信号からワンショットパルスを生成するワンショットパルス生成回路と、リセット端子を備えるラッチ回路と、ラッチ回路のセット出力の遷移エッジを受け、所定の比率で合成した信号を出力する第2の合成回路と、を備え、第2の合成回路の出力がラッチ回路のリセット端子に入力される。

(もっと読む)

水晶発振回路

【課題】 複数の異なる周波数信号を出力可能で、消費電力を低減し、構造が簡易で小型化できる水晶発振回路を提供する。

【解決手段】 電圧制御水晶発振器(VCXO)2からの出力を分周比に応じて分周器3で分周し、分周された信号とVCXO2から出力された信号を合成器4で合成し、予め分周比に応じて通過帯域が定められた複数のBPF5に出力し、該当するBPFのみが特定の周波数帯域の信号を通過させ、PLL6で位相制御が為されて、所望の周波数信号を出力する水晶発振回路である。

(もっと読む)

クロック生成回路

【課題】ロングタームジッタを正確に評価し、回路の誤動作を未然に防ぐ。

【解決手段】第1オシレータ10は、基準クロックCKrefを生成する。PLL回路14は、第1オシレータ10からの基準クロックCKrefにもとづいて出力クロックCKoutを生成する。異常発振監視部20は、基準クロックCKrefを分岐して受け、基準クロックCKrefの周期の整数倍の所定時間経過後にアサートされる基準タイミング信号S1を生成する。異常発振監視部20は、出力クロックCKoutのエッジのタイミングが基準タイミング信号S1のエッジに応じて規定される所定の範囲から逸脱するとき、異常検出信号S2をアサートする。

(もっと読む)

光学系及び原子発振器

【課題】信号強度の揃ったEIT信号を得てS/Nを向上させた光学系を提供する。

【解決手段】共鳴光3aを出射するコヒーレント光源3と、コヒーレント光源3の出射側に配置されガス状の金属原子を封入すると共に、金属原子ガス中に共鳴光3aを透過させるガスセル9と、ガスセル9を透過した光3bを複数の光に分散して再びガスセル9に導く導光手段11と、導光手段11により導かれガスセル9を再び透過した複数の光4b〜7bを検出する光検出器4〜7と、ガスセル9を所定の温度に加熱するヒータ8、10と、光検出器4〜7から検出された信号を合成する合成回路2と、合成回路2の出力信号により、発振周波数を制御する周波数制御回路12と、を備えて構成されている。

(もっと読む)

光学系及び原子発振器

【課題】複数の受光素子を発光素子と同一側に併置し、複数の受光素子を電気的に接続するボンディングワイヤを短くしてモジュール実装を容易とし、且つEIT信号レベルを大きくしてS/Nを改善した光学系を備えた原子発振器を提供する。

【解決手段】この光学系1は、共鳴光3を出射するコヒーレント光源2と、コヒーレント光源2の出射側に配置され共鳴光3を少なくとも2つの光路5、6に導く導光手段4と、導光手段4の出射側に配置されガス状の金属原子を封入すると共に、この金属原子ガス中に導光手段4により導かれた共鳴光5、6を通過させるガスセル7と、ガスセル7を通過した各共鳴光5、6を夫々検出する光検出器(光検出手段)10、11と、光検出器8、9から検出された信号を合成する合成回路10と、合成回路10の出力信号により、発振周波数を制御する周波数制御回路11と、を備えて構成されている。

(もっと読む)

通信装置、発振器、並びに周波数シンセサイザ

【課題】CDMAやOFDMといった大きな包絡線変動を伴う変調方式を使用することができ、送信機に線形性と高効率を両立するLINC送信機を提供する。

【解決手段】変調データの周波数変換を行なうPLLにおいて2ポイント変調方式を採用することで、発振器に入力される変調データはPLLにとって外乱とは見えなくなり、PLLのループ帯域幅に制限されない広帯域変調を実現することが可能となる。また、発振器の積分効果により、サンプリング周波数付近におけるレプリカを、アナログ・スムージング・フィルタを追加することなく大幅に抑制することができ、回路のリコンフィギャラビリティを高めることができる。

(もっと読む)

ゲート時間/デジタル変換器を有するデジタル位相ロックドループ

デジタルPLL(DPLL)、時間/デジタル変換器(TDC)および制御ユニットを含む。TDCは、位相情報を量子化するために、短い時間の間、周期的に有効され、電力消費を削減するために、残り時間の間、無効にされる。TDCは、第1のクロック信号と第1の基準信号を受信し、第1のクロック信号と第1の基準信号との位相差を示す出力をTDCに提供する。制御ユニットは、主基準信号に基づいてイネーブル信号を生成し、イネーブル信号でTDCを有効および無効にする。ある設計において、制御ユニットは、第1の基準信号および第2の基準信号を獲得するために、主基準信号を遅らせ、主基準信号および第2の基準信号に基づいてイネーブル信号を生成し、TDCに対する第1のクロック信号を獲得するために、イネーブル信号で主クロック信号をゲートする。 (もっと読む)

遅延固定ループ

【課題】ノイズの干渉、PVTの変動、及び頻繁に起こるパワーダウンモードへの進入・脱出など、半導体メモリ素子の最悪の状況でも安定的に動作できる遅延固定ループを提供すること。

【解決手段】遅延固定をなすために、ソースクロックの第1のクロックエッジ及び第2のクロックエッジに対応する第1の遅延クロック及び第2の遅延クロックを生成する遅延固定部と、前記第1の遅延クロックと第2の遅延クロックとの位相差を検出して加重値選択信号を出力する位相検出部と、前記第1の遅延クロックと第2の遅延クロックとの遅延固定時点から予定された期間に獲得した前記加重値選択信号を格納する加重値格納部と、該加重値格納部に格納された加重値選択信号に対応する加重値を反映し、前記第1の遅延クロックの位相と第2の遅延クロックの位相とを混合して遅延固定ループクロックとして出力する位相混合部とを備えることを特徴とする。

(もっと読む)

1 - 20 / 42

[ Back to top ]