Fターム[5J106DD13]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | 合成・分配回路 (405) | 加算・減算回路 (265)

Fターム[5J106DD13]に分類される特許

201 - 220 / 265

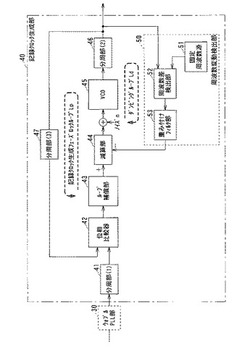

情報記録再生装置、およびその記録クロック生成方法

【課題】ウォブル信号に同期して生成される記録クロックの周波数安定化を簡素な構成で実現することができる情報記録再生装置を提供する。

【解決手段】本発明に係る情報記録再生装置は、光ディスクに記録クロックを用いてデータを記録する情報記録再生装置において、光ディスクの再生信号から抽出されるウォブル信号によるフェーズロック制御に基づいて周波数制御され、記録クロックの発振源となるVCOと、VCOの周波数変動量を検出する周波数変動検出部と、を備え、VCOは、フェーズロック制御に基づく周波数制御に加えて、周波数変動検出部にて検出される周波数変動量に基づいて周波数制御される、ことを特徴とする。

(もっと読む)

PLL回路

【課題】複数の位相誤差出力をもつ特殊なVCOを備えること無しに、間欠的に記録され、データの先頭部に同期引き込みパターン領域を有するデータに対し、高速での引き込みを可能とするPLL回路を提供する。

【解決手段】PLL回路において、ADコンバータ4と、ADコンバータ4の出力信号から位相誤差を算出する位相比較器5と、周波数系フィルタ6と、位相系フィルタ7と、所定のタイミングで位相比較器5で算出された位相誤差の読み取りを行い、その読み取り値に応じた出力を発生する位相誤差読み取り手段8および位相誤差変換手段9と、周波数系フィルタ6の出力、位相系フィルタ7の出力、および位相誤差変換手段9の出力を加算する加算器10と、DAコンバータ11と、DAコンバータ11の出力電圧に基づいてADコンバータ4のサンプリングクロックとして使用される発振出力を出力するVCO12とを備えた。

(もっと読む)

位相比較回路およびそれを用いたPLL周波数シンセサイザ

【課題】高速に周波数切り換えが可能であり、且つ小型でスプリアスを低減することが可能な位相比較回路を提供する。

【解決手段】本発明の一実施形態に係る位相比較回路は、制御回路からの制御信号に基づいて、クロックを分数分周した分数分周信号を生成する分数分周器と、分数分周信号を整数分周した第1の整数分周信号を生成する第1の整数分周器と、基準クロックを整数分周した第2の整数分周信号を生成する第2の整数分周器と、切換信号に基づいて、分数分周信号と第1の整数分周信号とのいずれか一方を選択的に出力する第1の選択回路と、制御回路からの切換信号に基づいて、基準クロックと第2の整数分周信号とのいずれか一方を選択的に出力する第2の選択回路と、第1の選択回路からの出力信号と第2の選択回路からの出力信号との周波数差および位相差を表す比較信号を生成する位相比較器とを備えている。

(もっと読む)

デジタルPLL回路及びそれを備えた光ディスク装置

【課題】動作周波数が低く、安価にIC化を行うことができ、設計が容易なデジタル回路を用いて時間分解能の高いクロック信号を生成することができるDPLL回路を備えた光ディスク装置を提供する。

【解決手段】デジタルPLL回路部は、エッジ検出回路部と、クロックデータ生成回路部と、位相差検出回路部とを備え、一周期毎に、デジタルクロックデータから、デジタルクロック信号の立ち上がりエッジ又は立ち下がりエッジの有無を時間分解能単位で示した書き込みタイミング信号を生成して出力する。

(もっと読む)

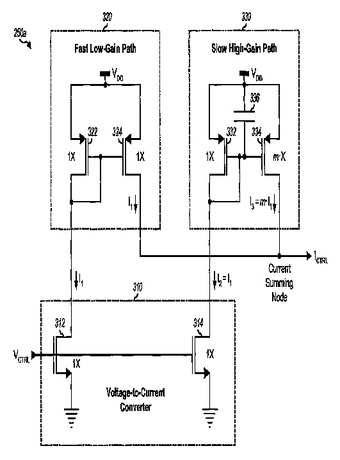

電流−モード利得分割デュアル−パスVCO

大きな電圧制御オシレータ(VCO)利得を効率的に取り扱うための技術が記載される。本技術は、(1)VCOの中心周波数を調節する平均制御電流を供給するための低速高利得パス、及び(2)通常動作の間VCO周波数を調節する瞬間的な制御電流を供給するための高速低利得パス、を利用する。1つのデザインでは、VCOは、電圧−電流コンバータ、電流増幅器、総和器、及び電流制御オシレータ(ICO)を含む。電圧−電流コンバータは、制御電圧を受け取り、そして第1電流と第2電流とを発生する。電流増幅器は、第1電流を増幅しそしてフィルタし、そして第3電流を発生する。総和器は、第2電流と第3電流を合算し、そして制御電流を発生する。ICOは、制御電流を受け取り、そして制御電流により決定される周波数を有するオシレータ信号を発生する。  (もっと読む)

(もっと読む)

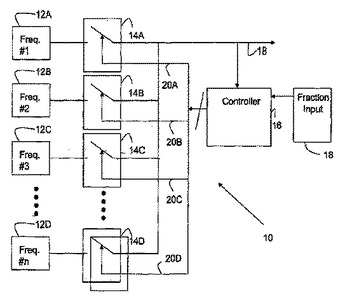

高速スイッチングのための周波数合成の新規方法

単一のソースの設計、マルチプレクサの設計、分数分周器の設計、または周波数逓倍器と周波数分周器の設計で実装可能なデジタル周波数シンセサイザである。実装は、制御器のディザリング回路またはデルタシグマ変調器を利用可能である。この周波数シンセサイザは、CMOS構成において実装可能であり、クリーンアップ位相ロックループ(PLL)を利用可能である。  (もっと読む)

(もっと読む)

発振回路

【課題】従来技術よりも正確な位相差を得ることができる発振回路を提供する。

【解決手段】複数のオペアンプ20−1〜20−4をループ状に直列に接続して構成されるリング発振回路202を含み、複数のオペアンプ20−1〜20−4における複数の出力信号を加算合成して第1の出力信号Vout1として出力すると共に、複数のオペアンプ20−1〜20−4における残りの総ての出力信号を加算合成して第2の出力信号Vout2として出力することによって上記課題を解決することができる。

(もっと読む)

スペクトラム拡散クロック発生回路

【課題】従来のスペクトラム拡散クロック発生回路では、回路内で前もって設定された複数値の拡散率の中に、他に及ぼす電磁ノイズ(EMI)の影響を最も良好に遮断できる拡散率が無い可能性が生じ、スペクトラム拡散クロック発生回路のEMI対策効果が不十分となる虞がある。

【解決手段】基準クロック信号と帰還クロック信号の位相差を検出する周波数位相比較器と、この位相差に応じて充電又は放電信号を発生するCPと、この充電信号に応じた差信号を発生する充放電回路と、電圧制御発振器を具備するスペクトラム拡散クロック発生回路において、上記スペクトラム拡散変調回路は、制御電圧VC値を可変させることで複数の異なる振幅で変化するスペクトラム拡散アナログ電圧信号を発生する変調器と、差信号にスペクトラム拡散アナログ電圧信号を加算する電圧加算器とを具備するスペクトラム拡散クロック回路。

(もっと読む)

クロック再生装置、データ受信装置

【課題】 原クロックの周波数に対して再生クロックの周波数が定常的に大きいあるいは小さいという状況が継続しないようにしたクロック再生装置を提供する。

【解決手段】 クロック再生装置は、送信装置から受信中のデータから原クロック情報を取得する信号検出器101と、再生クロックを出力するVCXO111と、信号検出器101にて取得した原クロック情報の中から、同期合わせに用いる同期合わせ用クロック情報として原クロック情報を選択する信号選択器102とを備える。VCXO111は、原クロック情報から求められる同期合わせ用クロック情報の間隔と、再生クロックにより計測される同期合わせ用クロック情報の取得時間の間隔との差を、同期合わせ用クロック情報の間隔で除した値に基づいて制御される。信号選択器102は、再生クロックが原クロックに近づくに従って、同期合わせ用クロック情報を選択する頻度を低くする。

(もっと読む)

周波数シンセサイザ

【課題】ロックさせる周波数の制御精度と処理速度とを共に擬制にすることなく、PLL回路の構成を1つの半導体チップに集積できるようにする。

【解決手段】アップ/ダウンカウンタ5を用いた第1のロックループによって局部発振周波数の粗調整を行うとともに、S/H回路11を用いた第2のロックループによって局部発振周波数の微調整を行うことにより、位相差に応じてコンデンサに電荷をチャージしたりポンプしたりする動作を不要とし、大容量のコンデンサを用いるLPFを周波数シンセサイザから省略できるようにする。また、S/H回路11を用いた微調整によって局部発振周波数を精度良くロックさせることができるようにするとともに、ロックさせる周波数の制御精度を上げるためにアップ/ダウンカウンタ5のビット数を大きくする必要をなくし、局部発振周波数を所望の周波数に高速にロックさせることができるようにする。

(もっと読む)

キャリア位相同期回路およびキャリア位相同期方法

【課題】 キャリア位相スリップの影響を低減する。

【解決手段】 キャリア位相変動成分を補償する1次ループと、初期位相推定回路と、1次ループの周波数引き込み終了後に、初期推定位相に第1の係数を乗じた値をループフィルタの初期値として設定し、位相検出回路の検出位相と第2の係数の乗算値をループフィルタで積分した結果を加算回路で加算して可変発振回路に入力する制御信号とする2次ループとを備えたキャリア位相同期回路において、初期位相推定回路は、位相検出回路の検出位相を所定の時間間隔で平均する移動平均回路と、移動平均回路から出力される移動平均位相を所定の抽出タイミングでサンプリングする抽出回路と、抽出回路で得られる異なる抽出タイミングにおける複数の移動平均位相サンプリング値を所定の制御タイミングで平均化し、初期推定位相として出力する選択制御手段とを備える。

(もっと読む)

マルチパス角度変調器の利得を常時較正する方法

マルチパス角度変調は、メイン制御ループに追加されたクローズドの二次ループを含み、高周波利得に関して較正ファクタを自動的に調整する。メイン制御ループは、主要パスとして角度変調信号の低周波部分を処理するように構成され、二次ループは、補助ループとして角度変調信号の高周波部分を処理するように構成されている。二次ループは較正情報を検知し、システムが主要動作を行っている間、較正情報を用いて変調ループ内で常時利得をリアルタイムで較正する。その結果、中断時間などのシステム停止または較正に特異的なタイミングが必要でなくなり、変調パスのバランスがとれる。較正は背景プロセスとして常時行われる。角度変調はすべての変調タイプのシステムに適用可能である。 (もっと読む)

遅延ロックループ回路、タイミング発生器、半導体試験装置、半導体集積回路及び遅延量校正方法

【課題】 遅延量の測定に代わる手法で、カウンタの初期設定値を決めて、遅延回路の校正にかかる時間を短縮可能とする。

【解決手段】 複数のカウンタ設定値の中から一つのカウンタ設定値がロードされ、遅延ロックループ回路10−1がロックモードに切り替えられ、サイクルスリップ検出回路20−1の順序回路22がリセットされ、その後、順序回路22から出力されるサイクルスリップ検出信号が読み込まれると、このサイクルスリップ検出信号にもとづき、遅延回路11の出力信号がサイクルスリップを起こしているか否かが判定され、起こしているときはカウンタ設定値が切り替えられ、一方起こしていないときは、ロックされて完了する。

(もっと読む)

位相同期装置、方法、及び、光ディスク装置

【課題】高速引込みが可能なPLL回路を備えた位相同期装置を提供する。

【解決手段】PLL回路17が非同期状態になると、最大符号反転間隔計測器18は、PRML検出器16が出力する識別データ中の符号反転間隔の最大値を計測する。第1のチャネル周波数推定器19は、符号反転間隔の最大値に基づいて、チャネル周波数を推定し、推定チャネル周波数fdet_Tを出力する。PLL回路17は、中心周波数を、推定チャネル周波数fdet_Tに設定する。その後、sync間隔計測器20は、識別データからsync間隔を計測する。第2のチャネル周波数推定器21は、計測されたsync間隔に基づいてチャネル周波数を推定し、推定チャネル周波数fdet_Sを出力し、PLL回路17は、中心周波数を、推定チャネル周波数fdet_Sに設定する。

(もっと読む)

遅延固定ループ

【課題】DCCを可能とする遅延固定ループにおいて、ロックの後、電源電圧値の変化に応じ、DCCの立ち上がりクロック及び立ち下がりクロックの位相差が特定遅延以上となるとき、遅延固定ループをリセットするようにし、遅延固定ループの動作上の問題を解決する遅延固定ループ装置を提供を課題とする。

【解決手段】第1クロックと第2クロックとをそれぞれ受信するデューティサイクル補償部を有する遅延固定ループと、クロックのロック後の電源電圧の変動に応じて前記第1クロック及び第2クロックの位相差が予定された遅延値以上の場合、前記遅延固定ループをリセットするリセット制御部とを備える遅延固定ループ装置を提供する。

(もっと読む)

位相同期ループ回路、位相同期ループ回路のループフィルタゲイン制御方法並びに再生装置

【課題】 ディジタルPLLのループフィルタゲインを自動制御することで、キャプチャ時間の短縮、エラーレートの改善を実現する位相同期ループ回路を提供する。

【解決手段】 ロックモード生成回路29は、イコライザ10からの周波数調整再生信号(e)とビタビ復号器12からのSAM値と補間フィルタ24からのフィルタ出力である同期がとれた再生信号(f)とに基づいて、上記ループフィルタ19の自動調整ゲインKp_auto及びKi_autoを出力する。

(もっと読む)

周波数制御装置及び周波数制御方法

【課題】クロック信号の周波数を目標とする周波数(目標とする周波数のキャプチャレンジ)に安定して到達させることが可能な周波数制御装置を提供すること。

【解決手段】周波数制御装置は、回転する光ディスクから読み取られた信号に基づきクロック信号を生成する生成手段と、前記生成手段により生成されたクロック信号のドリフト量を検出する検出手段と、前記検出手段により検出されたドリフト量に基づき前記クロック信号の周波数を補正する補正手段とを備えている。

(もっと読む)

スペクトル拡散クロック発生器を自動的に補正する方法と装置

【課題】位相ロックループ回路内の受動素子値およびシステム利得およびチャージポンプ電流の変動を自動的に補正するスペクトル拡散クロック発生器回路を提供する。

【解決手段】位相周波数検出器122のUPおよびDOWN信号124、126のパルス幅を特定の間隔で監視し、標準パルス幅持続時間と比較して、これらのUPおよびDOWN信号124、126の偏差誤差を判別する。パルス幅持続時間の実際の値で誤差を測定した後、誤差信号の大きさと方向に応じて位相ロックループ回路100を調整する。位相ロックループ利得パラメータ、特に電圧制御発振器134の利得およびチャージポンプ電流に変化があると、位相周波数検出器122の出力に著しい影響が出て、スペクトル拡散プロファイルに沿って周波数が変化するときにUPおよびDOWN信号124、126の幅が変動する。

(もっと読む)

PLL回路およびPLL回路を備える半導体装置

【課題】回路規模も小さく簡単にジッタ成分を含んだクロックを生成するPLL回路を提供する。

【解決手段】位相比較器11は、入力される参照クロック信号CKRと分周器14からフィードバックされる信号との位相を比較して位相差に応じた出力信号をフィルタ部12に出力する。フィルタ部12は、位相比較器11の出力信号の低周波成分を検出して電圧制御発振器13に出力する。電圧制御発振器13は、フィルタ部12の出力電圧に基づいて制御される発振周波数の発振信号を出力信号CKFとして発生する。分周器14は、出力信号CKFを分周して位相比較器11に出力する。配線部15は、外部からノイズを誘導してフィルタ部12の出力信号に加算するように配線部15の配線の一端Qをフィルタ部12の出力Pに接続する。電圧制御発振器13が発生する出力信号CKFの発振周波数がノイズによって揺らぐ。

(もっと読む)

位相同期ループ回路での周波数検出器及び周波数エラーの検出方法

【課題】 位相同期ループ回路において周波数エラーを高速で検出できる周波数検出器及び周波数エラーの検出方法を提供する。

【解決手段】 予測されたランレングス信号の予測分布度に基づいて、周波数検出周期の間にサンプルされたRF信号からランレングス信号を検出するランレングス信号検出ユニットと、周波数検出周期の間に、検出されたランレングス信号をカウントする少なくとも一つのカウンタを備えたカウンタユニットと、サンプルされたRF信号のパッシングエッジをカウントして、周波数検出周期を制御するエッジカウンタと、カウンタユニットに含まれたカウンタによりカウントされた値及び所定の基準値を利用して、周波数検出周期の間の周波数エラーを生成する周波数エラー生成ユニットとを備える。

(もっと読む)

201 - 220 / 265

[ Back to top ]