Fターム[5J106DD13]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | 合成・分配回路 (405) | 加算・減算回路 (265)

Fターム[5J106DD13]に分類される特許

81 - 100 / 265

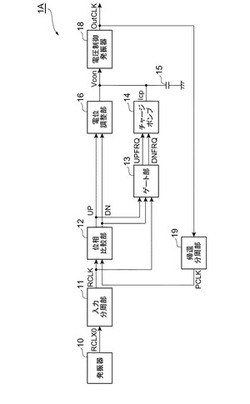

PLL周波数シンセサイザ

【課題】ループフィルタの容量素子の面積の増大を抑制しつつループフィルタの自然周波数ωnを小さくすることができるPLL周波数シンセサイザを提供する。

【解決手段】PLL周波数シンセサイザ1Aでは、位相比較部12,ゲート部13,チャージポンプ14,容量素子15,電位調整部16,電圧制御発振器18および帰還分周部19によりループが構成されている。このループにおいて、ゲート部13およびチャージポンプ14と電位調整部16とは並列的に設けられている。位相比較部12に入力される基準発振信号RCLKと帰還発振信号PCLKとの位相差が小さくなるように、チャージポンプ14から容量素子15へ充放電電流Icpが入力され、また、電位調整部16により容量素子15の第1端の電位が調整される。

(もっと読む)

クロックデータ再生回路

【課題】複数のVCO間の発振周波数のばらつきを補償し、ジッタを低減する。

【解決手段】第1の発振回路および第2の発振回路はそれぞれ2つの周波数制御端子を備え、それぞれの一方の周波数制御端子に周波数制御信号Aを入力する構成であり、第2の発振回路の他方の周波数制御端子に固定の周波数制御信号Bを与え、第1の発振回路および第2の発振回路の各発振周波数を比較し、その周波数誤差に応じた周波数制御信号Cを第1の発振回路の他方の周波数制御端子に与えるばらつき補償回路を備える。

(もっと読む)

アキュムレータおよび位相デジタル変換器を使用する2ポイント変調のデジタル位相同期ループ

2ポイント変調をサポートするデジタル位相同期ループ(DPLL)が説明される。1つの設計において、DPLLは、位相デジタル変換器、ループ内で動作するループフィルタ、ローパス変調パスのための第1の処理ユニットおよびハイパス変調パスのための第2の処理ユニットを含む。第1の処理ユニットは、入力変調信号を受信し、位相デジタル変換器の後でループフィルタより前のループの内部の第1のポイントに対して第1の変調信号を供給する。第2の処理ユニットは、入力変調信号を受信し、ループフィルタより後のループの内部の第2のポイントに対して第2の変調信号を供給する。第1の処理ユニットは、周波数を位相に変換するために入力変調信号を累算するアキュムレータを含み得る。第2の処理ユニットは、可変利得で入力変調信号をスケールするスケーリングユニットを含み得る。 (もっと読む)

電圧制御発振器のための補償回路

【課題】電圧制御発振器のための補償回路を提供する。

【解決手段】電圧制御発振器(VCO)の電圧を制御するために使用され得る回路は、第1の比較器、第2の比較器、アキュムレータ、及び出力装置を備え得る。第1の比較器は、制御電圧が高電位側しきい値電圧より高い場合に第1のパルス信号を出力する。第2の比較器は、制御電圧が低電位側しきい値電圧より低い場合に第2のパルス信号を出力する。アキュムレータは、もし第1のパルス信号が受信されるならばスイッチ制御信号の値を増加させ、もし第2のパルス信号が受信されるならばスイッチ制御信号の値を減少させる。出力装置は、スイッチ制御信号の値に応じてVCOの制御電圧を補償する補償電圧を生成する。

(もっと読む)

半導体装置

【課題】フラクショナルN−PLL回路における出力クロック信号でのスプリアスの発生を抑制する。

【解決手段】出力クロック信号を出力する電圧制御発振器と、出力クロック信号を分周して分周クロック信号を生成し、基準クロック信号と分周クロック信号とを比較し、比較結果に基づき出力信号を出力するN個の制御ユニットと、各制御ユニットからの出力信号を加算する加算器と、加算器の出力をフィルタ処理し電圧制御発振器に出力するローパスフィルタとを備え、分周クロック信号に同期して所定の順序で巡回させ供給するN個のデータからなる分周比に係る設定情報を、各制御ユニットに対して初期値を互いに異ならせて供給し分周動作及び比較動作を行わせるようにして、N個の制御ユニットにより移動平均フィルタを形成し量子化ノイズを低減し、出力クロック信号でのスプリアスの発生を抑制できるようにする。

(もっと読む)

シンセサイザと、これを用いたシンセサイザモジュール、受信装置、及び電子機器

【課題】位相雑音の劣化の少ないシンセサイザを提供すること。

【解決手段】シンセサイザ1の制御部7は、発振器5に電圧を出力するループフィルタ17の平滑回路に蓄積された電荷を予め設定された値に戻すことなく、温度を検出する温度検出部8の出力信号に基づいて分周器6の分周比を変化させる。これにより、シンセサイザ1は、温度変化に対応して制御部7が分周器6の制御を行う場合、ループフィルタ17の平滑回路に蓄積された電荷を予め設定された値に戻さないので、発振器5の発振周波数が大きく変動することを抑制し、これにより、シンセサイザ1における位相雑音を低減させることができる。

(もっと読む)

通信装置、位相同期ループ、移動体および通信方法

【課題】通信装置、位相同期ループ、移動体および通信方法を提供すること。

【解決手段】受信信号の同期保持を行うための位相同期ループ254を備え、前記位相同期ループは、n次の位相同期ループ用の回路構成nを包含する、m次の位相同期ループ用の回路構成m(m>n)、を有するループフィルタ109と、前記ループフィルタにおいて有効化される回路構成を、前記回路構成nと前記回路構成mとで切替える切替部と、を含む、通信装置。

(もっと読む)

量子周波数標準器及び時刻制御システム

【課題】簡素な回路構成で低消費電力の量子周波数標準器。

【解決手段】化学結合している原子核間のスピン−スピン相互作用によって複数に分裂したエネルギー準位を有する物質110を含む容器120と、容器120に磁場を与える磁場発生源MGと、容器120に電磁波を照射する発振器150と、を含む核磁気共鳴部100と、核磁気共鳴部100から出力される共鳴信号RSからエネルギー準位の核磁気共鳴周波数f1を検出し第1検出信号SD1として出力する第1検出部200と、共鳴信号RSから隣り合うエネルギー準位間のエネルギー差であるスピン結合定数Jを検出し第2検出信号SD2として出力する第2検出部300と、第1検出信号SD1と第2検出信号SD2に基づき核磁気共鳴部100を駆動する駆動信号DSを生成する駆動信号生成部400と、を含み、第2検出部300は、第2検出信号SD2に基づき標準周波数信号SOを出力する。

(もっと読む)

発振器および位相同期ループ

【課題】発振器の位相雑音を低減し、位相同期ループの消費電力および位相雑音を低減する。

【解決手段】発振器は、共振回路の容量値に応じて発振周波数が可変する構成であって、外部から入力する外部クロックと設定データに応じて、オーバーフロー信号を間欠的に出力するアキュムレータ11と、オーバーフロー信号の間欠入力に応じてオン・オフするスイッチ12と、スイッチ12を介して共振回路に接続される固定容量値を有する容量素子C2とを備え、設定データに応じて間欠的に出力されるオーバーフロー信号の入力によりスイッチ12がオンとなるオン時間における発振周波数と、オーバーフロー信号が入力されないときにスイッチ12がオフとなるオフ時間における発振周波数との間で、オン時間とオフ時間の時間割合に応じた平均発振周波数を可変させる。

(もっと読む)

発振器制御装置

【課題】安定したPLL動作を確立できる発振器制御装置を提供する。

【解決手段】発振器制御装置は、発振器調整信号OTWに応じた発振周波数の発振信号を出力するデジタル制御発振器100と、発振信号で同期化された基準信号に基づいてカウント値を出力するカウンタ120と、発振信号と基準信号との位相差dを算出する時間デジタル変換器130と、カウント値と位相差とを加算し、加算値を第1位相情報として出力する加算器140と、発振信号の立ち上がりタイミングと基準信号の立ち上がりタイミングとの時間差が所定時間未満である場合に、デジタル制御発振器の発振周波数を設定するための位相制御信号Acc1に基づいて第1位相情報を補正し、第2位相情報を出力する補正部160と、位相制御信号と第2位相情報との差分を平滑化するフィルタ180と、フィルタ出力にパラメータKを乗算して発振器調整信号OTWを出力する乗算器190と、を備える。

(もっと読む)

ジッタ発生装置

【課題】本発明は、ジッタ抑制分を加味することなく、ジッタを付加することが出来るジッタ発生装置を実現することを目的にする。

【解決手段】本発明は、一方の入力に基準信号を入力し、他方の入力と位相比較を行い、位相差が閾値未満のとき、位相比較結果を出力しない位相比較器と、この位相比較器の出力を入力とするローパスフィルタと、このローパスフィルタの出力を入力とする電圧制御発振器と、この電圧制御発振器の出力を入力とし、位相比較器の他方の入力に出力する帰還回路と、ローパスフィルタの前後の少なくとも一方に設けられ、ジッタ信号を入力信号に加算し、出力する加算器とを備えたことを特徴とするものである。

(もっと読む)

位相同期回路及びこれを用いた受信機

【課題】フラクショナルスプリアスの発生しない位相同期回路を提供する。

【解決手段】第1の分数及び第2の分数の和で表される比率を基準信号の周波数に乗じて得られる対象信号に周波数及び位相が一致した出力信号を得る位相同期回路において、第1の分数の分母と第2の分数の分母と2との最小公倍数を更に2で除した数と同じ段数の増幅器を環状接続して構成され、最小公倍数と同じ信号数の多相信号が取り出し可能であって多相信号の周波数がデジタル制御信号及びアナログ制御信号によって制御され、多相信号の1つが出力信号として出力される制御発振器120と、出力信号と基準信号との間の周波数差及び位相差をデジタル信号に変換する変換部116と、デジタル信号に基づいて、基準信号の周期毎に、次の周期において基準信号と位相が一致する信号を多相信号から順次選択する信号選択部140とを具備する。

(もっと読む)

クロック生成回路

【課題】高速動作するクロック・データリカバリのための正確なクロック信号を生成するクロック生成回路を提供する。

【解決手段】クロック生成回路は、第1入力電圧に応じて第1周波数信号を出力する第1電圧制御発振回路と、第2入力電圧に応じて第2周波数信号を出力する第2電圧制御発振回路と、制御信号を受け取り、第1周波数信号と第2周波数信号との位相差が制御信号に応じた値になるように第1入力電圧と第2入力電圧とを制御する位相調整回路と、第1周波数信号に同期して受信信号を検出して出力する第1判定回路と、第2周波数信号に同期して受信信号を検出して出力する第2判定回路と、第1判定回路の出力と第2判定回路の出力とに基づいて受信信号の位相を検出し、その位相検出の結果に応じて第1入力電圧と第2入力電圧とを制御する位相検出器とを含む。

(もっと読む)

位相誤差検出装置、位相誤差検出方法、集積回路及び光ディスク装置

【課題】周波数誤差が生じているときでも±180度を越える位相誤差の検出を可能とし、PLLの安定性を向上させることができる位相誤差検出装置を提供する。

【解決手段】アナログ入力信号をサンプリングクロックに基づいてAD変換してデジタル再生信号を生成するAD変換部1の出力より位相誤差を検出する位相誤差検出装置は、AD変換部1の出力より前記位相誤差を生成する位相誤差生成部2と、位相誤差を補正する位相誤差補正部3とを含み、位相誤差補正部3は、過去の位相誤差により位相誤差検出範囲を決定し、位相誤差生成部2が生成した位相誤差が位相誤差検出範囲外であった場合に当該位相誤差を補正する。

(もっと読む)

デジタルフェーズロックドループ回路

【課題】従来のADPLL回路では、出力クロックにデューティ劣化がある場合、最終的に導き出される位相差に大きな誤差が生じてしまう。

【解決手段】第1クロックをカウントする第1カウンタと、第2クロックを分周した第3クロックをカウントする第2カウンタと、第3クロックの遅延クロックと第1クロックを比較した第1比較結果と、第1クロックの遅延クロックと第3クロックを比較した第2比較結果とに応じ第1、第3クロックの相対的位相差を検出する第1位相検出器と、第2クロックの周期を測定する第2位相検出器と、第2位相検出器の検出結果により第1位相検出器の検出結果を正規化した値と、第1、第2カウンタの値とに応じて第1、第3クロックとの位相差を演算する位相誤差演算部と、位相誤差演算部の演算結果に応じ第2クロックを出力するDCOとを有するデジタルPLL回路。

(もっと読む)

周波数シンセサイザ

【課題】 AD変換器への入力レベルが変化したときに、PLL制御が正常に動作しない状況を防止して周波数ずれの発生を防止できる周波数シンセサイザを提供する。

【解決手段】 キャリアリムーブ16と、逆回転ベクトル乗算部17と、位相の時間差検出部18と、加算器19と、位相差の累積加算部20と、ループフィルタ21と、パラメータ出力部25と、振幅情報検出部26と、フィルタ27と、乗算器28とをFPGAで構成し、振幅情報検出部26で検出された振幅情報の値をアンロック検出手段が監視し、当該値が適正範囲内であれば、PLL制御におけるロック(同期)処理を行い、当該値が適正範囲外であれば、PLL制御におけるアンロックを検出し、そのアンロックの検出でアラーム検出するようにした周波数シンセサイザである。

(もっと読む)

PLL回路、及び無線機

【課題】 位相誤差の小さい、発振信号の精度が高いPLL回路及び無線機を提供する。

【解決手段】 第一差動信号を生成する第一発振部と、前記第一差動信号を90度の位相差をもつ第二差動信号を生成する第二発振部と、を有する電圧制御発振器と、前記第一及び第二差動信号に基づく第三差動信号の位相と、基準信号の位相とを比較する位相比較器と、前記位相比較器の比較結果に基づいて、前記電圧制御発振器を制御する制御電圧を生成するループフィルタと、を具備することを特徴とするPLL回路。

(もっと読む)

位相同期回路、および通信装置

【課題】設定される動作モードに基づいて処理信号の処理クロック周波数を動作モードに基づいて切り替え、消費電力の低減を図ることが可能な位相同期回路、および通信装置を提供する。

【解決手段】デジタル値で表される発振制御信号に基づく発振周波数の発振信号を出力する発振回路と、搬送波周波数が基準周波数で除算された分周比と動作モードを規定する制御信号とが入力され、分周比を制御信号に基づいて設定された整数値で除算する第1ビットシフト部と、発振信号に基づく信号と制御信号とが入力され制御信号に基づいて設定された整数値により発振信号に基づく信号を分周する第1分周部と、基準周波数信号の各周期において第1累積加算値と第2累積加算値および累積位相の小数部とを比較し位相比較信号を出力する位相比較部と、位相比較信号を制御信号に基づく任意の収束値に収束させ発振制御信号を出力するデータ変換部とを備える位相同期回路が提供される。

(もっと読む)

2ポイント変調と適応遅延マッチングとを用いるデジタル位相ロックドループ

適応遅延マッチングとともに2ポイント変調をサポートするデジタル位相ロックドループ(DPLL)が記述される。DPLLは、それぞれ、発振器の周波数および/または位相の広帯域および狭帯域の変調をサポートするハイパスおよびローパス変調パスを含む。DPLLは、他の変調パスの遅延と合わせるためにある変調パスの遅延を適応して調整することができる。ある設計において、DPLLは、2つの変調パスのうちの一つに、可変遅延を提供する適応遅延ユニットを含む。適応遅延ユニット内で、遅延計算ユニットは、2つの変調パスに適用される変調する信号と、DPLLにおける位相エラー信号とに基づいて、可変遅延を決定する。補正器は可変遅延の小数部分を提供し、プログラマブル遅延ユニットは可変遅延の整数部分を提供する。 (もっと読む)

クロック発生装置およびクロック発生装置におけるジッタ低減方法

【課題】よりジッタの少ないクロック信号を発生させること。

【解決手段】周期信号を発生するDDS回路と、入力信号と基準信号とを比較して2値化信号を出力するコンパレータと、を有し、前記DDS回路において発生される前記周期信号に対し、前記基準信号との交差点における変化率を増加させる補正を行う変化率補正手段を備えることを特徴としている。

(もっと読む)

81 - 100 / 265

[ Back to top ]