Fターム[5J106DD13]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | 合成・分配回路 (405) | 加算・減算回路 (265)

Fターム[5J106DD13]に分類される特許

121 - 140 / 265

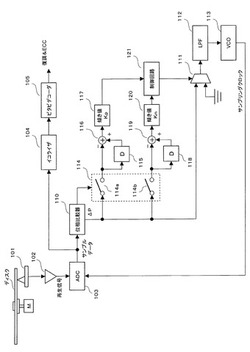

PLL回路およびディスク再生装置

【課題】簡易な演算処理にて、適時かつ迅速に、周波数誤差を検出でき、これにより、サンプリングクロックの位相誤差を円滑に補正できるPLL回路を提供する。

【解決手段】再生信号の立ち上がり時に検出された位相誤差量が、遅延回路115と減算回路116に供給される。減算回路116は、供給された位相誤差量と一回前に供給された位相誤差量(遅延回路115からの出力)とを減算する。この減算結果をもとに、時間軸上における位相誤差量の傾き値Kp(周波数誤差)が傾き値算出回路117にて算出される。同様に、再生信号の立ち下がり時に検出された位相誤差量から傾き値Knが傾き値算出回路120にて算出される。制御回路121は、傾き値Kp,Knの何れかが閾値を超えると制御信号を出力する。セレクタ111は、制御信号が入力されると位相誤差量に替えてグランド信号をLPF112に供給する。

(もっと読む)

周波数ダイバース離散時間位相ロックデバイス及び装置

【課題】周波数ダイバース離散時間位相ロックデバイスを提供する。

【解決手段】デジタル−アナログ変換器(DAC)、及び、該DACからの入力に基づいてクロック信号を与えるように動作する発振器を含む、アナログセクションと、デジタルシグナルプロセッサ(DSP)とを備えており、このデジタルシグナルプロセッサは、ループコントローラ状態機械と、位相検出器309と、発振器からのクロック信号を受信すると共に、前記位相検出器にカウント値を与えるように動作するカウンタ307と、基準信号310を受信すると共に、前記位相検出器に基準パルス312出力を与えるように動作する分周器と、相検出器309からの出力に基づいて、制御目標値320を与えるように動作するループフィルタ302とを備えており、前記位相誤差値に基づいて、前記発振器の出力が、前記位相誤差を定常状態値まで低減するように変更される。

(もっと読む)

電圧制御発振器

【課題】ループフィルタの変化電圧範囲と電圧制御発振器との許容入力範囲を整合させるためにシフト電圧生成回路を設けるが、基準電圧電源やグランドからの電源変動が電圧制御発振器の制御入力電圧に重畳し、正確な周波数の信号を供給できない問題があった。

【解決手段】本発明の電圧制御発振器のシフト電圧生成回路は、同じ基準電圧電源から加算電圧信号と中間基準電圧信号とを作成することにより、電圧変動波形の位相を同じくし、オペアンプの差動入力にそれぞれを入力し電圧変動を除去する。また、基準電圧電源と加算電圧信号あるいは中間基準電圧信号出力との間にローパスフィルタを設け、電圧変動を抑制する。これにより、電圧変動のない制御入力電圧が電圧制御発振器に入力でき、正確な周波数の出力信号を供給可能になる。

(もっと読む)

クロック信号分周回路および方法

【課題】大きな回路規模を必要とすることなく、有理数分周した出力クロック信号のサイクル時間変動を抑制するとともに、分周時に出力クロック信号の位相を調整する。

【解決手段】クロック選択制御回路100により、入力クロック信号のサイクルごとに、分周比に応じた一定サイクル時間を有する基準分周クロック信号と入力クロック信号との位相関係を示す位相計算値111を計算するとともに、位相調整信号に応じてその値を増減し、この位相計算値111に基づいて、出力動作のうち、基準分周クロック信号の位相と近いクロック信号を生成するための出力動作を指示する制御信号102,103を生成する。クロック選択回路101により、制御信号102,103に基づいて、入力クロック信号のクロックパルスをそのまま非反転で出力するか、反転して出力するか、マスクして出力しないか、のいずれかの出力動作を選択して実行することにより、出力クロック信号を生成する。

(もっと読む)

周波数生成装置、周波数生成方法、信号処理装置及び信号処理方法

【課題】

入力信号に含まれる所定信号に精度良く同期しつつ、入力信号を精度良く処理する。

【解決手段】

直交化信号生成部110Aが、入力信号SIAに含まれる角周波数ωCのパイロット信号の位相を反映し、互いの直交化が図られた信号PSA1,PSA2を生成する。これらの信号PSA1,PSA2に基づいて、位相算出部120Aが、パイロット信号PSを反映した各時点における位相を算出する。この算出結果に基づいて、生成部130がパイロット信号PSを反映した角周波数を生成する。そして、生成部130により生成された角周波数に基づいて、位相補正部140が、直交化信号生成部110A内のフィルタによる位相シフトの周波数特性を補正する。

(もっと読む)

周波数補正回路及びそれを用いた無線通信装置

【課題】 発振器の出力周波数が増減した場合に自動補正を可能として常に出力周波数の精度を一定の範囲内に維持する周波数補正回路を得る。

【解決手段】 発振器2の発振周波数よりも高精度の基準周波数を、発振周波数を分周した分周周期毎に計数するカウンタ5と、発振周波数が正常な時のカウンタの計数値に相当する正常値に対して所定値Mを加算した値とカウンタの計数値とを比較して一致したときに発振周波数の減少を示す信号を生成する比較回路7と、正常値に対してMを減算した値とカウンタの計数値とを比較する比較回路8と、この比較回路8の一致結果に応答してこの一致結果を所定時間マスクするためのマスク信号を生成する単安定マルチバイブレータ11と、比較回路7の減少を示す信号に応じて発振周波数を減少方向に制御し、マスク信号の非生成時に発振周波数を増加方向に制御する制御回路12及びCPU1とを含む。

(もっと読む)

周波数シンセサイザ

【課題】広帯域を細かく設定でき、周波数の引き込み範囲が広い周波数シンセサイザを提供する。

【解決手段】電圧制御発振部の出力周波数の正弦波信号を直交検波し、検波に用いた周波数信号の周波数との差分の周波数(速度)で回転するベクトルを利用したPLLにて、周波数引き込み手段は、PLLから電圧制御発振部への制御電圧が予め設定した設定範囲よりも大きい場合には、出力周波数を上昇させるための第1の定数を引き込み用電圧として積分し、また当該制御電圧が前記設定範囲よりも小さい場合には、出力周波数を低下させるための第2の定数を引き込み用電圧として積分する。そして加算手段は、PLLからの制御電圧と周波数引き込み手段からの引き込み用電圧とを加算し、電圧制御発振部へ出力する。

(もっと読む)

高分解能の時間/デジタル変換器

【解決手段】時間/デジタル変換器(TDC)は、インバータの伝播遅延よりも優れた分解能を有し得る。一例では、非整数遅延素子回路は、TDC入力信号を受信し、そこから、第1信号の時間シフトした複製である第2信号を生成する。第1信号は、第1遅延線タイムスタンプ回路(DLTC)に供給され、第2信号は第2DLTCに供給される。第1DLTCは、TDCへの参照入力信号のエッジと第1信号のエッジとの間の時間を示す第1タイムスタンプを生成する。第2DLTCは、参照入力信号のエッジと第2信号のエッジとの間の時間を示す第2タイムスタンプを生成する。第1及び第2タイムスタンプは合成されて、共に高い分解能の全体のTDCタイムスタンプを構成する。これは、第1または第2タイムスタンプよりも優れた分解能を有する。 (もっと読む)

シンセサイザと、これを用いた受信装置、および電子機器

【課題】精度の高い発振周波数を生み出す事ができるシンセサイザを提供する事を目的とする。

【解決手段】シンセサイザ1は、基準発振器2からの基準発振信号が入力される比較器4と、比較器4の出力信号に基づいて発振信号を出力する電圧制御発振器5と、この電圧制御発振器5の出力信号を制御部7からの制御信号に基づいて分周する第2分周器6とを備えており、比較器4は、第2分周器6からの出力信号と基準発振器2からの出力信号とを比較してこの比較結果を示す信号を電圧制御発振器5に出力し、シンセサイザ1を用いる電子機器の使用状態に基づいて、第2分周器6の分周比の値が決められている。これにより、温度検出部8とMEMS振動子11との間の温度差に起因したシンセサイザの発振周波数誤差を無くす事ができる。

(もっと読む)

周波数補償回路

【課題】感温部品を用いることなく、温度変動やデバイス自体に個体差がある場合でも、高精度で安定した掃引周波数又は変調信号を得ることが可能となるようにする。

【解決手段】制御電圧発生器から出力された掃引波(又は変調波)の制御電圧を入力し、所定幅の周波数を発生するためのVCO14、このVCO14の出力を入力し、任意に設定した校正周波数に位相ロックした電子同調電圧をVCO14へ帰還させるPLL−IC回路20及びループフィルタ21、上記VCO14の前段で、制御電圧発生器側とPLL回路側とを切り替える切替えスイッチ18、この切替えスイッチ18でPLL回路側に切り替えたとき、上記ループフィルタ21から電子同調電圧Vfを取り出し、制御電圧発生器側に切り替えたとき、取り出した電子同調電圧を上記制御電圧発生器からの出力制御電圧Vaに加算する回路(CPU23,DAC26,加算器28)を設ける。

(もっと読む)

半導体集積回路

【課題】クロック信号生成部をディジタル制御するレジスタへの制御情報の格納ステップを削減すること。

【解決手段】半導体集積回路は、クロック信号CLKmを生成するディジタル制御信号生成部10、ディジタル制御部20を具備するクロック生成部を含む。クロック生成部は、位相周波数比較器31、制御レジスタ22を更に具備する。比較器31には、基準信号CLKinとフィードバック信号Moutが供給される。制御レジスタ22に比較器31の出力信号FDoutが供給され、制御レジスタ22は複数ビットのディジタル制御情報を格納する。クロック生成部は、複数のロック動作のための複数の初期設定データを予め格納する制御データ記憶回路25を更に具備する。動作選択情報Minに応答して制御データ記憶回路25から初期設定データSet1〜Set5が、制御レジスタ22の上位ビットに格納される。

(もっと読む)

信号処理回路、信号処理方法、再生装置

【課題】パイプライン処理によるPLLの処理速度の高速化と収束性能の向上との両立を図る。

【解決手段】例えば二次のPLLにおいて、ループフィルタの入力に対して、該ループフィルタの出力の移動平均を負帰還すると共に、該ループフィルタの積分項に対して所定ゲインを与えたものを正帰還する。具体的には、フィードバック制御ループとしての閉ループ全体の遅延量をDとしたとき、上記ループフィルタの出力の「D−1」回の移動平均を上記ループフィルタの入力に負帰還し、上記ループフィルタの積分項に対しDをゲインとして乗じたものを上記ループフィルタの入力に正帰還する。これにより、フィードバック制御ループ内に生じる遅延成分を補償することができ、パイプラインディレイの補償が可能となる。つまりこれにより、パイプライン処理によるPLLの処理速度の高速化と収束性能の向上との両立が図られる。

(もっと読む)

同期クロック生成回路及び同期クロック生成回路を備えたアナログ/ディジタル角度変換器と角度検出装置

【課題】安価に構成することができる同期クロック生成回路を提供する。

【解決手段】角度検出器10の出力する2相の角度信号S1とS2を、第1二乗回路11と第2二乗回路12でそれぞれ二乗し、それぞれの二乗信号を加算回路14で加算し、加算回路14の出力信号の直流成分をフィルタ16で除去する。フィルタ16の出力信号と基準電位とを比較するコンパレータ18で矩形波に変換し、その矩形波の位相を移相器20で所定量遅らせる。移相器20の出力信号を、同期化分周回路22で角度検出器10に供給する励磁信号に同期して1/2分周して同期クロックSQ3を得る。

(もっと読む)

ゲート時間/デジタル変換器を有するデジタル位相ロックドループ

デジタルPLL(DPLL)、時間/デジタル変換器(TDC)および制御ユニットを含む。TDCは、位相情報を量子化するために、短い時間の間、周期的に有効され、電力消費を削減するために、残り時間の間、無効にされる。TDCは、第1のクロック信号と第1の基準信号を受信し、第1のクロック信号と第1の基準信号との位相差を示す出力をTDCに提供する。制御ユニットは、主基準信号に基づいてイネーブル信号を生成し、イネーブル信号でTDCを有効および無効にする。ある設計において、制御ユニットは、第1の基準信号および第2の基準信号を獲得するために、主基準信号を遅らせ、主基準信号および第2の基準信号に基づいてイネーブル信号を生成し、TDCに対する第1のクロック信号を獲得するために、イネーブル信号で主クロック信号をゲートする。 (もっと読む)

PLL回路

【課題】 VCOを構成する電流制御発振回路を制御する電流を生成する電圧−電流変換の動作を高速化して、従来に比較して周波数制御の応答特性を向上させるPLL回路を提供する。

【解決手段】 本発明のPLL回路は、電圧−電流変換回路と電流加算器と電流制御発振回路とから構成され、制御電圧及び制御電流に対応した周波数のパルスを出力する電圧制御発振回路と、パルスと、電圧制御発振回路が生成すべき周波数の基準パルスとの位相差により、第1の制御信号及び第2の制御信号を出力する位相検出器と、第1の制御信号により、第1の充電電流または第1の放電電流を出力する第1のチャージポンプ回路と、第1の充電電流または第1の放電電流により制御電圧を生成し、電圧制御発振回路に出力するループフィルタと、第2の制御信号により、第2の充電電流または第2の放電電流である制御電流を生成し、制御電圧発振回路に出力する第2のチャージポンプ回路とを有する。

(もっと読む)

位相差平滑化装置

【課題】多相クロック生成及び伝送の過程において発生した多相クロックの位相誤差を低減する。

【解決手段】入力多相クロックのうち所望の位相関係にある複数のクロックを入力して各クロックの位相に所望の重み付けをする重み付け手段と、重み付けされたクロックを加算する加算手段と、を有する位相フィルタ回路を前記多相クロックの位相数と同数備え、位相フィルタ回路から出力されたクロックを出力多相クロックとして出力する。

(もっと読む)

DLL回路およびその制御方法

【課題】より向上したデューティ比特性を有するクロックを生成する。

【解決手段】本発明は、デュアルループタイプ(Dual Loop Type)のDLL回路であって、第1位相検知信号に応答し、第1遅延制御信号を生成して第1遅延ラインの遅延量を制御し、第1遅延量情報信号を出力する第1遅延制御手段と、第2位相検知信号に応答し、第2遅延制御信号を生成して第2遅延ラインの遅延量を制御し、第2遅延量情報信号を出力し、前記第1遅延制御信号と半周期情報信号に応答して前記第2遅延ラインの遅延量を再び制御する第2遅延制御手段と、前記第1遅延量情報信号と前記第2遅延量情報信号の入力を受け、基準クロックの半周期情報を抽出して前記半周期情報信号を生成する半周期検知手段と、前記第1遅延ラインの出力クロックと前記第2遅延ラインの出力クロックを組み合わせてデューティ比補正クロックを出力するデューティーサイクル補正手段とを含む。

(もっと読む)

PLLキャリブレーション

変調信号を位相ロックループに加える方法であって、前記変調信号をフィルタリングして低周波数成分と高周波数成分を準備し、位相ロックループのフィードバック経路及びフィードフォワード経路にそれぞれ加えることを含む。前記高周波数成分は、前記フィードフォワード経路に加えられる前に、ゲイン係数によりスケールされる。前記低周波数成分も、ゲイン係数によりスケールされた後、前記フィードフォワード経路に加えられる。前記変調信号とループエラー信号との共通の低周波数範囲におけるエネルギーが見積もられ、その後、前記ゲイン係数は前記測定されたエネルギーに基づいて変更される。  (もっと読む)

(もっと読む)

マルチチャネル・データ検出システム用に構成されたエラー組み合わせ論理およびエラー信号を生成するための方法

【課題】 各チャネル用のフェーズ・ロック・ループを有するマルチチャネル・データ検出システムの位相エラー組み合わせ論理を提供することにある。

【解決手段】 この位相エラー組み合わせ論理は、各チャネルに関する位相エラー情報を受信することと、受信位相エラー情報を結合し、結合された位相エラーを生成するように構成された組み合わせ論理と、結合された位相エラーを少なくとも1つのチャネル・フェーズ・ロック・ループに適用するように構成された位相エラー出力とを含む。さらに、エラー信号組み合わせ論理は、各チャネルに関するフェーズ・ロック・ループに関連する信号のエラー情報を受信することと、受信エラー信号情報を結合し、結合されたエラー信号を生成し、たとえば、信頼性情報により、各チャネルからの受信エラー信号情報に重みを付けるように構成された組み合わせ論理とを含む。エラー補償出力は、結合され重みが付けられたエラー信号を少なくとも1つのチャネル・フェーズ・ロック・ループに適用するように構成される。

(もっと読む)

マルチチャネル・データ検出システム用に構成された周波数エラー組み合わせ論理および周波数エラーを生成するための方法

【課題】 各チャネル用のフェーズ・ロック・ループを有するマルチチャネル・データ検出システムの周波数エラー組み合わせ論理を提供することにある。

【解決手段】 この周波数エラー組み合わせ論理は、各チャネルに関する周波数エラー情報を受信することと、受信周波数エラー情報を結合し、結合された位相エラーを生成し、各チャネルからの受信周波数エラー情報に重みを付けるように構成された組み合わせ論理と、結合された周波数エラーを少なくとも1つのチャネル・フェーズ・ロック・ループに適用するように構成された周波数エラー出力とを含む。

(もっと読む)

121 - 140 / 265

[ Back to top ]