Fターム[5J106DD13]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | 合成・分配回路 (405) | 加算・減算回路 (265)

Fターム[5J106DD13]に分類される特許

161 - 180 / 265

信号処理装置

【課題】変調信号の復調を実行する際の消費電力を低減し、かつ実装コストを抑制することが可能な信号処理装置を提供する。

【解決手段】本発明に係る信号処理装置は、互いにほぼ直交する第1及び第2のリファレンス信号を生成する発振器と、搬送波周波数からベースバンド周波数に変換された変調信号の同相成分を示す第1信号と当該変調信号の直交成分を示す第2信号を入力する入力部と、第1信号と第1リファレンス信号の位相比較を行って、比較結果に応じた位相差を示す第1位相差信号を出力する第1位相比較器と、第2信号と第2リファレンス信号の位相比較を行って、比較結果に応じた位相差を示す第2位相差信号を出力する第2位相比較器と、第2位相差信号から第1位相差信号を減算し、合成位相差信号を出力する合成部を備え、合成部から出力された信号を復調信号として出力すると共に、発信器への入力として用いる。

(もっと読む)

デジタルシンセサイザ

【課題】位相比較器および信号発振器をデジタル化することによって短時間に同期を確立し、同期状態を高精度でしかも高安定に保持することができるデジタルシンセサイザあるいはデジタル同期発振器を提供する。

【解決手段】少なくとも、デジタル位相比較器21と、デジタル制御発振器22と、分周器23から構成する。

【効果】通信システムにおいて同じ周波数であることが必須の2つの入力信号の間で短時間に同期を確立し、入力信号が停止した場合あるいは取去られた場合にも、同期状態を高精度でしかも高安定に保持する。

(もっと読む)

ガスセル型原子発振器

【課題】 原子発振器の出力する安定な周波数の信号を使う場所が離れている場合に、その信号を長い同軸ケーブルで搬送していた。外部環境が同軸ケーブルに影響して発生する信号の周波数の揺らぎを削減する。

【解決手段】金属原子に対する励起光を出力する光源部1を設置する。その場所から離れて設置された原子共鳴部30には、該光源部1からの出射光を伝播させる光ファイバ33,34から出射される励起光と共鳴マイクロ波とを入力する。原子共鳴部30は、光マイクロ波二重共鳴を起し、その際に生じる共鳴周波数を出力する。

(もっと読む)

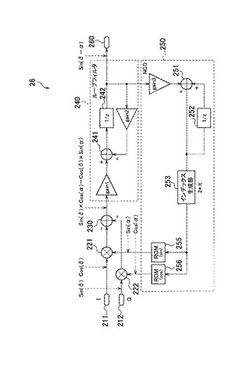

PLL回路および再生装置

【課題】データ信号からクロックを復調する際に、周波数ロックがはずれることを防ぎ、再生装置の再生品質を高める。

【解決手段】PLL回路200は位相追従ループと周波数追従ループを備える。周波数追従ループは、周波数比較器202とローパスフィルタLPF225とを備える。周波数比較器202は、復調クロックCLKとデータ信号S1との周波数差を検出し、検出結果に応じた周波数誤差信号を出力する。LPF225は、周波数誤差信号に応じて充放電するコンデンサ226の充放電により周波数誤差信号を平滑して周波数制御電圧信号FVCを得る。第1の制御部240と第2の制御部250は、周波数ロック状態において、周波数比較器202からLPF225への出力が遮断されるオフ期間と遮断されないオン期間が交互に繰り返されるように制御し、オフ期間においてリーク電流に起因するFVCの変動を補正する。

(もっと読む)

同期損失防止方法及び同期損失防止装置

【課題】CDR回路側の原因による接続ノード間の同期化の非成立を抑制し、接続失敗を抑制することができる同期損失防止方法及び同期損失防止装置を提供する。

【解決手段】受信データから同期化クロックを生成するCDR(Clock Data Recovery )回路と、受信データの受信開始から同期化検出時間Nを経過しても同期化クロックに基づく接続ノード間の同期化が非成立のときに、接続失敗処理を行う接続失敗処理段階(S15)と、受信データの受信開始から同期化リトライ判定時間(N/2)を経過しても同期化クロックに基づく接続ノード間の同期化が非成立のときに、CDR回路の動作を補正処理する補正処理段階(S13)とを備える。

(もっと読む)

クロックデータリカバリー回路及び通信装置

【課題】LSI化に適し且つ従来のPLLを用いたのと同等の特性を設定できるシリアルデータインターフェースのCDR回路を提供する。

【解決手段】本発明のCDR回路は、所定周波数のクロックの周期T1をN分割したT2時間ずつずらしたN相のクロックを出力する手段、シリアル転送されたデータをT2時間毎にサンプリングする手段、サンプリングしたデータを周期T1毎に第1のNビットパラレルデータに変換する手段、サンプリングしたデータのデータ変化点を示す第2のNビットパラレルデータに変換する手段、及び、第2のNビットパラレルデータを位相情報入力としてシリアルデータのデータ変化点の略中間位置を示す第3のNビットパラレルデータを出力する手段を有し、第3のNビットパラレルデータが示したビット位置と同じ、第1のNビットパラレルデータのビット位置データを復元データとすることを特徴とする。

(もっと読む)

分数分周PLL装置、およびその制御方法

【課題】設定すべきパラメータ数が減ぜられて使い勝手の向上が図られると共に、回路の簡略化を図ることが可能な分数分周PLL装置、およびその制御方法を提供すること

【解決手段】第1分周信号fprの初期のAサイクルの期間は、第2分周信号fAがハイレベル、第3分周信号fBがローレベルに維持される。3モジュラスプリスケーラ13は(M+1)分周値となる。引き続くBサイクルでは、第2分周信号fAがローレベル、第3分周信号fBがハイレベルである。3モジュラスプリスケーラ13は、ΣΔ変調器8から出力される擬似乱数の符号に合わせて、負値の場合に(M−1)分周値、正値の場合に(M+1)分周値となる。その後は、M分周となる。比較分周器4では、擬似乱数値Bxを含む(MN+A+Bx)の分周値が得られる。負値を含む擬似乱数をそのまま使用してΣΔ変調による分数分周を実現できる。

(もっと読む)

記録装置及び記録装置の制御方法

【課題】ディスクの回転に安定して同期した記録クロックを生成できるようにする。

【解決手段】ディスク状記録媒体に形成されているウォブルを読み取ってウォブル信号を検出し、前記ウォブル信号に基いて記録用のクロック信号を生成する記録装置であって、前記ディスク状記録媒体のウォブル周期に関連した周波数を有するクロックを生成する第1のクロック生成手段と、前記ディスク状記録媒体にデータを記録するためのチャネル周期に関連した周波数を有するクロックを生成する第2のクロック生成手段とを備え、前記第1のクロック生成手段に組み込まれているDVCO部と同一のDVCO部を組み込んで前記第2のクロック生成手段を構成する。

(もっと読む)

記録再生装置及び記録再生方法

【課題】回路規模や消費電力を増大させることなく、記録クロック及び再生クロックを安定して生成できるようにする。

【解決手段】ディスク状記録媒体に形成されたウォブル信号を検出するウォブル信号検出手段と、前記ウォブル信号検出手段によって検出されたウォブル信号に基いて、ウォブル周期に関連した周波数を有する第1のクロックを生成する第1のクロック生成手段と、前記第1のクロック生成手段が前記第1のクロックを生成する際の制御信号に予め設定された処理が施された周波数成分を制御信号とし、チャネル周期に関連した周波数を有するチャネルクロックを生成する第2のクロック生成手段とを有し、前記第1のクロック生成手段に組み込む電圧制御発振器と、前記第2のクロック生成手段に組み込む電圧制御発振器とを同一の構成にする。

(もっと読む)

位相差検出回路、PLL回路、位相差検出方法及び位相差検出プログラム

【課題】 ゼロクロスポイント検出用のハードを用いることなく、位相差の検出機能を実現する。

【解決手段】 位相差検出回路は、検出信号と内部基準信号の位相差を検出するための回路であって、d−q軸変換ユニット5と、1周期全加算ユニット6と、位相差算出ユニット7とを備えている。d−q軸変換ユニット5は、内部基準信号を用いて検出信号をd−q軸変換することで、瞬時値有効分dと瞬時値無効分qとを算出する。1周期全加算ユニット6は、瞬時値有効分dを1周期全加算することで有効分Dを算出して、さらに瞬時値無効分qを1周期全加算することで無効分Qを算出する。位相差算出ユニット7は、有効分Dと無効分Qを用いて位相差を算出する。

(もっと読む)

位相同期回路、同期検波回路および放送受信装置

【課題】簡易な構成で入力信号と同一周波数、同一位相の再生信号を出力すること。

【解決手段】位相同期回路1は、VCO13、混合器11、LPF12からなる第1のフィードバックループで周波数を合わせ、第1のフィードバックループで得られた制御信号をVCO23、混合器21、LPF22、加算器24からなる第2のフィードバックループに供給することで、第2フィードバックループから周波数と位相がともに入力信号と同一な再生信号を出力する。

(もっと読む)

信号処理回路

【課題】パルス状の入力信号のサンプリングを正確に行うことを可能とする。

【解決手段】入力信号のパルスの変動点を検出し、検出された入力信号のパルスの変動点から所定の位相幅ずれた位相点を入力信号のタイミングとして設定することにより、上記課題を解決することができる。

(もっと読む)

データ再生装置

【課題】再生信号の分解能が著しく低下した場合にも、安定して精度よくクロックを生成し、高速かつ安定したデータPLLを用いたデータ再生装置を提供する。

【解決手段】データ再生装置において、ピックアップ102の出力信号を所定のクロックでアナログ/デジタル変換するA/D変換器104と、A/D変換器104の出力信号を所望の特性に等化する波形等化回路105と、波形等化回路105の出力信号を最尤復号する最尤復号回路106と、クロックの位相誤差を検出する位相誤差検出回路107と、等化誤差を検出する等化誤差検出回路110と、位相誤差検出回路107の出力信号および等化誤差検出回路110の出力信号を加算する加算器111と、加算器111の出力信号により制御されてクロックを生成する電圧制御発振器114とを備えた。

(もっと読む)

PLL回路、位相制御方法、および、ICチップ

【課題】クロック周波数を上げることなく、受信精度を向上させる。

【解決手段】分周器131は、クロック信号f_clkを8分周することにより、PSK変調されたデジタル信号DATAとほぼ同じ周波数の互いにπ/2だけ位相が異なる信号sin(wt)、信号cos(wt)を生成する。ACT136は、信号sin(wt)および信号cos(wt)を仮想的に制御角Φだけ移相させた信号と信号DATAとの位相を比較した結果を示す信号ΣV11および信号ΣV12に基づいて、信号DATAと仮想の信号sin(wt+Φ)の位相を同期させるように、cosΦに対応するパラメータcos_paraおよびsinΦに対応するパラメータsin_paraの値を制御する。また、ACT136は、信号ΣV11およびΣV12に基づいて、CPUが信号DATAからデータを読み出すタイミングを制御する。本発明は、非接触ICチップに適用できる。

(もっと読む)

ジッタ発生装置

【課題】ジッタをデジタル的に発生させることにより、ジッタに関する調整が可能でありジッタ非注入時の信号劣化が生じることを防止したジッタ発生装置を提供する。

【解決手段】本実施の形態におけるジッタ発生装置では、第2カウンタ5が出力する−1〜1の範囲内のランダムな整数値のカウンタ値を第1カウンタ2が出力するカウンタ値に加算して、波形メモリ3にアドレスとして入力し振幅データから波形を得ることにより、ジッタをデジタル的に発生させ、波形20に対して波形21,22の波形の間をランダムにゆらいだ、ジッタが注入された波形を得ることが可能となる。

(もっと読む)

信号発生装置

【課題】本発明では、汎用DDSを使用した周波数可変の信号発生装置において、ジッター発生を抑制し、高精度の周波数可変の矩形パルス信号を発生する。

【解決手段】周波数可変の信号発生装置は、設定値に応じて変更される周波数のアナログ信号を出力するDDS1と、該アナログ信号から該周波数の第1矩形パルス信号を生成するコンパレータ3と、第1矩形パルス信号を設定される分周比で分周した第2矩形パルス信号を出力するプログラマブル分周器41と、制御部4とを備える。該周波数を高周波数領域側に変更の場合、該分周器に対し第1矩形パルス信号を出力信号Soとする。該周波数を低周波数領域側に変更の場合、DDSに対して設定値を分周比倍の値に変更制御して該分周比倍の周波数を有する第1矩形パルス信号を発生させ、分周器において当該分周比で分周した当該周波数の第2矩形パルス信号を出力信号Soとする。

(もっと読む)

クロックリカバリ回路

【課題】

過剰な位相雑音が検出されたとしても、同期外れを起しにくいクロックリカバリ回路を提供する。

【解決手段】

位相比較回路と、フィルタと、電圧制御型発振回路とを有するPLL回路を有するクロックリカバリ回路において、入力されるデータ信号に含まれるパターンを用いて、データ信号と前記電圧制御型発振回路から出力されるクロック信号との±πを超える位相差を検出し、その位相差に応じた信号を発生させる信号発生回路と、その信号を前記位相比較回路からの出力信号に加算する回路とを備える。

(もっと読む)

クロックデータ復元装置

【課題】トランスミッタ・クロック・ジッタや符号間干渉が大きい場合であっても安定してクロック信号およびデータを復元することができるクロックデータ復元装置を提供する。

【解決手段】クロックデータ復元装置1は、サンプラ部10、検出部20、オフセット決定部30、クロック出力部40およびDA変換部50を備える。クロック信号CK,CKXの位相は、入力デジタル信号の位相と一致するよう調整される。サンプラ部10におけるオフセット付与量(±Voff)は、値D(n-1)がハイレベルである場合の第1信号のデータ遷移時刻の分布のピーク時刻と一致するよう調整され、値D(n-1)がローレベルである場合の第2信号のデータ遷移時刻の分布のピーク時刻と一致するよう調整される。復元されたクロック信号として、クロック信号CK,CKXの何れかが出力される。復元されたデータとして、デジタル値D(n)の時系列データが出力される。

(もっと読む)

クロックデータ復元装置

【課題】より正確にクロック信号およびデータを復元することができるクロックデータ復元装置を提供する。

【解決手段】クロックデータ復元装置1は、入力したデジタル信号に基づいてクロック信号およびデータを復元する装置であって、イコライザ部10、サンプラ部20、クロック生成部30、イコライザ制御部40および位相モニタ部50を備える。イコライザ部10、サンプラ部20およびイコライザ制御部40によるループ処理により、イコライザ部10におけるデジタル信号のレベル調整量の制御が行われるが、一方で、クロック信号CKとデジタル信号との間の位相差が所定値より大きいときには当該制御が位相モニタ部50により停止される。これにより、より正確にクロック信号およびデータが復元され得る。

(もっと読む)

発振装置および周波数検出装置

【課題】 中心周波数と周波数可変範囲を自在に設定できる高安定、高精度な電圧制御発振器を提供すること。

【解決手段】 第1の水晶発振器の第1の周波数成分と、第2の水晶発振器の第2の周波数成分とを加算器等で加算する等して、所望の中心周波数および所望の可変周波数範囲を作る。

(もっと読む)

161 - 180 / 265

[ Back to top ]