Fターム[5J106DD17]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | 計数(カウンタ)回路 (442)

Fターム[5J106DD17]の下位に属するFターム

可変カウンタ (28)

アップダウンカウンタ (62)

リングカウンタ (1)

Fターム[5J106DD17]に分類される特許

201 - 220 / 351

クロック位相シフト回路

【課題】プロセス条件、電源電圧、温度等の変動によらず、入力クロックの位相シフトの調整ができ、かつ、従来のDLL回路を用いた場合と比較して占有面積の小さいクロック位相シフト回路を提供する。

【解決手段】入力クロックを遅延させる遅延回路の遅延セルと同一の遅延セルで構成されたリングオシレータを用いて、入力クロックのm周期分の発振出力をカウントし、入力クロックの1周期分の遅延セル段数を計算して位相シフト量分の遅延セル段数を設定する。

(もっと読む)

位相ロック・ループ内のジッターを決定するためのオンチップ位相誤差計測のための装置。

【課題】 位相ロック・ループ内のジッターを決定するためのオンチップ位相誤差計測の方法及び装置を提供する。

【解決手段】 装置は、位相誤差信号を出力するように構成された位相・周波数検出器を含む位相ロック・ループPLL回路(100)を含む。位相誤差モニター回路(102)は、位相誤差信号を論理的に結合し、論理的に結合された位相誤差信号のパルス幅を各基準クロック・サイクルにおいてプログラム可能な遅延時間と比較して瞬時位相誤差変化を決定することにより、瞬時ピーク位相誤差を決定するように構成される。記憶素子(124)は瞬時位相誤差変化をストアするように構成される。

(もっと読む)

周波数切替え方法、周波数切替え装置および撮像装置

【課題】 回路規模が大きくなるのを抑えることができ、動作中に周波数を切り替えたときに異常動作が起きるのを防ぐことができる周波数切替え方法を提供する。

【解決手段】 出力信号の周波数を目標周波数に切り替えるときに、位相周波数比較器10とチャージポンプ回路11と逓倍設定回路14をリセット状態にし(S2)、逓倍数を目標周波数に対応した逓倍数C1に変更し(S4)、分周数を目標周波数に対応した分周数より大きい仮分周数2Nに変更する(S5)。その後、位相周波数比較器10とチャージポンプ回路11と逓倍設定回路14のリセット状態を解除して(S6)、分周数を目標周波数に対応した分周数Nに変更する(S8)。

(もっと読む)

PLL回路及びディスク装置

【課題】温度特性や経時変化がなく、線速度変化に合わせてループ特性をシームレスに補正できるPLL回路を提供する。

【解決手段】デジタルループフィルタ103は、位相比較器102が出力する位相誤差を入力し、デジタル周波数値を生成する。このデジタル周波数値は、D/A変換器104でアナログ電圧に変換され、VCO105は、D/A変換器104が出力する電圧に応じた周波数の同期クロックを出力する。位相比較器102が出力する位相誤差は、デジタルループフィルタ103の出力に所定の係数Aを乗じたものでゲイン補正され、デジタルループフィルタ103に入力される。デジタルループフィルタ103に入力する位相誤差を、出力クロック周波数に比例して変化させることで、PLLループ全体として、出力クロック周波数に依存して線形にループ特性が制御できる。

(もっと読む)

システムクロック供給装置及び基準発振器の周波数ずれ判定方法

【課題】システムクロック供給装置及び基準発振器の周波数ずれ判定方法に関し、装置内の基準発振器自身の周波数ずれを、測定用の発振器を用いずに判定し、周波数異常箇所を特定し、異常周波数クロックの送出を防ぐ。

【解決手段】二重化構成(N系及びE系)のシステムクロック供給装置内にそれぞれ備えられたOCXO等の基準発振器(#N,#E)9−1の出力クロックと、システム同期用に通常入力されるリファレンスクロック(例えば8KHz)とを、周波数ずれ測定部(#N,#E)1−1でそれぞれ比較し、所定回数の周波数ずれの発生を誤検出保護回路(#N,#E)1−2で測定し、該両系の測定結果を基に異常個所判定部(#N,#E)1−3で、自系若しくは他系の基準発振器(#N,#E)9−1の出力クロックの周波数ずれ又はリファレンスクロックの異常を判定して異常箇所を特定し、異常箇所を他系に切り替えるよう選択信号を送出する。

(もっと読む)

半導体集積回路

【課題】本発明は、Ser/Des回路において、休眠ステートからパワーアップの状態へ遷移した際の受信エラーを減少できるようにする。

【解決手段】たとえば、受信機21が、休眠ステートP1からパワーアップの状態P0に遷移したとする。すると、リセット制御回路21mは、ディレイ回路21m-1によって、PLL31からのシステムクロックのカウントを開始する。そして、ディレイ回路21m-1がXサイクルをカウントした後に、リセット制御回路21mは、ディジタルフィルタ21eおよびPI制御回路21fのリセットを解除するように構成されている。

(もっと読む)

多相クロック生成回路

【課題】従来の多相クロック生成回路では、出力クロック信号に任意の周波数プロファイルを設定することができなかった。

【解決手段】本発明にかかる多相クロック生成回路1は、基準クロック信号に基づき多相クロック信号を生成する位相ロックループ回路10と、多相クロック信号の周波数プロファイルを保持し、開始信号に基づき周波数プロファイルの出力を開始し、基準クロック信号に基づき任意の周期で周波数プロファイルを更新する周波数プロファイル保持回路20と、周波数プロファイルに基づいて多相クロック信号のうち任意の位相のクロック信号を選択し、選択したクロック信号を位相ロックループ回路10に帰還させるクロック選択回路30とを有することを特徴とするものである。

(もっと読む)

PLLロック検出回路および半導体装置

【課題】高精度のPLLロック検出信号を得るとともに、平滑回路を削除することができるPLLロック検出回路を提供する。

【解決手段】本発明に係るPLLロック検出回路は、PLL回路において、誤ってロック判定することなく、安定したロック状態においてロック判定とアンロック判定の両方を同時に行うことにより、確実なロック判定を行う。PLLロック状態が数H連続して継続しているかどうかの検出を行う連続性検出部と、PLLアンロック状態が数H連続して継続しているかどうかの判定行う連続性検出部を備え、これら連続性検出部によってPLLのロック状態が同時に検出され、その検出結果を保持するR−Sラッチ部を備えている。

(もっと読む)

PLL回路及び信号送受信システム

【課題】出力クロック信号のジッタ値に対するプロセスばらつきによる影響を抑える。

【解決手段】PLL回路として、基準クロック信号と出力クロック信号に基づくフィードバッククロック信号との間の位相差を検出する位相周波数比較回路と、前記位相差に応じて電流を出力するチャージポンプ回路と、前記チャージポンプ回路の出力を平滑化し、制御電圧として出力するローパスフィルタと、前記制御電圧、ゲイン制御信号、及びオフセット制御信号に応じた周波数の信号を生成し、前記出力クロック信号として出力する電圧制御発振回路と、前記制御電圧の変化に対する前記出力クロック信号の周波数の変化の比が目標値になるように、前記ゲイン制御信号を求めるゲイン調整回路と、前記制御電圧が所定の値である時における前記出力クロック信号の周波数が目標値になるように、前記オフセット制御信号を求めるオフセット調整回路とを備える。

(もっと読む)

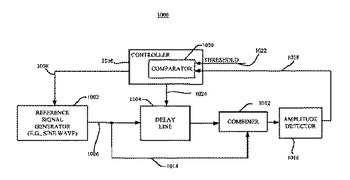

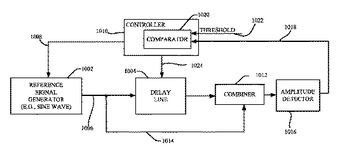

遅延線の較正

調整可能な遅延線は、目標値に、または希望の値の範囲内に遅延線の遅延を維持するように較正される。いくつかの態様において、遅延線を通った信号の累積的な遅延(例えばカウントにより示されるように)が、ある期間にわたって算定されるように、信号は遅延線を複数回通して渡される。前記カウントは、予定カウントと比較される。そして、この比較に基づいて、必要なときには、遅延線の遅延は調節される。いくつかの態様において、信号はデジタル信号を含み得る。いくつかの態様において、遅延線を通った遅延は、遅延線により信号に与えられた位相シフトにより引き起こされる信号における振幅変化の分析に基づいて算定され得る。いくつかの態様において、遅延線は、送信基準信号を生成する、および/または処理するように送信基準システムに組み入れられる。  (もっと読む)

(もっと読む)

遅延線の較正

調整可能な遅延線は、目標値に、または希望の値の範囲内に遅延線の遅延を維持するように較正される。いくつかの態様において、遅延線を通った信号の累積的な遅延(例えばカウントにより示されるように)が、ある期間にわたって算定されるように、信号は遅延線を複数回通して渡される。前記カウントは、予定カウントと比較される。そして、この比較に基づいて、必要なときには、遅延線の遅延は調節される。いくつかの態様において、信号はデジタル信号を含み得る。いくつかの態様において、遅延線を通った遅延は、遅延線により信号に与えられた位相シフトにより引き起こされる信号における振幅変化の分析に基づいて算定され得る。いくつかの態様において、遅延線は、送信基準信号を生成する、および/または処理するように送信基準システムに組み入れられる。  (もっと読む)

(もっと読む)

ジッタ発生装置

【課題】ジッタをデジタル的に発生させることにより、ジッタに関する調整が可能でありジッタ非注入時の信号劣化が生じることを防止したジッタ発生装置を提供する。

【解決手段】本実施の形態におけるジッタ発生装置では、第2カウンタ5が出力する−1〜1の範囲内のランダムな整数値のカウンタ値を第1カウンタ2が出力するカウンタ値に加算して、波形メモリ3にアドレスとして入力し振幅データから波形を得ることにより、ジッタをデジタル的に発生させ、波形20に対して波形21,22の波形の間をランダムにゆらいだ、ジッタが注入された波形を得ることが可能となる。

(もっと読む)

位相ロック・ループを制御する方法、利得制御装置及び位相ロック・ループ・システム

【課題】マルチ・ギガヘルツ範囲で動作し且つ低ジッタの、調整可能な利得を有する位相ロック・ループ(PLL)を提供する。

【解決手段】

1つの実施形態では、PLLのfVCO 信号の諸特性を取得する。これらの特性は、fVCO 信号及びPLLの位相ロック状態に関する異なるタイプのジッタの出現回数を含む。利得制御モジュールは、前記取得した諸特性の分析に基づき、少なくともPLLの一部を制御する。例えば、PLLが位相ロックされているか、又はループ・フィルタの漏洩がある場合、PLL内にあるチャージ・ポンプの利得が減少される。前記取得した特性に基づいて、チャージ・ポンプのミスマッチが検出される場合、当該ミスマッチを修正するために、追加の制御信号がチャージ・ポンプに供給される。

(もっと読む)

アンロック信号検出方法

【課題】

解決しようとする課題は、PLL回路において周期的及びバースト的に生じるアンロックの検出を正確に行い、また、周囲温度の変化にも柔軟に対応することができるディジタル信号回路の中核となるクロック系及び無線部の搬送周波数の基準となる周波数の異常を正確に判断することを可能にすることである。

【解決手段】

PLL回路におけるアンロック検出方法であって、予め定められた周期でサンプリングし、アンロックであればカウンタでカウントアップし、予め定められた周期回数でカウントアップした値と予め定められたしきい値を制御部で比較し、カウントアップした値が予め定められたしきい値を超えている場合にアラーム信号を出力すること実現した。

(もっと読む)

デジタル位相検知器及びデジタル位相検知信号の発生方法

【課題】フェーズロックループで使用可能なデジタル位相検知器において、サンプリングクロック信号を基準として高い位相分解能で入力クロック信号の位相を検知する。

【解決手段】サンプリングクロック信号はサンプリング14に対して、前もってデジタル的に調節可能な位相変位12へ露呈され、「補助サンプリングクロック信号」CK<1:8>が発生する。サンプリング14は位相検知信号PD OUTの第一のより上位のデジタルコンポーネントOUT1<9:0>を送給する。この第一のデジタルコンポーネントOUT1<9:0>の評価に基づいて、位相変位12が行われ且つ位相検知信号PD OUTの第二デジタルコンポーネントOUT2<12:0>が発生される。補助サンプリングクロック信号CK<1:8>は段階的に調節可能であり、それは各場合においてサンプリングクロック信号CKの1周期よりも小さい。

(もっと読む)

複数クロック間位相調整装置

【課題】従来の非同期データ受け渡しでは、送り側の信号変化周期を受け側の動作クロックの2倍以上にしておく必要があった。

ここで本発明では、この制限なく、非同期データの受け渡しを可能にすることを目的とする。

【解決手段】この目的を達成するために本発明では、非同期の関係にある2つのクロックから位相差量をパルス幅で抽出し、これを制御カウンタのクロックとして使用し、徐々にパルス幅が大きくなってカウンタが動作すると、遅延量制御部によって、一方のクロックの遅延量を制御し、一方のクロックが他方のクロックに追従する装置を提供する。

(もっと読む)

位相調整回路

【課題】システム高負荷動作中等における急激なPVT特性の変化による遅延量の変化に対応可能とする。

【解決手段】外部記憶手段とライトおよび/またはリードアクセスする際に、入力クロック信号の位相を調整して入力クロック信号に対して遅延された出力クロック信号を供給するクロック遅延調整回路100を利用して、外部回路から供給されるデータ信号およびデータストローブ信号の位相を調整する位相調整回路において、ライトデータおよび/またはリードデータを書き込む内部記憶手段と、ライトおよび/またはリードアクセスする際のタイミングマージンが確保されたときのクロック遅延調整回路の遅延パラメータの値を記録する内部記憶手段と、タイミングマージンの最適値を算出する最適値算出手段と、タイミングマージンの最適値を記録する最適値記憶手段と、を備えることを特徴とする。

(もっと読む)

位相同期ループ回路及び信号発生装置

【課題】回路規模の大幅な増大を招かずに、早期に所望の周波数を有する信号を出力することができる位相同期ループ回路及び当該回路を備える信号発生装置を提供する。

【解決手段】位相同期ループ回路1は、PLL部10と、PLL部10から出力される信号S1の周波数をPLL部10の同調周波数帯域に高速に引き込むためのプリチューン信号S26を生成するプリチューン信号生成部20とを備えている。プリチューン信号生成部20は、PLL部10から出力される信号S1の周波数をカウントするカウンタ21、カウンタ21でカウントされた信号S1の周波数とプリチューン周波数との誤差を示す誤差値が所定の閾値よりも小であるか否かを判定する誤差判定部23、及び誤差判定部23の判定によって誤差値が所定の閾値よりも小となるときのPLL部10に与えられるプリチューン信号S26を記憶するメモリ25を備える。

(もっと読む)

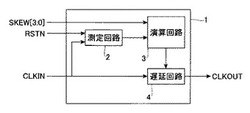

クロック信号源

【課題】周波数拡散させたクロック信号に対して正確な位相シフトを実現する。

【解決手段】周波数拡散クロック源40で周波数拡散されたクロック信号を位相シフタ30で位相シフトさせるとき、演算回路20に対して、周波数拡散クロック40から単位遅延セルの直列接続個数Nsを表す第1のコードを与え、この第1のコードの変化によって表される周波数拡散クロック源40の単位遅延セルの直列接続個数Nsの時間的変化、および希望するシフト量Saに基づいて、位相シフタ30における単位遅延セルの直列接続個数Npを表す第2のコードを生成する。

(もっと読む)

ディレイ調整回路およびその制御方法

【課題】同一チップ上の半導体素子のばらつきによる遅延特性のばらつきを補正するディレイ調整回路を提供すること。

【解決手段】ディレイ調整回路は、9段のディレイ素子が直列接続されるディレイ部と、ディレイ部の7段目の信号の立ち上がりエッジである第1エッジが第1基準信号の立ち上がりエッジである第1基準信号エッジよりも進んでいるか否かを検知する第1カウンタ10と、ディレイ部の9段目の信号の立ち上がりエッジである第2エッジが第1基準信号エッジよりも遅れているか否かを検知する第2カウンタ11と、第1カウンタ10において第1エッジが第1基準信号エッジよりも進んでおり、かつ、第2カウンタ11において第2エッジが第1基準信号エッジよりも遅れるように、基準信号Vbを補正して、ディレイ部のディレイ素子の遅延時間を調整する出力電流Ib1を出力するディレイ素子調整部と、を備えている。

(もっと読む)

201 - 220 / 351

[ Back to top ]