Fターム[5J106DD17]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | 計数(カウンタ)回路 (442)

Fターム[5J106DD17]の下位に属するFターム

可変カウンタ (28)

アップダウンカウンタ (62)

リングカウンタ (1)

Fターム[5J106DD17]に分類される特許

341 - 351 / 351

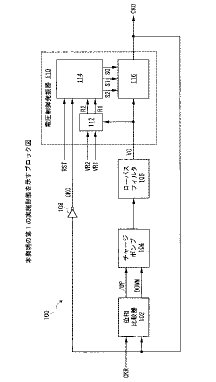

電圧制御発振器およびPLL回路

【課題】 電圧制御発振器の発振周波数範囲を広くし、かつ制御電圧のみにより発振周波数を調整する。

【解決手段】 電圧比較回路は、制御電圧が第1参照電圧より低いときに第1電圧比較信号を活性化させ、制御電圧が第2参照電圧より高いときに第2電圧比較信号を活性化させる。カウンタは、カウントクロックに同期して、第1比較結果信号の活性化中にカウンタ値を減少させ、第2比較結果信号の活性化中にカウンタ値を増加させる。発振回路は、複数の発振周波数帯域のいずれかをカウンタ値に応じて選択するとともに、選択した発振周波数帯域において制御電圧に応じて発振周波数を調整して出力クロックを出力する。これにより、動作条件の変動あるいは制御電圧の設定範囲の縮小に対して広い発振周波数範囲を確保でき、かつ電圧制御発振器の発振周波数を制御電圧のみにより調整できる。

(もっと読む)

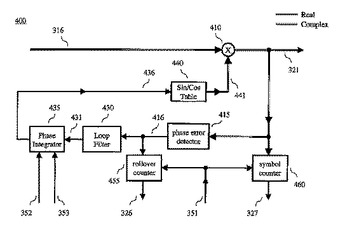

通信システムにおける搬送波再生で使われる方法および装置

受信機が搬送波再生を実行するためのデジタル式位相ロックループ(PLL)を含む。デジタル式PLLさらに硬判定によって駆動される位相誤差推定器と、該位相誤差推定器によって提供される位相誤差信号を累積する積分器とを含んでいる。引き込み時間を減らすため、デジタル式PLLは、搬送波周波数オフセットの推定が位相誤差信号の関数として決定される開ループモードで走らされる。搬送波周波数オフセットの推定値が決定されたあとは、決定された推定値が積分器に事前にロードされて、デジタル式PLLは閉ループモードで走らされる。

(もっと読む)

(もっと読む)

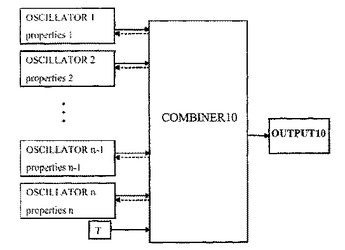

モノリシックなクロック・ジェネレータおよびタイミング/周波数リファレンス

電力節約モード、クロック・モード、リファレンス・モード、およびパルス化モードなどの複数の動作モードと共に、クロック・ジェネレータおよび/またはタイミングおよび周波数のリファレンスを提供する。共振周波数を有する第1の信号を供給するようになっている共振器と、増幅器と、温度に応じてこの共振周波数を修正するようになっている温度補償器と、製造プロセス変動に応じてこの共振周波数を修正するようになっているプロセス変動補償器とを含んでいる。さらに、実質的にこの共振周波数以下の対応する複数の周波数を有する複数の第2の信号に、この共振周波数を有する第1の信号を分周するようになっている周波数分割器と、これらの複数の第2の信号から1つの出力信号を供給するようになっている周波数セレクタとを含むことができる。  (もっと読む)

(もっと読む)

タイムスレービング装置

本発明はパケットデータ伝送ネットワークにおけるタイムスレービングのための装置に関する。各データパケットはタイムラベルを有しており、前記装置はネットワークから受信したパケットを受け取ることを目的とした一時記憶手段を有している。

本発明によれば、前記装置は、

一時記憶手段が、ネットワークの特性に依存した所定の時間(IPDV)の間に受信したデータを記録することのできる記憶容量を有している

ように構成されており、

前記装置はさらに、

入来パケットのタイムラベルに応じてローカル受信クロックを再生する手段と、

前記所定の時間(IPDV)と再生されたローカル受信クロックとに依存するある時点において一時記憶手段内のデータを読み取る手段

を有している。

(もっと読む)

LC発振器を備えたPLLの粗チューニング時間の改良

LC発振器のチューニング方法と装置が開示されている。本発明の実施形態は、ビット比較時間を適応的に制御し、最少の粗チューニング時間が得られるようにすることを含んでいる。ビット比較時間は、LC発振器のキャパシタアレイ内の対応する加重キャパシタの冗長量に逆比例してスケーリングされる。 (もっと読む)

基準発振器の周波数安定化

従来技術の不利な点を取り除き、特性(1)高い長期安定性、(2)低位相雑音、(3)高耐熱性、(4)その基準発振器の周波数についての正確な値、を改善したMEMS基準発振器を提供することが、本発明の目的である。  (もっと読む)

(もっと読む)

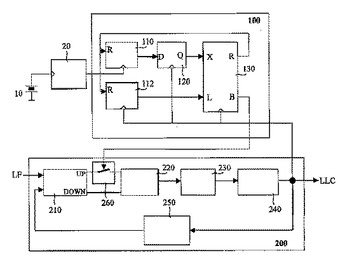

PLL回路

本発明は、位相又は周波数検出回路(210)の出力信号に応じて制御される発振回路(240)を有する位相同期ループ装置に関し、切替制御手段(130)は、所定の閾値周波数が供給される第1のタイマ手段(110)及び発振回路(240)の出力周波数が供給される第2のタイマ手段(112)の出力に応答して遮断信号を発生するように設けられる。遮断信号に基づいて、遮断手段(260)は、発振回路(240)への出力信号の供給を抑制する。これにより、PLL装置の出力周波数は、周波数閾値を超えて変化することが回避可能となるとともに、唯1つのPLL回路だけで済むことになる。

(もっと読む)

(もっと読む)

タイムベース用のレイアウト

【課題】シリコン共振器におけるように必ずしも温度安定性を必要としない周波数を有し、しかも周囲の熱的条件に係わらずに正確で低コストのタイムベースを得るために使用されることのできる共振器に基づいたレイアウトを提供すること

【解決手段】二つの発振器を含むタイムベースであって、その一つは、他方よりも低い周波数を有し、後者は断続的にスタンバイモードにセットされ、二つの発振器間の周波数差により第1安定時間基準(REF)、最も低い周波数を有する発振器の周波数を分周することにより得られる第2永久的時間基準(RTC)、及び、第1安定時間基準(REF)により決定される時間間隔の間に第1発振器(OSC1)により計数されるパルスに依存する除算因子を発生する。

(もっと読む)

電圧制御発振器の自走周波数の自動調整機能を有する位相ロックループ回路

【課題】 高度の安定性を有する基準クロック信号を発生するための回路を必要とせず、従って、動作安定性がそのような回路の安定性によって影響されることのない、電圧制御発振器(VCO)の自走周波数の自動調整機能を有するPLL回路を提供する。

【解決手段】 PLL回路20では、位相比較器26の比較結果信号が所定レベルにある期間中にVCO22が出力するパルス信号のパルス数をカウントし、そのカウント値に基づいて、マイクロコンピュータ32がディジタルデータを更新する。DAC36がそのディジタルデータに対応したアナログ信号を発生する。このアナログ信号と、位相比較器の比較結果信号をローパスフィルタ28で平滑化した信号とを、結合器30で加え合わせ、その加え合わせた信号をVCOの周波数制御信号とすることで、VCOの自走周波数が自動調整されるようにした。

(もっと読む)

位相同期回路、および、それを用いたシンセサイザ、通信装置

【課題】位相同期回路における入力クロックの同期に必要なエッジのみを検出し、異常入力クロック入力時や電源投入時でも、同期時間が短く、また、安定した出力クロックを供給できる位相同期回路を提供すること。

【解決手段】位相同期回路において出力クロックを分周する出力分周カウンタの出力値から、エッジ検出パルスを生成し、入力クロックの位相同期に必要なエッジのみを検出した入力分周クロックと出力分周クロックを位相比較器に入力することを特徴とする。

(もっと読む)

位相周波数検出器およびそれが組み込まれた位相ロックループ回路

【課題】 位相誤差信号に周波数差を加味した変形を加えることにより、周波数が離れているときでも短時間で位相同期を達成する。

【解決手段】 周波数が離れているときに生じる位相誤差信号の不連続なジャンプをジャンプ検出部30において検出し、検出信号により状態記憶部32の状態を遷移させる。保持部34において、状態記憶部32の状態に応じて位相誤差信号を修正して周波数位相誤差信号とする。

(もっと読む)

341 - 351 / 351

[ Back to top ]