Fターム[5J106DD17]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | 計数(カウンタ)回路 (442)

Fターム[5J106DD17]の下位に属するFターム

可変カウンタ (28)

アップダウンカウンタ (62)

リングカウンタ (1)

Fターム[5J106DD17]に分類される特許

81 - 100 / 351

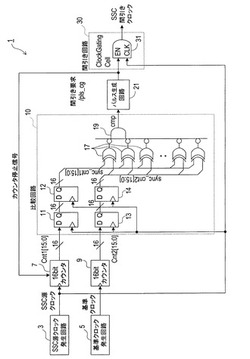

スペクトラム拡散クロック生成装置

【課題】生成されたスペクトラム拡散クロックを、各種タイミングを制御するカウンタのクロックとしても用いることのできるスペクトラム拡散クロック生成装置の提供。

【解決手段】SSC源クロック発生回路3,基準クロック発生回路5が発生するSSC源クロック,基準クロックは、16bitカウンタ7,9に入力されて、そのクロック数がカウンタ値cnt1,cnt2として計数される。カウンタ値cnt1,cnt2は、比較回路10に入力され、カウンタ値cnt1がカウンタ値cnt2よりも1以上大きくなると、比較回路10は比較結果cmpとしてLレベルの信号を出力する。すると、パルス生成回路21がLレベルの矩形パルス(間引き要求pls_cg)を出力し、AND回路31によりその間引き要求pls_cgとSSC源クロックとの論理積が計算されることによって、SSC源クロックが1クロック分間引かれる。

(もっと読む)

同期伝送装置及びジッタ抑圧方法

【課題】同期伝送装置及びジッタ抑圧方法に関し、入力クロックとシステムクロックの周波数偏差のゼロ交叉点付近で発生するピークジッタを抑圧する。

【解決手段】入力クロックを自装置内のシステムクロックでリタイミングした基準クロックを生成するディジタル回路15_1と、基準クロックに同期した出力クロックを生成するPLL回路15_2と、入力クロックの周波数偏差とシステムクロックの周波数偏差との接近を検出する周波数偏差接近検出部1_1と、該周波数偏差の接近が検出されたとき、該周波数偏差の差が増大するよう、システムクロックの発振器1_3の発振周波数を調整する周波数調整部1_2を備える。

(もっと読む)

クロック信号制御回路及びクロック信号制御方法

【課題】クロック信号の周波数制御をより好適に行うこと。

【解決手段】モニタ回路12のリングオシレータ16によるモニタ結果であるモニタ信号MSの周波数に応じて設定値記憶回路13からテーブル値TVALを出力させる。そして、そのテーブル値TVALに応じてクロック信号生成回路14のPLL回路15a,15bにより生成した発振信号と等しい周波数のクロック信号CLKを対象回路11に供給する。

(もっと読む)

送受信装置およびその動作方法

【課題】半導体チップ面積を低減して再生データと再生クロックの生成の誤動作の可能性を軽減する。

【解決手段】送受信装置7は、クロックデータリカバリ回路11、デシリアライザ15、シリアライザ14、PLL回路13、周波数検出器12を具備する。クロックデータリカバリ回路11は受信信号RXとPLL回路13から生成されるクロック信号TXCLKに応答して、再生クロックCLKと再生データDATAを抽出する。デシリアライザ15はCLKとDATAからパラレル受信データDTを生成し、シリアライザ14はパラレル送信データDRとTXCLKからシリアル送信信号TXを生成する。検出器12は受信信号RXとクロック信号TXCLKの周波数の差を検出して周波数制御信号FCSを生成して、信号FCSに応答して周波数の記差を低減するように、PLL回路13はTXCLKの周期を制御する。

(もっと読む)

PLL回路

【課題】位相比較周波数を高く保ち、PLLの位相雑音を改善し、出力信号の精度を向上させたPLL回路を提供する。

【解決手段】基準信号をクロックとして動作し所定範囲内でサイクリックにクロックが入力する度に予め設定された値を累積加算した基準信号の位相に相当する信号を出力する第1位相アキュムレータ1、発振器の出力信号をクロックとして動作し所定範囲内でサイクリックにクロックが入力する度に予め設定された値を累積加算した発振器の出力信号の位相に相当する信号を出力する第2位相アキュムレータ2、第1及び第2位相アキュムレータの出力信号を比較して差を求め基準信号と発振器の出力信号との位相差を示す出力信号を出力する位相比較器3、位相比較器の出力信号に従って発振器への制御信号を生成する制御部4、制御部からの制御信号に応じた周波数の信号を出力する上記発振器5を有す。

(もっと読む)

抵抗値調整回路

【課題】LSI内部の抵抗素子の抵抗値を精度よく且つ適時に較正する。

【解決手段】

複数の抵抗素子を有する半導体集積回路に設けられる抵抗値調整回路は、前記複数の抵抗素子のうち第1の抵抗素子に基準電圧を印加して第1の抵抗素子の抵抗値に反比例する定電流を生成し、前記半導体集積回路の外部のコンデンサに前記定電流を供給する定電流源と、前記コンデンサに前記定電流が供給されるときに、前記コンデンサの電圧が所定電圧上昇する時間を計測する充電時間計測部と、予め設定された基準充電時間と前記計測された計測充電時間の差分に基づいて前記複数の抵抗素子のうち第2の抵抗素子の抵抗値を較正するキャリブレーション部を有する。LSI外部のコンデンサは容量が既知であり、LSIの製造プロセスのばらつきに依存しないので、基準充電時間と計測充電時間の差分に基づいて、精度よく抵抗値を較正できる。

(もっと読む)

位相同期ループ回路および通信機

【課題】低消費電力化と小型化とが両立されたPLL回路を提供する。

【解決手段】PLL回路の位相比較器2は、カウンタ16と時間デジタル変換器13とを含む。カウンタ16は、参照クロック信号REFと、デジタル制御発振器の出力を分周した低周波クロック信号CLKAおよび高周波クロック信号CLKBとを受ける。カウンタ16は、高周波クロック信号CLKBのクロック数をカウントすることによって参照クロック信号REFと低周波クロック信号CLKAとの位相差を検出する。時間デジタル変換器13は、参照クロック信号REFと低周波クロック信号CLKAとを受ける。時間デジタル変換器13は、カウンタ16の出力が所定範囲になってから、参照クロック信号REFと低周波クロック信号CLKAとの位相差を、高周波クロック信号CLKBの周期よりも短い時間の精度で検出する。

(もっと読む)

半導体集積回路装置

【課題】プロセスモニタに必要な回路面積を増加させることなく、高精度なプロセスキャリブレーションを短時間で行う。

【解決手段】ディジタル制御発振器38が任意の発振バンドを選択した後、制御部25はTDC41の信号がプロセスモニタ制御部40に入力されるようにスイッチ44を切り換える。TDC41は、信号VREFの立ち上がりエッジと最も近い信号VPREの立ち上がりエッジの期間をディジタル値に、信号VREFの立ち上がりエッジと2番目に近い信号VPREの立ち上がりエッジの期間をディジタル値に変換し、その差を算出する。プロセスモニタ制御部40は、ルックアップテーブルを参照し、算出した値と予め設定されている期待値とを比較し、プロセス値を決定する。そのプロセス値は、プロセス信号として調整制御部26にそれぞれ出力され、プロセスキャリブレーションが行われる。

(もっと読む)

信号受信装置、信号受信装置の制御方法及びコンピュータプログラム

【課題】1つの位相比較器及びループフィルタを複数の同期保持チャネルで共有することで、同期保持チャネルの増加に伴う回路規模の増大を抑えることが可能な信号受信装置を提供すること。

【解決手段】所定の周波数のキャリアを生成する信号生成器を含む位相同期ループ部と、衛星から受信した信号のキャリアと信号生成器が生成したキャリアとの位相差を検出して出力する1以上の位相比較器と、位相比較器が出力する位相差情報からノイズを除去して所望のループの応答を実現する1以上のループフィルタと、を備え、同時に追跡可能な最大衛星数N(Nは2以上)に対して、位相比較器及びループフィルタの数MはN>Mである、信号受信装置が提供される。

(もっと読む)

PLL回路および電圧制御発振器

【課題】PLL回路のデッドロック状態になることを防止する

【解決手段】閾値判定部13aは、制御電圧の高低を示す制御信号を生成する。制御部13bは、制御信号に応じた制御値を出力し、制御値が発振周波数の上限および下限について最も高い対応関係を示す場合において制御信号が高を示すとき、および制御値が発振周波数の上限および下限について最も低い対応関係を示す場合において制御信号が低を示すときのいずれか一方を満たす際、所定の制御値を出力する。発振器13cは、制御電圧と発振周波数との対応関係が発振周波数の上限および下限が異なるように複数定められていると共に対応関係が複数の制御値と対応付けられており、制御値が示す対応関係における制御電圧に応じた発振周波数を有する出力信号を出力する。

(もっと読む)

スペクトラム拡散クロック生成器及び半導体装置

【課題】回路規模の大きなDACやアナログ変調回路を用いずに理想的な周波数特性を得ることが可能なスペクトラム拡散クロック生成器及びスペクトラム拡散クロック生成器を備えた半導体装置を提供する。

【解決手段】動作クロックを生成する電圧制御発振器と、動作クロックの位相と基準クロックの位相とを比較し比較結果により電圧制御発振器の発振の基準となる電圧を生成する帰還制御部と、動作クロックの周波数に変動を与える成分をデルタシグマ変調したパルス信号として生成する変調パルス生成部と、パルス信号の振幅を設定するレベル設定部と、帰還制御部が生成した電圧とレベル設定部によって振幅が設定されたパルス信号とを加算する加算部と、加算部の出力信号を濾波して電圧制御発振器に与える制御電圧を生成する低域パスフィルタと、を備える。

(もっと読む)

通信装置及びその折り返し試験方法

【課題】SSCのジッタを抑制し、SSCの変調度を滑らかに遷移させることが可能なSSC生成機能を有するPLL回路及び通信装置を提供する。

【解決手段】SSCコントローラ18は、SSCの変調プロファイルに応じて予め定められたタイミングで位相シフト量を変更するよう位相補間器15を制御し、出力クロック信号C_OUTの変調度を周期的に変更させる。さらに、SSCコントローラ18は、帰還クロック信号C_FBの一周期内において位相補間器15より出力される位相シフト信号C_PSに与える総位相シフト量を、当該総位相シフト量と直前の一周期における総位相シフト量との差分が常に基本遅延量Δ以下となるよう制御する。ここで、基本遅延量Δは、出力クロック信号C_OUTの周期T_OUTを位相補間器15の位相分解能Nrで除算した値(つまり、T_OUT/Nr)である。

(もっと読む)

多相発振器を有する位相ロックループ

位相ロックループが複数のデジタル入力を有する多相発振器を利用する。時間に関して互いにオフセットされた複数のDQフリップフロップが、複数の制御信号を生成して、発振器から制御位相情報をデジタル形式で取り出す。発振器における任意の2つのデジタル入力間に接続されたDQフリップフロップが、進行波の方向を判定する。その方向と位相情報とにより、ルックアップテーブルがアドレス指定され、発振器の現時点のフラクショナル位相が判定される。発振器周波数を低減するために、N分周回路が用いられる。発振器に関する全位相表示信号が、現時点のフラクショナル位相を用いて判定される。この全位相を基準位相と比較して、発振器に対する修正を行うための制御信号を生成する。フィードフォワード経路において、分周器が、発振器からの高周波信号をより低い所望の周波数に分割し、それにより位相分解能を向上させる。 (もっと読む)

時間デジタル変換器

【課題】時間遅延量の最適値制御が行える時間デジタル変換器を提供すること。

【解決手段】入力されるクロック信号を多段に遅延する複数の遅延段を有し、該複数の遅延段の少なくとも1つが可変遅延段である遅延回路と、前記遅延回路の遅延段と同数個設けられ、参照信号の入力に応答して並列に対応する遅延段の出力を取り込む複数のフリップフロップと、前記複数のフリップフロップの各出力の立ち上がりと立ち下がりの一方または両方を検出するエッジ検出回路と、前記エッジ検出回路が検出したエッジ数をカウントするカウンタ回路と、前記カウンタ回路がカウントしたエッジ数に応じて前記可変遅延段の遅延量を制御する制御回路とを備える。

(もっと読む)

デジタルフェーズロックドループ回路

【課題】安定した位相同期ループを構成できない。

【解決手段】本発明は、第1、第2のクロック信号をカウントする第1、第2のカウンタと、第1のクロック信号を遅延させた第1、第2の遅延クロック信号を生成する遅延クロック生成回路と、第1のクロック信号及び第1、第2の遅延クロック信号のそれぞれで第2のカウンタのカウント値をサンプリングするサンプル回路と、第1、第2のクロック信号を所定の数で分周した第3のクロック信号との位相差と、サンプリングしたカウント値に応じ、そのサンプリングしたカウント値のうち1つを選択する選択回路と、第1のカウンタ及び選択回路が選択したカウント値に応じて第1、第3のクロックとの位相差を演算する位相誤差演算回路と、位相誤差演算回路の演算結果に応じて第2のクロックを出力するデジタル制御発振器とを有するデジタルフェーズロックドループ回路である。

(もっと読む)

PLL回路

【課題】温度変動による位相雑音の悪化を低減することが可能なPLL回路を提供することを目的とする。

【解決手段】電圧制御発振回路81と、分周器82と、基準信号REF-INと発振信号Outputとの互いの位相を比較し、位相差に応じたパルス幅のパルス信号UP、DOWNを出力する位相比較器と、パルス信号UP、DOWNのパルス幅に応じた大きさのCP電流ICPp、ICPnを出力する出力電流補正機能付きチャージポンプ1と、CP電流ICPp、ICPnに応じてVt電圧を制御するループフィルタ85と、温度変動に応じて遅延時間が変化する遅延回路8とを備えてPLL回路100を構成し、遅延回路8の遅延時間に基づいて、CP電流ICPpとCP電流ICPnとの差が小さくなるように、CP電流ICPp又はCP電流ICPnを補正する。

(もっと読む)

クロック生成回路

【課題】位相ロックの精度を向上する。

【解決手段】クロック生成回路は、出力クロックの周期または位相を段階的に遅延する第1の遅延回路および前記第1の遅延回路の遅延時間を設定し制御する第1のカウンタを有する逓倍回路と、前記逓倍回路内の第1の遅延回路から出力された前記出力クロックを入力し、前記出力クロックを所定時間遅延させる第2の遅延回路および前記第2の遅延回路の遅延時間を設定し制御する第2のカウンタを有する位相同期回路を備え、前記逓倍回路は、初期値が第1の値であり第1のカウンタのカウンタ値が一定時間以内で変化しない場合に第2の値が設定される第3のカウンタをさらに有し、前記第3のカウンタのカウンタ値が前記第1の値から前記第2の値に変化した時、前記第2の遅延回路の遅延時間が前記第1の遅延回路の遅延時間と同じかあるいは少し長い遅延時間となるように前記第2のカウンタのカウンタ値を設定する。

(もっと読む)

デューティ検出回路及びこれを備えるクロック生成回路、並びに、半導体装置

【課題】デューティ検出信号を高頻度に更新する。

【解決手段】内部クロックRCLK,FCLKのデューティを検出する複数のデューティ検出部210−1〜210mと、複数のデューティ検出部を互いに異なる位相で動作させる制御部220と、複数のデューティ検出部からのデューティ検出信号を選択する出力選択部230とを備える。本発明によれば、複数のデューティ検出部が互いに異なる位相で動作することから、各デューティ検出部におけるデューティ検出信号の生成頻度よりも高頻度でデューティ検出信号DCCSを出力することが可能となる。このため、本発明によるデューティ検出回路をDLL回路のクロック調整に使用すれば、DLL回路の制御周期を短縮することが可能となる。

(もっと読む)

信号処理装置

【課題】 温度によるクロックの変動を抑える。

【解決手段】 クロックを用いて信号を生成する信号処理部と、外部からの入力信号と前記信号処理部から出力された信号との位相差を検出し、前記位相差を示す信号を出力すると共に前記入力信号が無くなるとその直前の位相差の信号を出力する位相差検出部と、温度補償型の発振器からの出力信号に応じて前記位相差検出部からの出力に応じた値をカウントし、前記カウント値に基づいて基準信号を生成するデジタル発振器と、前記デジタル発振器からの基準信号と前記クロックを分周した信号との位相差に応じて前記クロックを生成するクロック生成部とを備える。

(もっと読む)

発振器および位相同期ループ

【課題】発振器の位相雑音を低減し、位相同期ループの消費電力および位相雑音を低減する。

【解決手段】発振器は、共振回路の容量値に応じて発振周波数が可変する構成であって、外部から入力する外部クロックと設定データに応じて、オーバーフロー信号を間欠的に出力するアキュムレータ11と、オーバーフロー信号の間欠入力に応じてオン・オフするスイッチ12と、スイッチ12を介して共振回路に接続される固定容量値を有する容量素子C2とを備え、設定データに応じて間欠的に出力されるオーバーフロー信号の入力によりスイッチ12がオンとなるオン時間における発振周波数と、オーバーフロー信号が入力されないときにスイッチ12がオフとなるオフ時間における発振周波数との間で、オン時間とオフ時間の時間割合に応じた平均発振周波数を可変させる。

(もっと読む)

81 - 100 / 351

[ Back to top ]