Fターム[5J106DD17]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | 計数(カウンタ)回路 (442)

Fターム[5J106DD17]の下位に属するFターム

可変カウンタ (28)

アップダウンカウンタ (62)

リングカウンタ (1)

Fターム[5J106DD17]に分類される特許

141 - 160 / 351

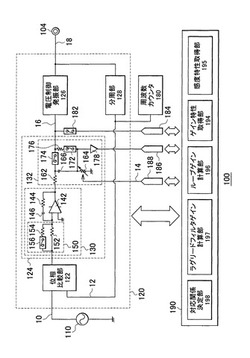

発振器および位相同期回路のループ帯域補正方法

【課題】安定した高周波信号を発振する発振器および位相同期回路のループ帯域補正方法を実現する。

【解決手段】基準周波数の基準信号を発生する基準信号発生部と、前記基準信号とフィードバック信号との位相差に応じた電圧を出力する位相比較部と、前記位相比較部から出力された電圧が入力され、外部制御信号により、前記位相比較部から出力された電圧のゲインを調整するループフィルタと、前記ループフィルタによりゲインが調整された調整信号に応じた周波数の出力信号を発振する電圧制御発振部と、前記出力信号を分周した分周信号を前記フィードバック信号として前記位相比較部にフィードバックする分周部とを備える。

(もっと読む)

周波数変調機能付きクロック生成回路

【課題】良好なスペクトラム拡散効果を有し、ノイズの発生が少なく周辺回路や電子部品の誤動作を低減することができる周波数変調機能付きクロック生成回路を提供する。

【解決手段】クロック生成回路1は、帰還用分周器17を有し、周波数変調されたクロックを出力するPLL回路10と、帰還用分周器17から所定の周波数のみ取り出しPLL回路10に入力するバンドパスフィルタ20と、三角波を生成する三角波生成回路40とを有し、バンドパスフィルタ20は、サイン波生成器としても機能し、所定のタイミングでサイン波を生成して三角波と合成して帰還用分周器17の分周比を変化させる。

(もっと読む)

タイミング信号発生回路

【課題】 種々の時間間隔のタイミング信号を低コストで正確に発生させる。

【解決手段】 クロック回路と、クロック信号を入力するカウント回路と、外部から入力する基準タイミング信号を取得し、少なくとも2以上の基準タイミング信号を含む所定の2時点間のカウント回路のカウント値の増分と、該2時点間の時間とを対応させて記録する記憶回路と、カウント回路が所定の2時点間に対応するカウント値だけ増分した時点を中心とする所定の期間に基準タイミング信号を取得し、基準タイミング信号を受信した時点のカウント回路のカウント値を所定の2時点間に対応するカウント値として記録し、所定の2時点間の時間を周期とするタイミング信号をカウント回路のカウント値の増分を契機として発生させ、さらに基準タイミング信号を取得し、基準タイミング信号を取得した時点からカウント値の増分を計数し直す制御手段とを備える。

(もっと読む)

位相同期ループ回路の制御方法及び位相同期ループ回路

【課題】ロックアップ時間を短縮すること。

【解決手段】PLL回路20の位相比較器23は、基準信号frと比較信号fpの位相を比較し、両信号fr,fpの位相差に応じた信号を出力する。ループフィルタ25は強誘電体容量C1を含み、位相比較器23の出力信号に応じたチャージポンプ24から出力される位相差電流IPにより直流電圧を生成するとともに、その直流電圧を平滑化して制御電圧VCを生成する。VCO26は、制御電圧VCに応じた周波数の出力信号foを生成する。カウンタ31は、入力信号fiをカウントし、カウント値と第1の設定値,第2の設定値とを比較し、第1の期間、強誘電体容量C1を高電位電源VDDの電源線に接続し、第2の期間、強誘電体容量C1と低電位電源VSSの電源線を接続する。

(もっと読む)

ディジタル位相検出器およびPLL

【課題】従来のディジタル位相検出器は、遅延素子としてインバータ等の遅延時間を使用しているが、遅延素子の配置および配線の固定が必要であることからゲート・アレイやFPGA等ではインプリメントすることが難しい。遅延素子の遅延時間はデバイスの種類やプロセスばらつきにより変動するため位相検出の精度に影響が出る。

【解決手段】2つのクロックが整数比に近い周波数を有している場合において、第1のクロックを入力とするM/N逓倍する逓倍器と、逓倍器の出力クロックを用いて第2のクロックをラッチするF/Fと、F/Fの出力を微分する微分回路と、逓倍器の出力クロックを入力とするカウンタと、微分回路の出力に応じて前記カウンタの出力を保持するラッチ回路と、ラッチ回路の出力を加算する第1の加算器と、第1の加算器の出力を固定値から減算する第2の加算器と、第2の加算器の出力を順次積算する積算器と、を備えるよう構成する。

(もっと読む)

位相同期ループ回路

【課題】ループ利得の変動を抑圧できるループ利得検出回路を備えたPLL回路を提供する。

【解決手段】PLL回路内の電圧発振器1で駆動されるカウンタ6と、その出力を周期的に積算するアキュームレータ(ACL)と、ACLのカウント値とレジスタ9に予め設定された設計値とを比較する比較演算回路部8を設け、ACLのカウント値がループ利得と反比例することを応用してPLL回路のループ利得を検出する。検出結果に基づいてチャージポンプ電流等でループ利得の補正を行ってループ利得を校正する。これにより、PLL回路は、PLLを構成する各素子の特性のばらつきに影響しない安定したループ特性を保つことができる。

(もっと読む)

発振回路、発振回路を備えた電子機器及び発振回路の制御方法

【課題】高精度発振器間の位相同期を間欠動作にすることにより低消費電力化する。

【解決手段】基準となる周波数の基準信号Frefを出力する周波数確度が高い高精度発振器100と、出力信号Foutの周波数を制御電圧Vcで制御する電圧制御発振器110と、基準信号Frefの位相と出力信号Foutの位相との位相差を検出し位相差信号Poを出力する位相比較部120と、位相差信号Poに基づき制御電圧Vcを生成する制御電圧生成部130と、位相比較部120への電源VDDの接続を接続状態または非接続状態に切り替えるスイッチ回路140と、位相差信号Poに基づき位相差が無くなった時点から所定の時間が経過するまでの期間はスイッチ回路140を接続状態にし、期間以外はスイッチ回路140を非接続状態にする制御信号Swを出力するタイマ回路150と、を含む発振回路1。

(もっと読む)

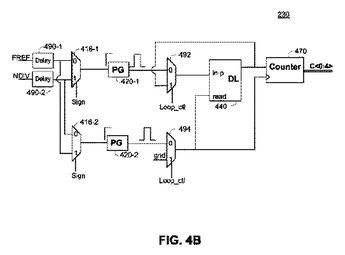

小数位相検出器を用いたクロック生成

入力信号から、低減されたスキューを有する1つまたはより多くの出力クロック信号を生成する回路が提供される。入力信号は、出力クロック信号の周波数とは異なった周波数を有するオリジナルクロックの遷移から導き出される遷移を有する。出力クロック信号の周波数は、入力信号についての周波数と、整数比との乗算からの積である。回路は、積算器と、小数位相検出器と、ループフィルタを含む。積算器は、数値的オフセット値を数値的位相値に周期的に追加する。出力クロック信号は、この数値的位相値から生成される。小数位相検出器は、数値的位相値から、入力信号の遷移の各々についてのそれぞれの数値的位相誤差を生成する。ループフィルタは、それぞれの数値的位相誤差のフィルタリングから数値的オフセット値を生成する。  (もっと読む)

(もっと読む)

PLL回路

【課題】ディジタル回路で構成されるADPLLにおいて、位相差0近傍における位相差検出を改善することができる技術を提供する。

【解決手段】基準信号VREFフィードバック信号VDIVとの位相及び周波数を比較するPFDと、PFDの出力をディジタル値に変換するTDCと、TDCの出力から高周波雑音成分を除去するDLFと、DLFの出力に基づいて制御されるDCOと、DCOの出力を分周しフィードバック信号VDIVを出力するDIVによりフィードバックループが構成される。フィードバックループのいずれかの箇所にオフセット値が加算され、フィードバック信号VDIVの位相が制御され、ロック時にもTDCに0ではない値が入力される。

(もっと読む)

クロック発生機能付き装置、基準周波数等設定方法、および基準周波数等調整方法

【課題】クロックに関する設定を簡単に行う。

【解決手段】VCXOと、基準周波数とこの基準周波数のクロックをVCXOに発生させる電圧のレベルである基準レベルとを記憶するメモリと、必要な周波数のクロックを、メモリに記憶されている基準周波数および基準レベルを基準に求められる電圧をVCXOに与えて発生させるD/Aコンバータ制御部およびD/Aコンバータと、を有する装置において、下記の処理を行う。試験時レベルを適宜変化させながら、各試験時レベルに応じた電圧をVCXOに与えて試験用クロックを発生させる。試験用クロックを周波数カウンタに出力する。試験用クロックの周波数と目標周波数との差が所定の範囲内であることが周波数カウンタによって確認できたら、メモリに、この試験用クロックがVCXOによって発生された際の試験時レベルを基準レベルとして記憶させ、この試験用クロックの周波数を基準周波数として記憶させる。

(もっと読む)

周波数ダイバース離散時間位相ロックデバイス及び装置

【課題】周波数ダイバース離散時間位相ロックデバイスを提供する。

【解決手段】デジタル−アナログ変換器(DAC)、及び、該DACからの入力に基づいてクロック信号を与えるように動作する発振器を含む、アナログセクションと、デジタルシグナルプロセッサ(DSP)とを備えており、このデジタルシグナルプロセッサは、ループコントローラ状態機械と、位相検出器309と、発振器からのクロック信号を受信すると共に、前記位相検出器にカウント値を与えるように動作するカウンタ307と、基準信号310を受信すると共に、前記位相検出器に基準パルス312出力を与えるように動作する分周器と、相検出器309からの出力に基づいて、制御目標値320を与えるように動作するループフィルタ302とを備えており、前記位相誤差値に基づいて、前記発振器の出力が、前記位相誤差を定常状態値まで低減するように変更される。

(もっと読む)

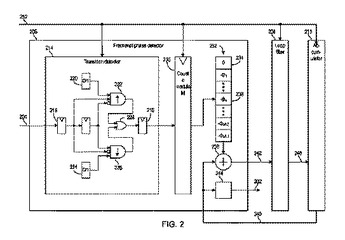

完全デジタル位相ロックループにおける位相デジタル変換器

位相デジタル変換器と、完全デジタル位相ロックループと、完全デジタル位相ロックループを有する装置とについて、本明細書で説明する。位相デジタル変換器は、時間デジタル変換器を駆動する位相周波数変換器を含む。時間デジタル変換器は、位相周波数変換器によって出力された位相差の絶対値と符号とを判断する。時間デジタル変換器は、タップ付き遅延線とループフィードバックカウンタとを利用して、ループ追跡プロセスによくある小さいタイミング差およびループ収集プロセスによくある大きいタイミング差の測定を可能にする。タップ付き遅延線は、基準期間の部分の測定を可能にし、基準クロックの速度に関する要件を低減することによって位相デジタル変換器のより低電力の動作を可能にする。  (もっと読む)

(もっと読む)

PLL回路

【課題】PLLのロック時間を高速化する。

【解決手段】PLLを構成するローパスフィルタ107に対して回路の最大電圧を与えて充電する。その過程でクロック計数カウンタ102が基準クロック10の一周期におけるVCO出力クロックの数をカウントし、所定の2時点でのカウント値により基準クロックとVCO出力クロック27に対する分周クロックとのロックポイントにおける位相差を推定する。この推定は、演算処理回路105において、VCO個体のカタログデータに基づいて行ない、カウンタロード値24を算出し、分周カウンタ109はこれを分周信号28、位相比較器106は該推定位相差とし、充電後にローパスフィルタに供給する。

(もっと読む)

周波数補正回路及びそれを用いた無線通信装置

【課題】 発振器の出力周波数が増減した場合に自動補正を可能として常に出力周波数の精度を一定の範囲内に維持する周波数補正回路を得る。

【解決手段】 発振器2の発振周波数よりも高精度の基準周波数を、発振周波数を分周した分周周期毎に計数するカウンタ5と、発振周波数が正常な時のカウンタの計数値に相当する正常値に対して所定値Mを加算した値とカウンタの計数値とを比較して一致したときに発振周波数の減少を示す信号を生成する比較回路7と、正常値に対してMを減算した値とカウンタの計数値とを比較する比較回路8と、この比較回路8の一致結果に応答してこの一致結果を所定時間マスクするためのマスク信号を生成する単安定マルチバイブレータ11と、比較回路7の減少を示す信号に応じて発振周波数を減少方向に制御し、マスク信号の非生成時に発振周波数を増加方向に制御する制御回路12及びCPU1とを含む。

(もっと読む)

半導体集積回路装置および逓倍クロック生成方法

【課題】 エージング時に使用可能な同期逓倍クロック発生回路を提供することである。

【解決手段】 可変ディレイヤを用いた発振回路と、カウンタを用いた発振周波数制御回路とを有し、入力クロック周波数の逓倍の周波数のクロックを発生するクロック発生回路において、上記発振回路を入力クロックに同期させて動作させることで、入力クロックと同期した逓倍クロックを発生させる。

(もっと読む)

発振器制御装置

【課題】安定した位相雑音特性を高速に得ることができる発振器制御装置を提供する。

【解決手段】動作電流制御信号に基づく動作電流を供給する可変電流源14を含み、発振器調整ワードに応じた発振周波数の発振信号を出力するデジタル制御発振器1と、前記発振信号と基準信号との間の位相差を算出し、位相差信号を出力する位相差算出部(2,3,4)と、前記デジタル制御発振器の発振周波数を設定するための周波数命令ワードと前記位相差信号との差分を平滑化して、前記発振器調整ワードを出力するフィルタ6と、前記発振器調整ワードを測定し、前記動作電流制御信号を出力する制御部7と、を備え、前記制御部は、前記動作電流の値を変化させるように前記動作電流制御信号を出力し、前記発振器調整ワードが極大値となる前記動作電流の値を抽出し、前記可変電流源が供給する動作電流がこの抽出した値となるように前記動作電流制御信号を出力する。

(もっと読む)

パルス位相調整方法および装置

【課題】事前に位相ずれの評価や調整を行うことなく、フレームパルスとクロックとの間の位相変化を自動調整することができる。

【解決手段】位相制御部30により、位相調整部10での入力クロックCLKinに対する位相調整量を変化させて、レーシング検出部20により、このような危険なレーシング状態を検出し、位相制御部30により、その時の最悪位相調整量に基づいて、入力フレームパルスFPinを安定してラッチできる最適位相調整量を決定する。

(もっと読む)

半導体集積回路

【課題】クロック信号生成部をディジタル制御するレジスタへの制御情報の格納ステップを削減すること。

【解決手段】半導体集積回路は、クロック信号CLKmを生成するディジタル制御信号生成部10、ディジタル制御部20を具備するクロック生成部を含む。クロック生成部は、位相周波数比較器31、制御レジスタ22を更に具備する。比較器31には、基準信号CLKinとフィードバック信号Moutが供給される。制御レジスタ22に比較器31の出力信号FDoutが供給され、制御レジスタ22は複数ビットのディジタル制御情報を格納する。クロック生成部は、複数のロック動作のための複数の初期設定データを予め格納する制御データ記憶回路25を更に具備する。動作選択情報Minに応答して制御データ記憶回路25から初期設定データSet1〜Set5が、制御レジスタ22の上位ビットに格納される。

(もっと読む)

周波数制御回路およびCDR回路

【課題】調整のための外部接続端子を必要とする部品や外部接続部品を必要とする部品を不要にする。

【解決手段】CDR回路は、周波数制御回路と、制御電圧に応じて発振周波数が制御されかつ入力データにより発振位相が制御される再生クロックを生成する第1のVCO2と、再生クロックによって入力データのデータ識別を行うFF1と、制御電圧に応じて発振周波数が制御される第2のVCO3とを備える。周波数制御回路は、第2のVCO3の出力信号の周波数を参照クロックの周波数と比較し、検出した周波数差に応じた信号を出力する周波数比較器4と、周波数比較器4の出力信号に応じて出力するデジタル値を上下させるアップダウンカウンタ5と、アップダウンカウンタ5の出力をアナログ信号に変換してVCO2,3の制御電圧として出力するD/A変換器6とから構成される。

(もっと読む)

PLL回路、無線端末装置、および周波数検出方法

【課題】DCOの最低発振周波数を検出し、分周比Nに比例した制御データから、DCOの制御データへの変換を精度良く行うことが可能な、新規かつ改良されたPLL回路を提供すること。

【解決手段】ディジタル値を用いて制御される発振回路を有するPLL回路であって、搬送波周波数値を設定する搬送波周波数設定部と、搬送波周波数値が変化したことを検出する検出部と、搬送波周波数値が変化したことを示す信号に同期して、発振回路を最低周波数で発振させるための制御信号を送信し、基準周波数の1周期内の発振回路の出力クロック数を計測する計測部と、を含むことを特徴とする、PLL回路が提供される。

(もっと読む)

141 - 160 / 351

[ Back to top ]