Fターム[5J106DD17]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | 計数(カウンタ)回路 (442)

Fターム[5J106DD17]の下位に属するFターム

可変カウンタ (28)

アップダウンカウンタ (62)

リングカウンタ (1)

Fターム[5J106DD17]に分類される特許

1 - 20 / 351

自励発振型D級アンプおよび自励発振型D級アンプの自励発振周波数制御方法

PLL回路

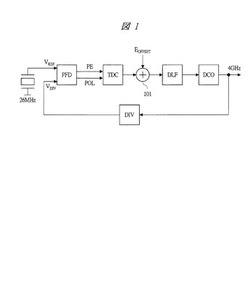

【課題】ディジタル回路で構成されるADPLLにおいて、位相差0近傍における位相差

検出を改善することができる技術を提供する。

【解決手段】基準信号VREFフィードバック信号VDIVとの位相及び周波数を比較するPFDと、PFDの出力をディジタル値に変換するTDCと、TDCの出力から高周波雑音成分を除去するDLFと、DLFの出力に基づいて制御されるDCOと、DCOの出力を分周しフィードバック信号VDIVを出力するDIVによりフィードバックループが構成される。フィードバックループのいずれかの箇所にオフセット値が加算され、フィードバック信号VDIVの位相が制御され、ロック時にもTDCに0ではない値が入力される。

(もっと読む)

位相同期回路及び位相同期回路制御方法

【課題】少ない分周数を用いた小数点以下の分周における位相の同期を精度良く行う位相同期回路及び位相同期回路制御方法を提供する。

【解決手段】位相比較器3は、基準クロックと比較クロックとの位相差を電流に変換して出力する。キャパシタ4は、位相比較器3から入力された電流に応じて電圧を出力する。VCO6は、キャパシタ4から入力された電圧によって出力周波数を制御し、当該出力周波数を有する信号を出力する。可変分周器7は、VCO6から出力された信号を所定の周期で異なる値に分周することで、小数点以下の値を有する分周を行なった比較クロックを生成する。パルスカウンタ8は、可変分周器7から出力された比較クロックの数をカウントする。補償係数計算部9は、パルスカウンタ8のカウント数を基に、キャパシタ4に対する電流及び電圧の補償値を取得する。DAC11は、前記補償値を基に、キャパシタ4に対して電流を流し補償を行う。

(もっと読む)

半導体装置

【課題】半導体装置の入出力クロックスキューを抑制する。

【解決手段】I/O電圧電源で駆動される第1のバッファ1及び第2のバッファ8と、I/O電圧電源の電圧レベルを示す電圧判定信号を生成する電圧判定部5と、第1のバッファ1を介して入力された入力クロック信号に基づいて出力クロック信号の位相を調整して第2のバッファへ出力するエコークロック生成部7と、電圧判定信号と位相の調整量との関係を選択するモード情報を記憶する記憶部6と、を有し、エコークロック生成部7は、電圧判定信号とモード情報とに基づいて出力クロック信号の位相の調整量を決定する。

(もっと読む)

デジタルPLL回路、半導体集積回路装置

【課題】デジタルPLL回路の追従可能な周波数レンジを拡大する。

【解決手段】第1カウンタ(21)は、第1クロック信号をカウントして第1カウント値を出力し、第2カウンタ(22)は、第2クロック信号を分周して生成される第3クロック信号をカウントして第2カウント値を出力する。位相検出器(23)は、第1クロック信号と、第3クロック信号との位相差をデジタル値で示す出力値を出力する。位相誤差演算回路(26)は、第1カウント値と、第2カウンタ値と、出力値とに基づいて、位相誤差を演算して出力する。デジタルフィルタ回路(107)は、位相誤差を平滑化して発振周波数を示すコードを出力する。デジタル制御発振器(108)は、コードに応答して第2クロック信号を出力する。キャリブレーション制御回路(112)は、分周比と、第2クロック信号と第1クロック信号との比較結果とに基づいてデジタル制御発振器の発振周波数を調整する。

(もっと読む)

PLL回路

【課題】出力クロック信号の周波数制御を精度良く行うことが容易となるPLL回路を提供する。

【解決手段】流出または流入の出力電流を出力するものであって、パルス信号に応じて前記出力電流のオン/オフが切替えられるチャージポンプと、周期性を有する多値の参照信号に応じて前記パルス信号を生成する、パルス信号生成部と、を備え、前記出力電流に応じた出力クロック信号を生成するPLL回路であって、前記参照信号に応じて前記出力電流の電流量を調節する、電流量調節部を備えたPLL回路とする。

(もっと読む)

位相平均化に基づくクロック及びデータ回復の方法、回路及びシステム

【課題】入力データビットストリームとともに伝達される周波数ジッタ及びクロック信号発生器によって生成される周波ジッタを減衰させることができる、位相平均化に基づくクロック及びデータ回復の方法等を提供する。

【解決手段】一実施形態で、方法は、第1のクロック信号の第1の周波数を第1の周波数と基準クロック周波数の基準クロック周波数との間の周波数差に基づき調整するステップ(603)と、第1のクロック信号の第1の周波数及び第1の位相を第1のクロック信号と入力データビットストリームとの間の位相差及び第1の周波数と基準クロック周波数との間の周波数差に基づき更に調整して、第1のクロック信号の第1の周波数及び第1の位相を入力データビットストリームの入力データビット周波数及び入力データビット位相に略固定するステップ(606)とを有する。

(もっと読む)

PLL回路およびそのキャリブレーション方法

【課題】1回のキャリブレーションによって電圧制御発振器のフリーラン発振周波数がPLLロックレンジ内に入るようにして、キャリブレーション時間の大幅な時間短縮が可能となり、低消費電流化に貢献できるようにする。

【解決手段】PLLループをオープンにし、電圧制御発振器1に制御電圧Vcとして基準電圧Vaを入力したとき、基準信号f3のパルスによって帰還信号f2のパルス幅をカウントし、得られたカウント値に基づき、電圧制御発振器1の発振周波数f1を調整するキャリブレーションを実行するキャリブレーション回路10を設ける。

(もっと読む)

クロック発振回路

【課題】発振周波数のトリミングを行うクロック発振回路であって、CR発振回路の特性に起因する発振周波数のばらつきを低減することが可能なクロック発振回路を提供する。

【解決手段】クロック発振回路は、周波数調整コードに応じた発振周波数のクロック信号を生成する発振部101と、発振部101の発振周波数をカウントするOSCクロックカウンタ102と、外部接続された水晶発振器の発振周波数をカウントする基準クロックカウンタ103と、両発振周波数の比較を行う比較回路104とを備える。また、周波数調整コードの自動探索を行う探索回路105を備える。探索回路105は、周波数調整動作時において、発振部101に対する周波数調整コードの設定と、比較回路104による比較結果に応じた周波数調整コードの更新とを繰り返し行うことにより、周波数調整コードの自動探索を行う。

(もっと読む)

半導体装置

【課題】アナログ電圧を使用することなく、クロック信号を高精度且つ広範囲に遅延させる。

【解決手段】入力ノード110aと出力ノード110bとの間に直列接続された複数のワンショットパルス生成回路201〜20nを備える。ワンショットパルス生成回路201〜20nのそれぞれは、入力されたクロック信号の一方のエッジに応答して、ワンショットパルスを生成する。ワンショットパルスのパルス幅は、カウント値RCNTに基づいて可変である。これにより、カウント値RCNTを変化させることによって、ディレイライン110の遅延量を広範囲且つ高精度に変化させることが可能となる。しかも、アナログ電圧を使用しないことから、アナログ電圧の生成回路やその安定化回路などを設ける必要もなくなり、回路設計が容易となる。

(もっと読む)

半導体装置

【課題】サンプル間、温度等の変位に伴い発生するロック位相の変動を補正し、ロック位相を一定とすることができるDLLを備えた半導体装置を提供する。

【解決手段】位相検出回路(PD)105を構成する複数のMOSFETのうち所定のMOSFETのバックゲート電位を変更するPDバックゲート電位変更回路106と、温度センサ107と、サンプル別閾値電圧(Vt)情報を記憶したFuse(ヒューズ)108を備える。温度センサ107の温度情報、Fuse(ヒューズ)108に記憶されたサンプル別閾値電圧(Vt)情報は、PDバックゲート電位変更回路106に読み出され、閾値電圧を制御し、ロック位相の変動を補正する。

(もっと読む)

半導体装置

【課題】電流消費を削減する。

【解決手段】第1のクロック信号(ICLK)を受け、第1のクロック信号を可変である遅延量に応じて遅延させた第2のクロック信号(LCLK)を出力する遅延回路(31)と、第2のクロック信号を受け、遅延された第3のクロック信号(RCLK)を出力するレプリカ回路(32)と、第1および第3のクロック信号の位相差が所定時間以上であるか否かを検知し、所定時間以上である場合には遅延回路の遅延量を変化させ、所定時間未満である場合には遅延回路の遅延量を変化させないように制御する位相差検出回路(36)と、を備える。

(もっと読む)

PLL回路及びその制御方法

【課題】回路規模の増大を抑制しつつ、VCOの発振周波数を広い範囲で変化させることができるPLL回路及びその制御方法を提供すること。

【解決手段】本発明にかかるPLL回路1は、VCO11と、制御ロジック14と、位相比較器13と、を備える。VCO11は、両端の電位差に応じて容量値が変化する可変容量素子を有し、電位差に応じた発振周波数の出力信号を出力する。制御ロジック14は、可変容量素子の一端に所定の電圧を印加した状態で、基準信号と出力信号との周波数差に基づいて、当該可変容量素子の他端に印加する制御電圧Vtcを決定する。位相比較器13は、可変容量素子の他端の電圧を制御ロジック14により決定された制御電圧Vtcに固定した状態で、基準信号と出力信号との位相差に基づいて、可変容量素子の一端に印加する制御電圧Vtaを決定する。

(もっと読む)

半導体装置及びその制御方法

【課題】クロック信号にジッタ成分が重畳している場合であってもDLL回路を正しくロックさせる。

【解決手段】カウンタ部102のカウント値に応じてクロック信号LCLKを生成するディレイライン101と、クロック信号LCLKを反転させるか否かを制御する反転制御部103とを備える。カウンタ部102のカウント値を第1の初期値にリセットした後、反転制御部103はクロック信号LCLKを反転させ又は反転させることなく出力する。次に、カウンタ部102のカウント値を第2の初期値にリセットする。本発明によれば、ジッタなどの影響によってクロック信号LCLKを誤って反転させ、或いは誤って反転させなかった場合であっても、ダウンカウント(またはアップカウント)が多数回連続することがなくなる。これにより、第1及び第2の初期値としてオフセットした値を用いることが可能となる。

(もっと読む)

半導体装置

【課題】出力クロック信号を生成して出力するまでに要する時間を短縮させる。

【解決手段】半導体装置は、第1のクロック信号のライズエッジ及び第2のクロック信号のライズエッジを合成して第1及び第2のクロック信号のライズエッジの間にライズエッジを有する第3のクロック信号を生成する第1の位相合成回路と、第1のクロック信号のフォールエッジ及び第2のクロック信号のフォールエッジを合成して第1及び第2のクロック信号のフォールエッジの間にフォールエッジを有する第4のクロック信号を生成する第2の位相合成回路と、第3のクロック信号のライズエッジを受けてライズ/フォールエッジの内の一方の位相を、第4のクロック信号のフォールエッジを受けてライズ/フォールエッジの内の他方の位相を其々調整した出力クロック信号を出力する第3の位相合成回路と、を備える。

(もっと読む)

クロック再生回路

【課題】ジッタが小さく、面積が小さなクロック再生回路を提供する。

【解決手段】このクロック再生回路は、各UGにおける外部データ信号列Dinの最初の立ち上がりエッジに応答して論理レベルが反転される信号PD_Dinと、内部クロック信号VCOCLKに同期したクロック信号PD_Cinとを生成するエッジ抽出回路1と、信号PD_Dinとクロック信号PD_Cinの位相を比較し、比較結果を示す信号UP,DNを出力する位相比較器6とを備える。したがって、各UGで1回だけ位相比較を行なうので、データパターンに依存するジッタを抑制できる。

(もっと読む)

クロック生成回路、クロック生成方法および半導体集積回路

【課題】占有面積や定常位相誤差の増大、並びに、クロックが安定するまでに長時間を要することなく、スペクトラム拡散クロックを生成してEMI対策を図る。

【解決手段】基準信号CK1を受け取って、立ち上がりエッジの傾き、または、立ち下がりエッジの傾き、または、立ち上がりエッジおよび立ち下がりエッジの傾きを、周期的に変化させた第1信号CK2を生成する第1回路4と、前記第1信号を受け取って、周期的に周波数が変化するクロックを生成する第2回路5と、を有する。

(もっと読む)

半導体装置

【課題】DLL回路がロックしないという現象の発生を防止する。

【解決手段】カウンタ回路202と、カウンタ回路202のカウント値CNTに応じた遅延量を内部クロック信号LCLKに与えるディレイライン201とを有する。まず、カウンタ回路202は第1のカウント値にセットされ、判定信号PDに基づいてそのカウント値CNTが周期的に更新される。その結果、内部クロック信号LCLKの位相が所望の位相に到達しなかった場合、カウンタ回路202は、第1のカウント値とは異なる第2のカウント値にセットされ、DLL回路200がリスタートされる。これにより、DLL回路がロックしなかった場合であっても自動的にリスタートされることから、DLL回路がロックしないという現象が防止される。

(もっと読む)

同期信号処理装置

【課題】回路の小面積化、低消費電力化を図ることが可能であり、しかも温度依存性の影響を受けない安定した位相比較が可能な同期信号処理装置を提供する。

【解決手段】水平同期信号を同期クロックで同期させ、当該同期クロックのタイミングでデジタルデータとして出力する時間デジタル変換器(TDC)と、同期クロックをカウントして参照クロックを生成する参照クロック生成部と、TDCによるデジタルデータと参照クロックの位相比較を行うことにより位相差情報を得るデジタル位相比較器と、デジタル位相比較器の位相差情報に応じて上記参照クロックとTDCによる水平同期信号のデジタルデータの位相が一致するように周波数が制御される同期クロックを生成する同期クロック生成装置と、を有する。

(もっと読む)

シリアル・データ通信装置のDPLL回路

【課題】PLCで設計・構成するシリアル・データ通信の高速化を図ることができ、しかも受信データのジッタ許容範囲を明確にできる。

【解決手段】DPLL回路10のうち、データシフト回路DS1〜DS3は受信データからソースクロックCLKで同期を取った複数のシリアル・データを生成する。排他的論理和回路EX_ORは一対のシリアル・データから受信データの変化点を検出する。カウンタDPLCNTは、最大カウント値nが設定され、変化点から次の変化点までをソースクロックをカウントする。一致判定回路ANDはカウンタのカウント値が予め設定したカウント値n/2に一致したときに受信クロックとして出力する。ハイレベル・データ・リンク・コントローラ・モジュール(HDLC−IP)20は、受信クロックを使って受信データ(シリアル・データ)の転送制御を行う。

(もっと読む)

1 - 20 / 351

[ Back to top ]