Fターム[5J106DD18]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | 計数(カウンタ)回路 (442) | 可変カウンタ (28)

Fターム[5J106DD18]に分類される特許

1 - 20 / 28

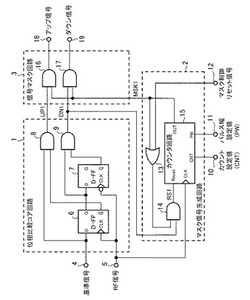

位相比較回路

【課題】入力信号の周波数比が整数でない場合にも、±180度の範囲で位相差検出ができる位相比較回路を得る。

【解決手段】RF信号と基準信号との立ち上がりエッジを比較してアップ信号またはダウン信号を生成する位相比較コア回路1と、RF信号と基準信号との周波数比をN+K/M(但し、N,K,Mは任意の自然数)とし、RF信号の周波数をfrfとしたとき、アップ信号の立ち上がりの直前のRF信号の立ち上がりに同期して立ち上がり、パルス幅は基準信号の1周期分とほぼ等しく、周期は(M×N+K)/frfとなるマスク制御信号MSK1を生成するマスク信号生成回路2と、位相比較コア回路1により生成されたアップ信号およびダウン信号を、マスク信号生成回路2により生成されたマスク制御信号MSK1に従いマスクする信号マスク回路3とを備えた。

(もっと読む)

PWM信号生成装置

【課題】PWM信号生成装置において、回路規模を小さくして効果的に放射雑音等のノイズを低減する。

【解決手段】CPU204、カウンタ201、レジスタ202、及びコンパレータ205は基準クロックの周波数をその一周期未満の時間で変動させた変動クロックを生成する。TFF206は基準クロックに応じて変動クロックを第1のPWM信号として出力する。TFF251は基準クロックを所定の時間遅延させた遅延クロックに応じて変動クロックを第2のPWM信号として出力する。セレクタ252は第1及び第2のPWM信号を選択的にPWM信号として出力する。

(もっと読む)

クロック生成回路及びこれを備える半導体装置、並びに、クロック信号の生成方法

【課題】クロック信号の周波数に依存しないデューティ調整回路が搭載されたDLL回路を提供する。

【解決手段】内部クロック信号ICLKを遅延させることによって内部クロック信号LCLKを生成するディレイライン110と、ディレイライン110の遅延量を指定するカウンタ回路123と、カウンタ回路123のカウント値を調整するカウンタ制御回路122と、内部クロック信号ICLKとレプリカクロック信号RepCLKのライズエッジが一致する第1及び第2のカウント値との差分を演算する減算回路133とを備え、得られた差分の1/2に相当する値に基づいて、内部クロック信号LCLKのフォールエッジを調整する。これにより、キャパシタを交互にディスチャージするタイプのデューティ調整回路を用いた場合のように、適用可能な周波数帯域が限られることがない。

(もっと読む)

双方向無線通信システム、無線通信装置及び双方向無線通信方法

【課題】PLL回路を含んだ回路に比べて周波数同期回路等を簡単な回路によって構成できるようにする。

【解決手段】入力信号を変調した変調信号に所定の搬送周波数の基準搬送信号を重畳して送信信号を送信する双方向用のTRX1と、通信許可信号を生成するTRX2とを備える。TRX2は自走発振周波数の信号を発振する発振器を有している。TRX2は、TRX1から受信した受信信号を発振器23に注入する。これと共に、発振器23の自走発振周波数を可変制御しながら受信信号を受信し、発振器23の信号の自走発振周波数が注入同期に至る周波数範囲に入って注入した受信信号の搬送周波数に周波数同期したか否かを検出する。TRX2は、発振器23の信号の自走発振周波数が、注入した受信信号の搬送周波数に周波数同期したことを検出したときに、通信許可信号をTRX1に送信するものである。

(もっと読む)

位相補償用クロック同期回路

【課題】短時間で精度よく位相調整を行うことが可能な位相補償用クロック同期回路を提供する。

【解決手段】DLLは、入力レシーバ1と、遅延チェーン回路2と、遅延複製器4と、位相比較器5と、リセットパルス発生器6と、粗調整期間発生器7と、分周器8と、単位可変カウンタ9と、を備えている。まず単位可変カウンタ9の増減単位を17または1(平均で16)として粗調整を行って粗くロックさせた後に、単位可変カウンタ9の増減単位を1として微調整を行って細かくロックさせるため、短い期間で確実にクロックINTCKXとクロックEXTCKXの位相を合わせることができる。

(もっと読む)

シンセサイザと、これを用いた受信装置及び電子機器

【課題】シンセサイザにおけるデジタル的な周波数制御に起因した位相雑音性能の悪化。

【解決手段】本発明のシンセサイザは、基準発振器から出力された基準発振信号が入力される比較器と、比較器の出力側に接続されたフィルタと、フィルタの出力側に接続されて発振信号を出力する発振器と、発振器の出力信号を制御部からの制御信号に基づいて分周する分周器とを備え、比較器は、分周器からの出力信号と基準発振器からの出力信号とを比較してこの比較結果を示す信号をフィルタに出力すると共に、制御部は、温度を検出する検出器の検出結果に基づいて分周器の分周比を時間間隔Tで制御し、時間間隔Tとフィルタのカットオフ周波数fcとの関係は、1/T≧fcを満たす構成である。

(もっと読む)

周波数合成器および周波数合成装置

【課題】基準信号の周波数の実数倍の周波数を持ちジッタの少ないデジタル信号を整数PLLとデジタル回路のみを用いて生成する。

【解決手段】実数である周期指定値をデルタ・シグマ変調器を通してジッタの低周波成分を抑制した整数分周数列を発生させ、その分周数列で基準信号を分周する。その分周出力信号に対して整数PLLによりジッタを除去することにより所望の信号を得る。また、前記デルタ・シグマ変調器では、分周器出力において理想的な信号の立ち上がりのタイミングと実際の立ち上がりのタイミングの誤差を算出し、その誤差に対してデジタルフィルタを通して分周数にフィードバック補償を行う。

(もっと読む)

ディジタル位相同期ループ(DPLL)の時間対ディジタル変換器(TDC)のパワーオンゲーティング窓を較正するためのシステム及び方法

ディジタル位相同期ループ(DPLL)の時間対ディジタル変換器(TDC)のパワーオンゲーティング窓を較正するのに関係するシステム及び方法が開示される。ゲーティング窓は同時に電力の効率的方法でTDCを動作させながらDPLLの適切な動作を保証するために較正される。特に、その技術はTDCゲーティング窓の幅を既定値に設定すること;制御ループが実質的にロックされるまで、DPLLを動作させること;DPLLの位相誤差デバイスによって生成される位相誤差信号をモニターしながら、TDCゲーティング窓の幅を所定の量だけ減少させること;位相誤差が所定の閾値に実質的に到達するか、或いは横切るときにTDCゲーティング窓の現在の幅を決定すること;及びTDCゲーティング窓の動作幅の誤差のマージンに組込む所定の量だけTDCゲーティング窓の現在の幅を増加させることを要する。  (もっと読む)

(もっと読む)

局所発振回路

【課題】消費電力を低減できる局所発振回路を提供する。

【解決手段】周波数fsの基準振動信号と周波数fout/(m×n)の分周信号の位相を比較する位相比較器1と、上記両信号の位相のずれに応じた電流IOUTを出力する電荷ポンプ10と、上記出力電流IOUTに応じた制御電圧VCを生成するループフィルタ3と、上記制御電圧VCに応じた発振周波数foutの信号を出力する電圧制御発振器4と、電圧制御発振器4の出力信号を設定周波数に応じた分周値(m×n)で分周して上記分周信号を出力する前置分周器5および可変カウンタ6とを備え、上記発振周波数foutを上記設定周波数に引き込む局所発振回路において、上記電荷ポンプ10は、出力電流IOUTの値を上記設定周波数に応じて切り換える。

(もっと読む)

DLL回路及びこれを用いた半導体記憶装置、並びに、データ処理システム

【課題】FDLを調整するカウント信号のビット数を増加させても、高速に遅延量を確定させることが可能なDLL回路を提供する。

【解決手段】相対的に粗い調整ピッチでクロック信号を遅延させるディレイライン(CDL)10と、相対的に細かい調整ピッチでクロック信号を遅延させるディレイライン(FDL)20と、ディレイライン10,20の遅延量を制御する位相検知回路41,42及びカウンタ制御回路51,52とを備える。カウンタ制御回路51,52は、線形探索法によってディレイライン10を制御するとともに、二分探索法によってディレイライン20を制御する。これにより、ディレイライン20を調整するカウント信号のビット数を増加させても、高速に遅延量を確定させることが可能となる。

(もっと読む)

PLL回路

【課題】複数の分周回路を備えるPLL回路に関し、PLL回路の新たな回路構成を提案する。

【解決手段】基準クロックの位相と位相比較クロックの位相とを比較し、位相差に応じた信号を出力する位相比較回路と、前記位相比較回路により出力された前記信号をフィルタリングするループフィルタと、前記ループフィルタによりフィルタリングされた前記信号に応じた周波数のクロックを出力する電圧制御発振回路と、前記クロックを分周して前記位相比較クロックを生成する第1の分周回路と、前記クロックを分周して出力クロックを生成する第2の分周回路と、前記第1の分周回路の分周数と前記第2の分周回路の分周数とを制御する分周制御回路とを備えることを特徴とするPLL回路。

(もっと読む)

クロックアンドデータリカバリ回路

【課題】クロックアンドデータリカバリ回路において、周波数追従ループのジッタ耐性を向上させる。

【解決手段】位相検出器210は、同期クロック信号とシリアルデータの位相を比較して比較結果に応じた位相誤差信号を出力する。積分器230は、位相誤差信号を積分してシリアルデータの位相変動に追従するための位相補正制御信号を得る。積分器240は、所定の長さの平滑期間毎に位相誤差信号を積分して平滑誤差信号を得る。パターン発生器250は、所定の長さのパターン発生期間毎に、平滑誤差信号に応じた頻度で同期クロック信号の位相を変更するパターンを発生して周波数補正制御信号として出力する。積分器240は、周波数補正制御信号がフィードバックされ、該周波数補正制御信号における頻度の変動方向に応じて、平滑化期間の長さを変更する。

(もっと読む)

クロックアンドデータリカバリ回路

【課題】クロックアンドデータリカバリ回路において、周波数追従ループのジッタ耐性を安定させる。

【解決手段】位相検出器210は、位相補間器270からの同期クロックとシリアルデータの位相を比較して比較結果に応じた位相誤差信号を出力する。第1の積分器230は、位相誤差信号を積分してシリアルデータの位相変動に追従するための位相補正制御信号を得る。第2の積分器240は、位相補正制御信号をさらに積分してアップ/ダウン信号を得る。パターン発生器250は、アップ/ダウン信号からシリアルデータの周波数変動に追従するための周波数補正制御信号を生成する。パターン発生器250のパターン長と第2の積分器240のカウント幅の積は、第1の積分器230のカウント幅が大きいほど大きくなる大きさの閾値以上である。

(もっと読む)

時間デジタル変換装置およびデジタル位相同期ループ装置、受信機

【課題】広帯域の周波数範囲に対応可能で、量子化ノイズ成分を増大させることなく低消費電力化を図る。

【解決手段】時間デジタル変換器104は、発振周波数を制御する周波数制御信号16を用いて、入力周波数に応じて動作する遅延回路10−1〜10−nの段数を切り替えるスイッチング素子12−1〜12−nを備えている。入力周波数の周期に応じて必要な段数の遅延回路だけが動作することとなるため、広帯域の周波数範囲に対応しながらも系全体の低消費電力化を図ることが可能となり、特に高い入力周波数において低消費電力化を図ることができる。

(もっと読む)

周波数シンセサイザ

【課題】複数の発振周波数帯域から1つの周波数帯域を選択可能な集積化されたVCOを構成する素子に製造ばらつきがあっても、最適な周波数帯域で所望の周波数に位相ロックすることができ、しかもVCOの消費電流を低減できる周波数シンセサイザを提供する。

【解決手段】分周比格納部9aの分周比が更新されたらPLLを開ループ状態にして可変分周器2、3の出力信号と基準分周器5の出力信号の位相を比較し、その結果に応じて、電圧制御発振器1bの共振回路の共振周波数を変化させながら、所望の周波数の周波数帯域を選択し決定する。その後、可変分周器の出力信号と基準分周器5の出力信号の位相を比較し、その結果に応じて、電圧制御発振器1bの電流を変化させながら、最適電流値を決定する。その後、位相同期系を閉ループ状態にして位相ロックさせる。

(もっと読む)

クロック生成回路

【課題】逓倍回路から正確な逓倍クロックが出力されず、温度等の変動に対する補正能力が低下し、ロックが困難になるという課題があった。

【解決手段】互いに直列に接続された複数個の遅延素子から構成されるデジタルディレイライン56,69,71を有し、デジタルディレイライン56,69,71に対応したカウンタ52,65から出力されるカウント値に応じて複数の遅延素子のいずれかの遅延を選択し、選択した遅延素子およびこれに隣接する1つの遅延素子によって遅延時間を設定制御する。

(もっと読む)

PLL回路

【課題】 複数種類の異なった記録モードで記録するための記録信号が入力され、入力信号に含まれる雑音成分を取り除いた純度の高い信号を出力するPLL回路を実現する。

【解決手段】 入力信号を1/Lにして第1分周器41から第1周波数信号を出力し、入力信号に対応するマスタクロック信号を発振器46aで発振し、マスタクロック信号の周波数を1/Mにして第2周波数信号を第2分周器52から出力し、第1周波数信号と第2周波数信号との位相差信号を位相比較器43から出力し、第1周波数信号と第2周波数信号とが一致しているか否かをロック検出器44で検出し、一致しない場合には第1分周器のL及び第2分周器のMを可変させ、一致した場合にはL及びMを固定させる制御信号を制御回路48から出力し、マスタクロック信号を1/Nにして真の信号成分を第3分周器から出力するようにしたPLL回路を構成した。

(もっと読む)

自動周波数制御ループ回路

【課題】高い精密度を有しながら周波数を広帯域で発振させることができる自動周波数制御ループ回路を提供すること。

【解決手段】基準周波数を発生させるクロック発振部と、基準周波数を第1分周比で分周する第1分周器、発振周波数を第2分周比で分周する第2分周器、第1分周器によって分周された第1分周周波数と第2分周器によって分周された第2分周周波数との間の位相差を検出する位相検出器、位相差に対応して発振周波数を発生させる電圧制御発振器と、入力周波数と発振周波数に対応して出力周波数を出力する周波数変換器を含む周波数合成部と、出力周波数を設定周波数と比較して誤差を検出する誤差検出器、誤差を積分する積分器と、積分器の積分値に対応する制御信号を計算する演算器を含む復調部とを含み、制御信号に応じて第1分周比及び第2分周比を変更して誤差を補正することを特徴とする。

(もっと読む)

通信装置

【課題】 ロックアップタイムの短縮と、受信品質の向上と、を両立すること。

【解決手段】 PLL回路10を用いて受信信号の周波数変換を行う通信装置1において、PLL回路10の次数を変更する次数変更手段と、周波数変換後の受信信号の品質を示す品質情報を取得する品質情報取得手段と、を含み、前記次数変更手段は、前記品質情報により示される品質が所定条件を満たすように、前記次数を変更する、ことを特徴とする。

(もっと読む)

通信用半導体集積回路

【課題】所定の周波数の局部発振信号を発生する発振器を含むPLL回路を内蔵し、温度が変化してVCOの発振周波数が変動してもPLLループのロックがはずれにくい高周波ICを提供する。

【解決手段】発振周波数帯を切り替え可能なVCO11と可変分周回路12と位相比較回路15とループフィルタ17とを含み、ループフィルタとVCOとの間を切り離した開ループ状態で、複数の所定の固定電圧のいずれかをVCOへ印加する切替えスイッチと、所定の周波数の基準信号に対する可変分周回路の出力の位相の進みまたは遅れを判別する判別回路22と、判別回路の出力に基づいてVCOの周波数帯を切り替える信号を生成する自動バンド切り替え回路23とを設け、2分探査方式でVCOの周波数帯を切り替えながら最適な周波数帯を見つけ、さらにVCOへ印加する固定電圧を2分探査方式で切り替え最適な印加電圧を見つけPLLループをロックさせる。

(もっと読む)

1 - 20 / 28

[ Back to top ]