Fターム[5J106DD21]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | 同期化クロック制御回路 (365)

Fターム[5J106DD21]の下位に属するFターム

パルス挿入・抜き取り制御 (9)

分周比・カウンタ値制御 (46)

移相・遅延量制御 (201)

クロック周波数選択制御 (13)

クロック位相選択制御 (34)

複数の同期化クロック制御回路 (29)

Fターム[5J106DD21]に分類される特許

1 - 20 / 33

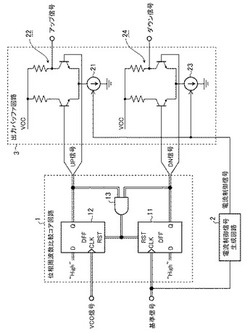

位相周波数比較回路

【課題】雑音特性及び高速動作を維持しながら、消費電力を削減することができる位相周波数比較回路を得ることを目的とする。

【解決手段】出力バッファ回路3が、電流制御信号生成回路2から電流制御信号が出力されている期間中、位相周波数比較コア回路1からUP信号が出力された場合、アップ信号を出力し、電流制御信号生成回路2から電流制御信号が出力されている期間中、位相周波数比較コア回路1からDN信号が出力された場合、ダウン信号を出力する。

(もっと読む)

時刻同期装置およびその時刻同期補正方法

【課題】GPS衛星電波が受信出来ない時も正確に同期タイミング信号を出力する時刻同期装置およびその時刻同期補正方法を提供する。

【解決手段】内蔵発振器1は、GPS受信器Rからの1pps信号と出力するクロックと間の位相差信号を発振制御部3へ出力し、この位相差を無くす発振周波数制御信号が発振制御部3内蔵発振器1へ出力される。1pps信号が断となった場合、発振制御部3は、ログ部LGのドリフト記録部5と信号断時間記録部6から、予め測定記録していた単位時間あたりの内蔵発振器1の周波数のドリフト量からドリフトを補正する発振周波数制御信号を生成して内蔵発振器1へ出力し、タイミング信号発生部2は、内蔵発振器1からのクロックにより生成した同期タイミング信号を外部へ出力する。

(もっと読む)

多相発振器を有する位相ロックループ

位相ロックループが複数のデジタル入力を有する多相発振器を利用する。時間に関して互いにオフセットされた複数のDQフリップフロップが、複数の制御信号を生成して、発振器から制御位相情報をデジタル形式で取り出す。発振器における任意の2つのデジタル入力間に接続されたDQフリップフロップが、進行波の方向を判定する。その方向と位相情報とにより、ルックアップテーブルがアドレス指定され、発振器の現時点のフラクショナル位相が判定される。発振器周波数を低減するために、N分周回路が用いられる。発振器に関する全位相表示信号が、現時点のフラクショナル位相を用いて判定される。この全位相を基準位相と比較して、発振器に対する修正を行うための制御信号を生成する。フィードフォワード経路において、分周器が、発振器からの高周波信号をより低い所望の周波数に分割し、それにより位相分解能を向上させる。 (もっと読む)

同期化システム用結晶ベース発振器

【課題】クロックの不具合の可能性を排除し、冗長性及び拡張性を備える同期化システムを提供するためのSXOモジュールを提供する。

【解決手段】第1のバスから調整済み信号を受信し、共振器信号をステージ維持増幅器に渡す結晶共振器を含む結晶発振器ベースのモジュール。同期化範囲拡大回路が利得制御ネットワークと共振器の間に接続される。トライステートバッファがバッファを介して共振器信号を受信するように接続された主入力を有する。トライステートバッファの出力は、必要に応じて整合ネットワークを介して、第2のバスに接続される。上記モジュールを交互に2つのバスに接続することによって同期クロックシステムが形成されうる。また、トライステートバッファは制御入力も有しており、制御入力はホットスワッピングおよび他の便益を可能にするようにVccとグラウンドの間の遅延回路に接続されてもよい。

(もっと読む)

原子発振器

【課題】周波数基準を実現させると共に、光源駆動制御回路系を簡略化して装置を小型化

し、且つ安価な光源を利用することでコストを低減することができる原子発振器を提供す

る。

【解決手段】この原子発振器50は、アルカリ金属の一種であるCs原子の異なる遷移エ

ネルギーに対応する二種類の周波数の励起光対を発生させる光源1と、少なくとも気体状

のCs原子を封入したCsセル2と、光検出器3と、光検出器3により検出した光強度の

変化に応じてその出力値(電圧等)を制御する周波数制御手段4と、周波数制御手段4の

出力値によりその出力周波数を制御可能な基準発振源5と、基準発振源5の出力周波数を

光源1が発生する二種類の励起光対の周波数差の周波数に逓倍する逓倍手段6と、逓倍手

段6で発生した周波数差の二種類の励起光対を光源1から発生させる光源駆動電流の変調

手段7と、を備えて構成されている。

(もっと読む)

クロックリカバリ回路、及びそれを備えるクロックデータリカバリ回路

【課題】動作信頼性を向上させるクロックリカバリ回路、及びそれを備えるクロックデータリカバリ回路を提供すること。

【解決手段】受信信号を再生するタイミング情報が重畳された前記受信信号とリカバリクロックとの位相差に基づいて、前記受信信号とリファレンスクロックとの周波数オフセット情報を検知する周波数差検知部34と、前記周波数検知部34が検知した前記周波数オフセット情報に基づいて、前記受信信号と前記リカバリクロックとの位相差を補正する補正部30とを具備する。

(もっと読む)

デジタルPLL回路及びデジタルPLL動作方法

【課題】CLVスピンドル制御のランダムシーク時でもスループット低下を抑え、かつ安価で消費電力を抑えたワイドキャプチャ対応のデジタルPLL回路を提供する。

【解決手段】本発明のデジタルPLL回路10Aは、周波数値fq’に応じてマスタクロックsclkの周波数を切り替えるマスタクロック切り替え手段10Bと、周波数値fq’に一定の倍率を乗じて数値制御発振器6へ出力するとともに、マスタクロックsclkの周波数が切り替わる前後で同期クロックgclkの周波数が一定になるように前記倍率を切り替える倍率切り替え手段10Cと、を備えたことを特徴とする。

(もっと読む)

デューティ検出回路およびCDR回路

【課題】入力データが交播パターン以外の場合であっても、高速かつ高精度にデューティを検出する。

【解決手段】デューティ検出回路は、入力データDinとこの入力データDinに周波数および位相が同期したクロックCKとを入力とし、入力データDinをクロックCKに同期してラッチして基準パルス幅を示すパルス信号Refを出力するフリップフロップ1と、入力データDinの平均電圧レベルとパルス信号Refの平均電圧レベルとの差を、入力データDinのデューティ100%からの変動分を示す検出信号Outとして出力する出力回路2とを備える。

(もっと読む)

PLL回路、無線端末装置、および周波数検出方法

【課題】DCOの最低発振周波数を検出し、分周比Nに比例した制御データから、DCOの制御データへの変換を精度良く行うことが可能な、新規かつ改良されたPLL回路を提供すること。

【解決手段】ディジタル値を用いて制御される発振回路を有するPLL回路であって、搬送波周波数値を設定する搬送波周波数設定部と、搬送波周波数値が変化したことを検出する検出部と、搬送波周波数値が変化したことを示す信号に同期して、発振回路を最低周波数で発振させるための制御信号を送信し、基準周波数の1周期内の発振回路の出力クロック数を計測する計測部と、を含むことを特徴とする、PLL回路が提供される。

(もっと読む)

半導体装置

【課題】 シリアルデータの高速化にともなう受信性能の低下および連続同符合データ受信によるクロックデータリカバリー回路の精度低下を防止し、尚且つ消費電力の低いクロックデータリカバリー回路を提供する。

【解決手段】 シリアルデータを受信するSerDes回路101と、並走クロック信号を受信する参照SerDes回路102とを有し、SerDes回路101は、参照SerDes回路102の生成した位相制御信号P_CSを用いて位相制御された再生クロックにより受信したシリアルデータの直列並列変換を行う。

(もっと読む)

データ駆動回路及び遅延固定ループ

【課題】アナログデータ信号のディスプレイパネルへの印加時に発生する誤りなどにも関わらず、正常に動作可能なデータ駆動回路及び遅延固定ループの提供。

【解決手段】第1のクロック信号の入力を受けて第2のクロック信号を出力する遅延固定ループにおいて、前記第1のクロック信号、前記第2のクロック信号及び少なくとも一つの遅延信号によって位相差信号-前記第1のクロック信号又は前記第2のクロック信号によって前記第1のクロック信号と前記第2のクロック信号の間の位相差に該当する値を有し、前記少なくとも一つの遅延信号によって位相差無しに該当する値を有する-を出力する位相検出器21と、前記第1のクロック信号を遅延させることにより前記第2のクロック信号及び前記少なくとも一つの遅延信号を求める遅延線23-前記第1のクロック信号に対する前記第2のクロック信号の遅延は前記位相差信号により変更される-と、を備える。

(もっと読む)

信号再生装置

【課題】受信したDVB−ASI信号からジッタなどによる位相変動を抑制したクロックを再生可能とする。

【解決手段】パラレル変換されたDVB−ASI信号の各TSパケットの47hコードが、47コード検出器4により、検出された47hコードパルスEが得られ、適応型位相代替回路5を介してPLL回路の位相比較器13に供給され、分周器8からの位相基準クロックF1と位相比較される。ジッタなどによって47hコードパルスEの位相が大きく急変し、位相基準クロックF1との位相差が異常に大きい場合には、適応型位相代替回路5は、かかる47hコードパルスEに代わる代替パルスを位相比較器13に供給する。これにより、VCO15の制御電圧の急変を抑えることができ、安定した基準クロックFが得られる。

(もっと読む)

クロックデータ再生回路

【課題】高速シリアルデータ転送の受信回路において、低消費電力モードから通常モードに復帰する際の復帰時間を短縮する。

【解決手段】シリアルデータ転送路から転送される同期用クロックを含むシリアルデータから同期用クロック及びデータを再生するクロックデータ再生回路であって、シリアルデータ及び基準クロックを電力モードに応じて選択してクロックデータ再生回路に供給する選択回路を具備する。

(もっと読む)

記録装置及び記録装置の制御方法

【課題】ディスクの回転に安定して同期した記録クロックを生成できるようにする。

【解決手段】ディスク状記録媒体に形成されているウォブルを読み取ってウォブル信号を検出し、前記ウォブル信号に基いて記録用のクロック信号を生成する記録装置であって、前記ディスク状記録媒体のウォブル周期に関連した周波数を有するクロックを生成する第1のクロック生成手段と、前記ディスク状記録媒体にデータを記録するためのチャネル周期に関連した周波数を有するクロックを生成する第2のクロック生成手段とを備え、前記第1のクロック生成手段に組み込まれているDVCO部と同一のDVCO部を組み込んで前記第2のクロック生成手段を構成する。

(もっと読む)

情報再生装置

【課題】PLLループディレイを増加させることなく、CAV再生時にも安定的に情報を検出できる情報再生装置を提供する。

【解決手段】A/D変換器101は、固定周波数のシステムクロックsclkで読出し信号をサンプリングし、A/D変換を行う。変動補償器102は、内部帰還形の補償フィルタとして構成され、A/D変換器101が出力するデジタル信号の変動を抑圧する。デジタルPLL103は、補間器131により、チャネル周波数に同期したタイミングにおける読出し信号のサンプリング値を補間生成し、NCO134により、同期クロックと補間器131に帰還する補間位相信号とを生成する。2値化回路104は、補間器131が出力する補間値に基づいて読出し信号を2値化する。変動補償器102の周波数特性は、ループフィルタ133が出力する周波数値に基づいて制御される。

(もっと読む)

システムクロック供給装置及び基準発振器の周波数ずれ判定方法

【課題】システムクロック供給装置及び基準発振器の周波数ずれ判定方法に関し、装置内の基準発振器自身の周波数ずれを、測定用の発振器を用いずに判定し、周波数異常箇所を特定し、異常周波数クロックの送出を防ぐ。

【解決手段】二重化構成(N系及びE系)のシステムクロック供給装置内にそれぞれ備えられたOCXO等の基準発振器(#N,#E)9−1の出力クロックと、システム同期用に通常入力されるリファレンスクロック(例えば8KHz)とを、周波数ずれ測定部(#N,#E)1−1でそれぞれ比較し、所定回数の周波数ずれの発生を誤検出保護回路(#N,#E)1−2で測定し、該両系の測定結果を基に異常個所判定部(#N,#E)1−3で、自系若しくは他系の基準発振器(#N,#E)9−1の出力クロックの周波数ずれ又はリファレンスクロックの異常を判定して異常箇所を特定し、異常箇所を他系に切り替えるよう選択信号を送出する。

(もっと読む)

位相誤差検出回路、位相同期ループ回路および情報再生装置

【課題】 位相誤差検出回路において、読み出し信号の振幅レベルが変動しても位相誤差を精度良く検出し、よって位相同期ループ回路の位相同期特性を安定させること。

【解決手段】 位相誤差検出回路7は、入力信号の連続する2つのサンプリング位置n,(n−1)における信号レベルXn、Xn−1について、それらの和Anと差Bnの比Cn(=An/2/Bn)を演算する演算器を備える。そして、信号レベルXn、Xn−1の極性が変化するサンプリング位置における演算結果Cnを位相誤差信号Tnとして出力する。さらに、演算したAnの値を、入力信号のDC誤差信号Snとして出力する。

(もっと読む)

クロック切替回路

【課題】位相が異なるクロックを非同期の切替信号に基づき切り替えても出力クロックに、切り替え時の短パルスが発生しないクロック切替回路を提供すること。

【解決手段】クロック切替回路1は、外部クロックCLKT、CLKBが入力されそれぞれPLL回路2、3と、PLL回路3の出力PLBかPLL回路2の出力PLTの反転信号を選択出力するマルチプレクサ14と、CLKB、PLBとは非同期のLock判定信号12aに基づきマルチプレクサ14を切り替え制御するクロック制御回路13とを有する。クロック制御回路13は、Lock判定信号12aが入力されるとPLBの位相を所定値オフセットさせたオフセットクロックPLQBに同期してマルチプレクサ14の出力を切り替えさせる。

(もっと読む)

チャージポンプ回路及びこれを用いたPLL回路

【課題】PLL回路の応答特性を調整可能にし、更に、リファレンスリーク(キャリアリーク)を低減する。

【解決手段】位相比較器50内にパルス幅変更部70を設け、外部からセレクト信号SL1,SL2によりセレクタ73,76を切り替えることにより、アップ信号UP又はダウン信号DNのパルス幅を変更させ、チャージポンプ回路80の充電時間を調整することにより、PLL回路の反応特性を高める(不感帯を減少させる)。チャージポンプ回路80内にセレクト部90を設け、外部からセレクト信号SL1,SL2によりスイッチ91〜94を切り替えることにより、チャージ電流Icpによる出力電圧Vcpの持ち上がりによって起きるリファレンスリーク(キャリアリーク)を抑制し、これによってノイズ量を低減する。

(もっと読む)

デジタル放送受信装置およびデジタル放送システム

【課題】本発明は、可変周波数の水晶発器(VCXO)を用いること無く、基地局と受信装置間の時間情報および基準クロックの同期を実現することができる、デジタル放送受信装置等を提供する。

【解決手段】水晶発振子22は、所定の固定周波数のクロックを発振する。可変デジタル分周回路24は、固定周波数を分周比によりデジタル分周し、分周比を変更することができる。システムでコーダ5は、基地局からの基準時間情報を検出する。基準カウンタ18は、受信装置20の時間情報を生成する。位相比較器13は、基準時間情報と時間情報との差分を検出する。分周比制御回路25は、前記差分に基づいて前記分周比の変更を制御する。また、基準カウンタ18は、可変デジタル分周回路24により分周された周波数を有するクロックに基づいて時間情報の生成を行い、時間情報を位相比較器13にフィードバックさせている。

(もっと読む)

1 - 20 / 33

[ Back to top ]