Fターム[5J106DD44]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | デジタル回路 (2,545) | 演算回路 (156)

Fターム[5J106DD44]に分類される特許

101 - 120 / 156

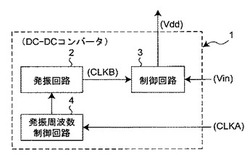

発振周波数制御回路、その発振周波数制御回路を有するDC−DCコンバータ及び半導体装置

【課題】マイコン等の特別な制御回路が不要で、しかも無線送受信回路で使用する周波数に関係なく、スイッチングノイズの影響を無視できるレベルまでスイッチングノイズを軽減することができる発振周波数制御回路、その発振周波数制御回路を有するDC−DCコンバータ及び半導体装置を得る。

【解決手段】アップ/ダウン制御回路11は、第1クロック信号CLKAと第1分周クロック信号CLKB1との周波数を比較する第1周波数比較回路12と、第1クロック信号CLKAと第2分周クロック信号CLKB2との周波数を比較する第2周波数比較回路13の各出力信号UP及びDOWNに応じて、第2クロック信号CLKB2の周波数が所定の下限値から所定の上限値の間を連続的に変化しながら往復するように、発振回路2に対して、第2クロック信号CLKBの周波数制御を行うようにした。

(もっと読む)

周波数制御回路およびCDR回路

【課題】調整のための外部接続端子を必要とする部品や外部接続部品を必要とする部品を不要にする。

【解決手段】CDR回路は、周波数制御回路と、制御電圧に応じて発振周波数が制御されかつ入力データにより発振位相が制御される再生クロックを生成する第1のVCO2と、再生クロックによって入力データのデータ識別を行うFF1と、制御電圧に応じて発振周波数が制御される第2のVCO3とを備える。周波数制御回路は、第2のVCO3の出力信号の周波数を参照クロックの周波数と比較し、検出した周波数差に応じた信号を出力する周波数比較器4と、周波数比較器4の出力信号に応じて出力するデジタル値を上下させるアップダウンカウンタ5と、アップダウンカウンタ5の出力をアナログ信号に変換してVCO2,3の制御電圧として出力するD/A変換器6とから構成される。

(もっと読む)

PLL回路、無線端末装置、および周波数検出方法

【課題】DCOの最低発振周波数を検出し、分周比Nに比例した制御データから、DCOの制御データへの変換を精度良く行うことが可能な、新規かつ改良されたPLL回路を提供すること。

【解決手段】ディジタル値を用いて制御される発振回路を有するPLL回路であって、搬送波周波数値を設定する搬送波周波数設定部と、搬送波周波数値が変化したことを検出する検出部と、搬送波周波数値が変化したことを示す信号に同期して、発振回路を最低周波数で発振させるための制御信号を送信し、基準周波数の1周期内の発振回路の出力クロック数を計測する計測部と、を含むことを特徴とする、PLL回路が提供される。

(もっと読む)

デジタルPLL回路

【課題】同期信号消失時の同期維持精度が向上されるとともに簡素な回路構成のデジタルPLL回路を提供することである。

【解決手段】同期信号の入力があるときの2つのクリアパルスの間に含まれる内部クロックの数の時系列的な平均値を学習値として記憶する学習値記憶回路と、PLLクロックカウンタのカウント値が学習値の整数成分と一致したとき一致検出パルスを生成する一致検出回路と、一致検出パルスを内部クロックの1周期分遅延して遅延パルスを生成するフリップフロップと、一致検出パルスまたは遅延パルスのいずれか一方を小数補正信号に従って選択し擬似同期パルスとして出力する擬似同期パルス選択回路と、補正区間において遅延パルスの数の擬似同期パルスの数に対する割合が学習値の小数成分に近似するよう選択する小数補正信号を出力する小数補正演算回路と、を有する。

(もっと読む)

PLL回路

【課題】安定かつ最適な位相雑音レベルで動作するPLL回路を提供する。

【解決手段】上記課題を解決するために、PLL回路100は、2つの入力信号の位相差に応じた電圧を出力する位相比較器101と、電流変換利得を調整して入力信号を任意の昇圧率で上昇させる可変チャージポンプ102と、所定の周波数特性を有するループフィルタ103と、VCO104と、ループフィルタ103の出力信号をデジタル値に変換するA/Dコンバータ105と、VCO104を選択するともにA/Dコンバータ105の出力値に応じて可変チャージポンプ102を制御するVCO選択回路106と、VCO104からの出力信号を1/N倍に分周する分周回路107と、を備える。

(もっと読む)

小数部の入出力位相に基づいたデジタル位相同期ループ動作

1つの態様では、デジタルPLL(DPLL)は、入出力位相の小数部に基づいて動作する。DPLLは、入力位相を得るために少なくとも1つの入力信号を蓄積する。DPLLは、例えばタイムデジタルコンバータ(TDC)を使用して、発振器からの発振信号と参照信号との間の位相差に基づいて出力位相の小数部を決定する。DPLLは、入力位相の小数部および出力位相の小数部に基づいて位相エラーを決定する。その後、DPLLは、位相エラーに基づいて発振器のための制御信号を生成する。別の態様では、合成されたアキュムレータを含むDPLLは、参照信号に基づいて、発振信号サイクルの数のトラッキングを保持することにより粗い出力位相を決定する。 (もっと読む)

マルチチャネル・データ検出システム用に構成されたエラー組み合わせ論理およびエラー信号を生成するための方法

【課題】 各チャネル用のフェーズ・ロック・ループを有するマルチチャネル・データ検出システムの位相エラー組み合わせ論理を提供することにある。

【解決手段】 この位相エラー組み合わせ論理は、各チャネルに関する位相エラー情報を受信することと、受信位相エラー情報を結合し、結合された位相エラーを生成するように構成された組み合わせ論理と、結合された位相エラーを少なくとも1つのチャネル・フェーズ・ロック・ループに適用するように構成された位相エラー出力とを含む。さらに、エラー信号組み合わせ論理は、各チャネルに関するフェーズ・ロック・ループに関連する信号のエラー情報を受信することと、受信エラー信号情報を結合し、結合されたエラー信号を生成し、たとえば、信頼性情報により、各チャネルからの受信エラー信号情報に重みを付けるように構成された組み合わせ論理とを含む。エラー補償出力は、結合され重みが付けられたエラー信号を少なくとも1つのチャネル・フェーズ・ロック・ループに適用するように構成される。

(もっと読む)

PLL回路

【課題】位相比較器出力のビット数を極端に増やすことなくループを安定化するとともに、ループ誤差の低減と収束の応答性の向上を実現する。

【解決手段】DCO回路102の入力は、第1の可変利得回路103を介して位相比較器101の出力に接続される。また、設定値Aを設定する手段104と、分周比Nを入力する手段106を持ち、設定値Aを第1の可変利得回路103と等価な利得G2を有する第2の可変利得回路105で変換し、第1の加算回路107で分周比Nから減じた後、第1の可変利得回路103の出力と加算するための第2の加算回路108を持たせる。

(もっと読む)

データリカバリ方法およびデータリカバリ回路

【課題】入力データのジッタの影響を簡単な構成で低減でき、データを正確に復元できるデータリカバリ方法およびデータリカバリ回路を提供すること。

【解決手段】入力データから位相データを検出する選択信号生成部を備え、選択信号生成部が検出した位相データに基づいて入力データをサンプリングするデータリカバリ回路において、選択信号生成部は、入力データの位相と検出済みの位相データが表す位相との位相差を検出する位相差検出部530a〜530dと、位相差の絶対値が位相補正用規定値を超える場合に、位相差の絶対値が位相補正用規定値にクリップするよう位相データを補正するクリップ回路531a〜531dとを備える。

(もっと読む)

半導体集積回路

【課題】ロック動作の初期において高速引き込みを可能とすると伴に入力信号ジッタや入力雑音の影響の小さなディジタルフェーズロックドループを提供すること。

【解決手段】半導体集積回路は、位相比較器10、11、ディジタルループフィルタ12、ディジタル制御発振器13、フィードバック分周器14を含むディジタルフェーズロックドループADPLLを具備する。ディジタルループフィルタ12は、第1ゲインαを有して位相比較器10、11のディジタル位相出力信号θが供給される比例パス12aと、第2ゲインβを有して信号θが供給される積分パス12b、12c、12dと、信号θの大きさを判定する判定器12g、12hを含む。ディジタル位相出力信号θの大きさが所定の基準値θthよりも大きい場合には、判定器12g、12hは第2ゲインβと第1ゲインαとの比β/αを大に設定する。

(もっと読む)

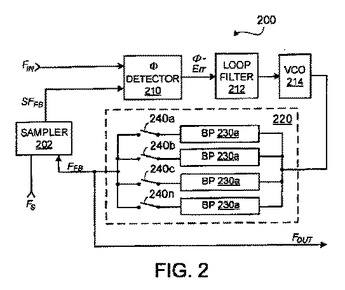

偽信号化された周波数上の位相ロック

位相ロックループ(200)は、サンプラー(202)、位相検出器(210)、ループフィルタ(212)、VCO(214)を含む。ループは、ループのフィードバックパス中に分割器を必要とすることなく周波数逓倍を達成する。VCO(214)は、サンプラーのナイキストレートより上で動作され、ループが偽信号化された信号上にロックすることを引き起こす。VCO出力周波数中のあらゆる変動(即ち、ジッターまたは位相ノイズ)は、周波数分割器に通常関連付けられる減衰無しで、1対1で位相検出器(210)にフィードバックされる。ループゲインは従って、高い閉ループ周波数逓倍を提供するループにおいてでも、高く保つことができる。一変形によると、高調波発生器(540)がVCOとサンプラーの間に置かれ、よってループがVCO周波数の高調波上にロックすることを引き起こす。開ループゲインと精度はよって更に向上される。  (もっと読む)

(もっと読む)

デジタル制御発振回路、周波数シンセサイザ、それを用いた無線通信機器及びその制御方法

【課題】周波数が直線的に変化する範囲が広く且つ占有面積が小さいデジタル発振回路を実現できるようにする。

【解決手段】デジタル制御発振回路10は、複数の第1の可変容量素子からなる第1の容量素子群14及び複数の第2の可変容量素子からなる第2の容量素子群14を含む可変容量部12を有し、可変容量部12の容量値に対応した発振周波数の信号を生成する発振部を備えている。第1の可変容量素子の第1の容量変化量は、第2の可変容量素子の第2の容量変化量に2以上の整数値を乗じた値であり、第2の可変容量素子の個数は、2以上の整数値から1を減じた値以上である

(もっと読む)

クロック生成回路

【課題】 CPUの負荷を軽減するとともに、回路規模またはシステムの規模の増大の抑制が可能なクロック生成回路を提供する。

【解決手段】 制御信号に基づいてクロック信号の周波数を制御して出力する発振回路と、所定期間、発振回路が出力するクロック信号のパルス数をカウントしてカウント値を生成するカウンタと、カウント値と、予め設定された周波数に基づいた設定値と、を減算して差分データを生成する減算回路と、差分データに基づいて、制御信号値を補正する制御信号生成補正回路と、制御値信号をアナログ信号に変換して制御信号を生成し、発振回路に出力するデジタル−アナログ変換回路と、を備えることで、上記課題を解決することができる。

(もっと読む)

周波数同期システム及び周波数同期方法

局部発振器からの局部信号と遠隔発振器からの基準クロック信号の間で周波数を同期させるデジタル周波数ロックループに関連するシステムおよび方法。基準カウンタは、基準クロック信号内のパルスごとにその計数を増分する。基準カウンタ内の値は、設定可能な基準値と比較される。基準カウンタ値と基準値の一致が発生するたびに、ヒット信号が生成され、基準カウンタ値が再初期化される。上記と同時に、局部信号からのパルスごとにフィードバックカウンタが増分される。ヒット信号が生成されると、フィードバックカウンタ内の値が設定可能なフィードバック値と比較(減算による)されて、差の値を生成する。次いで差の値が、局部発振器の周波数を増大または減少させるのに使用するための周波数調整信号に変換される。ヒット信号はまた、フィードバックカウンタを再初期化する。 (もっと読む)

可変遅延回路、可変遅延装置およびVCO回路

【課題】入力信号に対して小さな遅延時間の制御を行うことができる可変遅延回路、可変遅延装置及びVCO回路を提供する。

【解決手段】可変遅延回路は、入力信号を遅延させるトランスファゲートTG1およびトランスファゲートTG3と、トランスファゲートTG1およびトランスファゲートTG3と入力信号との間に設けられるトランスファゲートTG2およびトランスファゲートTG4と、を備えている。

(もっと読む)

PLL回路

【課題】従来のPLL回路は、回路規模と消費電力とが大きい問題があった。

【解決手段】本発明にかかるPLL回路は、それぞれ位相が異なる複数の基準クロックを出力する多相基準クロック出力回路10と、複数の基準クロックのいずれか1つを動作クロックとし、周波数制御入力の値に応じて周波数が変動する出力クロックと、前記周波数制御入力の値に応じて計算される理想位相と出力クロックの位相との位相差を示す遅延量データとを出力するデジタルVCO20と、遅延量データに応じて複数の基準クロックの1つに同期した出力クロックを選択して出力する選択回路30と、を有するものである。

(もっと読む)

分数分周PLL装置、およびその制御方法

【課題】設定すべきパラメータ数が減ぜられて使い勝手の向上が図られると共に、回路の簡略化を図ることが可能な分数分周PLL装置、およびその制御方法を提供すること

【解決手段】第1分周信号fprの初期のAサイクルの期間は、第2分周信号fAがハイレベル、第3分周信号fBがローレベルに維持される。3モジュラスプリスケーラ13は(M+1)分周値となる。引き続くBサイクルでは、第2分周信号fAがローレベル、第3分周信号fBがハイレベルである。3モジュラスプリスケーラ13は、ΣΔ変調器8から出力される擬似乱数の符号に合わせて、負値の場合に(M−1)分周値、正値の場合に(M+1)分周値となる。その後は、M分周となる。比較分周器4では、擬似乱数値Bxを含む(MN+A+Bx)の分周値が得られる。負値を含む擬似乱数をそのまま使用してΣΔ変調による分数分周を実現できる。

(もっと読む)

記録装置及び記録装置の制御方法

【課題】ディスクの回転に安定して同期した記録クロックを生成できるようにする。

【解決手段】ディスク状記録媒体に形成されているウォブルを読み取ってウォブル信号を検出し、前記ウォブル信号に基いて記録用のクロック信号を生成する記録装置であって、前記ディスク状記録媒体のウォブル周期に関連した周波数を有するクロックを生成する第1のクロック生成手段と、前記ディスク状記録媒体にデータを記録するためのチャネル周期に関連した周波数を有するクロックを生成する第2のクロック生成手段とを備え、前記第1のクロック生成手段に組み込まれているDVCO部と同一のDVCO部を組み込んで前記第2のクロック生成手段を構成する。

(もっと読む)

無線装置

【課題】パルスの形状が変動しても、正確な波形サンプルが可能な無線装置を提供する。

【解決手段】入力信号とクロック信号を同期させる同期装置は、入力信号を、所定の間隔の第1と第2のサンプルタイミングでサンプルするサンプル手段102,103と、同期引き込み時に、第1と第2のサンプルタイミングをともにずらし、同期追従時に、第1と第2のサンプルタイミングの間隔を狭める遅延制御手段112とを備える。同期状態判定部105は位相誤差算出部104から出力された位相誤差量から同期しているか否かを判定し、遅延量制御部106に同期状態を出力する。遅延量制御部106は位相誤差算出部104から出力される位相誤差量と同期状態判定部105から出力される同期状態から、可変遅延器107および108に現在設定している遅延量の増減を制御する。

(もっと読む)

位相ロック・ループ内のジッターを決定するためのオンチップ位相誤差計測のための装置。

【課題】 位相ロック・ループ内のジッターを決定するためのオンチップ位相誤差計測の方法及び装置を提供する。

【解決手段】 装置は、位相誤差信号を出力するように構成された位相・周波数検出器を含む位相ロック・ループPLL回路(100)を含む。位相誤差モニター回路(102)は、位相誤差信号を論理的に結合し、論理的に結合された位相誤差信号のパルス幅を各基準クロック・サイクルにおいてプログラム可能な遅延時間と比較して瞬時位相誤差変化を決定することにより、瞬時ピーク位相誤差を決定するように構成される。記憶素子(124)は瞬時位相誤差変化をストアするように構成される。

(もっと読む)

101 - 120 / 156

[ Back to top ]