Fターム[5J106DD44]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | デジタル回路 (2,545) | 演算回路 (156)

Fターム[5J106DD44]に分類される特許

121 - 140 / 156

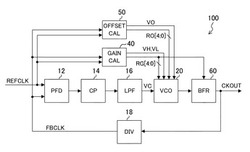

PLL回路及び信号送受信システム

【課題】出力クロック信号のジッタ値に対するプロセスばらつきによる影響を抑える。

【解決手段】PLL回路として、基準クロック信号と出力クロック信号に基づくフィードバッククロック信号との間の位相差を検出する位相周波数比較回路と、前記位相差に応じて電流を出力するチャージポンプ回路と、前記チャージポンプ回路の出力を平滑化し、制御電圧として出力するローパスフィルタと、前記制御電圧、ゲイン制御信号、及びオフセット制御信号に応じた周波数の信号を生成し、前記出力クロック信号として出力する電圧制御発振回路と、前記制御電圧の変化に対する前記出力クロック信号の周波数の変化の比が目標値になるように、前記ゲイン制御信号を求めるゲイン調整回路と、前記制御電圧が所定の値である時における前記出力クロック信号の周波数が目標値になるように、前記オフセット制御信号を求めるオフセット調整回路とを備える。

(もっと読む)

シグマデルタ変調器およびフラクショナル周波数シンセサイザ

【課題】出力信号の増加および減少の振幅を小さくする。

【解決手段】入力信号をシグマデルタ変調した出力信号を出力するシグマデルタ変調器であって、直列に接続された複数の累算器と、それぞれの累算器が出力する比較結果信号に基づいて、出力信号を生成する出力信号生成部とを備え、それぞれの累算器は、入力される信号の値を積分し、積分値が基準値以上となった場合に、所定の値の比較結果信号を出力すると共に、積分値から比較結果信号の値を減算し、初段の累算器には、入力信号の値が入力され、他の累算器には、前段の累算器の積分値が入力され、少なくとも一つの累算器は、積分値の波形の所定の高周波成分を除去するローパスフィルタを有するシグマデルタ変調器を提供する。

(もっと読む)

数値制御型オシレータ(NCO)出力クロック位相平滑化

【課題】 入力クロックに基づく選択可能周波数において複数個のNCOクロックパルスを発生する形態とされている数値制御型オシレータ(NCO)を包含する位相平滑化回路が記載される。

【解決手段】 該複数個のNCOクロックパルスのエッジは該入力クロックのエッジに整合している。位相エラー計算モジュールが該NCOへ結合されており且つ該複数個のNCOクロックパルスの各々に対する対応する位相エラーを発生する形態とされている。クロック位相選択可能遅延が該位相エラー計算モジュールへ結合されており且つ該選択可能周波数において出力クロックを発生するために該対応する位相エラーに従って該複数個のNCOクロックパルスの各々を調節する形態とされている。

(もっと読む)

位相同期ループ回路及び信号発生装置

【課題】回路規模の大幅な増大を招かずに、早期に所望の周波数を有する信号を出力することができる位相同期ループ回路及び当該回路を備える信号発生装置を提供する。

【解決手段】位相同期ループ回路1は、PLL部10と、PLL部10から出力される信号S1の周波数をPLL部10の同調周波数帯域に高速に引き込むためのプリチューン信号S26を生成するプリチューン信号生成部20とを備えている。プリチューン信号生成部20は、PLL部10から出力される信号S1の周波数をカウントするカウンタ21、カウンタ21でカウントされた信号S1の周波数とプリチューン周波数との誤差を示す誤差値が所定の閾値よりも小であるか否かを判定する誤差判定部23、及び誤差判定部23の判定によって誤差値が所定の閾値よりも小となるときのPLL部10に与えられるプリチューン信号S26を記憶するメモリ25を備える。

(もっと読む)

クロック信号源

【課題】周波数拡散させたクロック信号に対して正確な位相シフトを実現する。

【解決手段】周波数拡散クロック源40で周波数拡散されたクロック信号を位相シフタ30で位相シフトさせるとき、演算回路20に対して、周波数拡散クロック40から単位遅延セルの直列接続個数Nsを表す第1のコードを与え、この第1のコードの変化によって表される周波数拡散クロック源40の単位遅延セルの直列接続個数Nsの時間的変化、および希望するシフト量Saに基づいて、位相シフタ30における単位遅延セルの直列接続個数Npを表す第2のコードを生成する。

(もっと読む)

クロック発生回路

【課題】

サイドバンドを低減する。

【解決手段】

カウンタ22は、基準クロックCLKrefをカウントし、カウント値CNTを比較回路24に印加する。加算器26は、入力端子14からの周波数設定値にN+MビットのDFF28のQ出力を加算し、加算結果をDFF28のD入力に印加する。DFF28は、比較回路24からのイネーブル信号ENと基準クロックCLKrefの立ち上がりと立ち下がりに従い、加算器26の出力をラッチする。加算器32は、ランダム値発生回路30からのランダム値をDFF28のQ出力の上位Nビットに加算し、加算結果を比較回路24に印加する。比較回路24は、両入力が等しいときにイネーブル信号を出力する。インバータ20によりQ出力がD入力に帰還接続されるDFF18は、イネーブル信号と基準クロックCLKrefに従いQ出力をハイからロー又はその逆に遷移する。

(もっと読む)

キャリブレーション装置、試験装置、キャリブレーション方法、帯域測定装置、及び帯域測定方法

【課題】PLL回路に対して、予め定められたループ帯域を精度よく設定できるキャリブレーション装置を提供する。

【解決手段】PLL回路の電圧制御発振器に入力される制御電圧に、ループ帯域のカットオフ周波数の周波数成分を含むキャリブレーション信号を重畳する信号重畳部と、電圧制御発振器が出力する発振信号のカットオフ周波数の周波数成分を測定する測定部と、キャリブレーション信号のカットオフ周波数成分の強度と、測定部が測定した周波数成分の強度とを比較する演算部と、演算部における比較結果に基づいて、PLL回路に設けられたチャージポンプのゲインを調整する調整部とを備えるキャリブレーション装置を提供する。

(もっと読む)

クロック発生回路

【課題】クロック逓倍してクロック信号を発生するクロック発生回路のロックインタイムを短縮する。

【解決手段】ロックイン状態において、2つの数値データCi,C(i+1)を積和演算器が出力し、各数値データに従って発振器11の発振周期を設定して、その出力クロック信号のパルス数をカウントして第1および第2のカウント値を生成する。これらの2つの数値データと2つのカウント値と周期目標データとに従って、発振器の発振周期を設定する第3の数値データを生成して、発振器の発振周期を設定する。

(もっと読む)

主にデジタルな時間基準発生器を使用する信号完全性測定のシステム及び方法

1以上の被テスト信号のサンプリングを制御するための、独自の時間基準発生技法を利用する信号完全性測定のシステム及び方法である。本開示に従い作成した時間基準発生器は、位相フィルタ及び変調回路を備えており、これらは、シグマデルタ変調器の出力の関数として、高速に変化する位相信号を発生させるものである。この位相フィルタは、該高速に変化する位相信号から所望でない高い周波数の位相成分をフィルタする。フィルタされた該信号は、1以上のサンプラをクロックするために使用され、それによって上記の被テスト信号のサンプリングの事例を生成する。次に、これらサンプリングの事例を、被テスト信号の種類に適した何らかの1以上の様々な技法を使用して分析する。 (もっと読む)

複数個の出力信号を発生させるフェーズロックループ

【課題】入力クロック信号と同期した複数個の出力クロック信号を調節可能な相対的位相差でもって供給する。

【解決手段】制御可能なオシレータDCOがフェーズロックループの出力信号CKoutを発生し、且つ位相検知器PDがPLL12の入力クロック信号CKinとPLL出力信号CKoutとの間の位相差を決定し、且つオシレータDCOを使用されているクロック信号CKinと同期させる位相検知器出力信号を供給する。ここで、クロック信号CKinと同期されている調節可能な相対的な位相差を有する複数個のPLL出力信号を供給可能にするために、位相差の決定のためにPLLの出力信号CKoutの位相シフトをしたバージョンCK<1:8>を発生し且つ使用されているクロック信号CKinの位相と比較し、且つPLL出力信号CKoutの調節し位相シフトしたバージョンCK<1:8>を更なるPLL出力信号CK<1:8>として供給する。

(もっと読む)

スイッチ可能なフェーズロックループ及びスイッチ可能なフェーズロックループの動作方法

【課題】PLL及びPLLの動作方法に関し、制御可能なオシレータが出力信号を発生し且つPLLの入力クロック信号として使用するために第一クロック信号及び第二クロック信号の間でスイッチオーバーさせる。

【解決手段】現在使用されているクロック信号(CKin1又はCKin2)が出力信号を発生するために、このクロック信号と出力信号との間の位相差が決定され且つオシレータの制御のために使用され、一方現在使用されていないクロック信号(CKin2又はCKin1)が出力信号を発生するために、出力信号に関してのその周波数差が決定され且つ格納され且つ継続的にアップデートされ且つ、前に使用されていないこのクロック信号へのスイッチオーバーの後にオシレータの制御のために提供される。PLL出力信号はどのようなスイッチオーバーに関連する周波数変化よりも迅速に追従することが可能である。

(もっと読む)

半導体集積回路

【課題】フラクショナル−N PLL回路のサイクルトゥサイクルジッターを低減すること。

【解決手段】フラクショナル−N PLL回路は、位相周波数比較器PFD、チャージポンプ回路Ch_Pmp、ループフィルタLp_Flt、電圧制御発振器VCO、フラクショナル分周器DIV、ΣΔ変調器ΣΔModを含む。基準クロック信号RCLKと出力帰還信号VCLKとの位相差の検出動作に基づくループフィルタLp_Fltの出力電圧VCNTの電圧生成動作が時間差を有する複数の動作により実行されるように位相周波数比較器とチャージポンプ回路との一方が構成されている。

(もっと読む)

クロック信号のデューティサイクルを補正するための補正装置

【課題】クロック信号のデューティサイクル補正を行うために、確実かつ簡便に実現される技術を提供する。

【解決手段】クロック信号(CLK)から第1グループおよび第2グループのn個の遅延された各バージョンをそれぞれ生成するために各遅延デバイス(DA、DB)を設ける。第1グループの各バージョンでは前側エッジが後側エッジに対して時間増分τだけずつ段階的に遅延し、第2グループの各バージョンでは後側エッジが前側エッジに対して時間増分τだけずつ段階的に遅延する。第1グループの信号が消失する点での遅延増分値の順序数xを確定する。第2グループの各信号が発振が消失する点での遅延増分値の順序数yを確定する。遅延補正デバイス(DC)を、x>yまたはx<yである場合にクロック信号のパルスの前側エッジまたは後側エッジを(V=τ×|x−y|/2)だけ遅延して補正クロック信号CLK’を得るために制御可能に設ける。

(もっと読む)

周波数推定方法、広帯域周波数弁別器及び無線位置測定用受信機

【課題】 サンプリング周波数の2倍の周波数における回転因子の集合に対応する、DFT演算子と1/2DFT演算子の組み合わせにもとづく周波数弁別器である。

【解決手段】 周波数弁別器は、ゼロ又は不連続点を持たないように選定される。そのため、この発明の弁別器は、拡張された動作範囲において、より安定的かつ良好に動作する。この発明の弁別器は、GPS受信機に適用された場合、初めに大きな誤差が有っても、より確実にキャリヤ周波数にロックすることが可能であるとともに、誤ってロックする問題を防止するものである。

(もっと読む)

ディジタルPLL装置

【課題】入力信号の周波数が変動してもジッタを低減させることが可能なディジタルPLL装置を提供する。

【解決手段】本発明の一実施形態に係るディジタルPLL装置は、入力信号に対する再生クロックの位相遅れ、位相進みを検出する位相検出器と、位相検出器からの出力信号を積分し、積分値に応じて位相ずれ信号を発生するランダムウォークフィルタ部と、入力信号の周波数値に応じた値を有する周波数信号を生成する周波数検出器と、位相ずれ信号の値と周波数信号の値とを加算した値を有する制御信号を生成する加算器と、制御信号の値を分周比として、マスタークロックを分周した再生クロックを生成する制御分周部と、を備える。制御分周部における分周比の中心値N(Nは自然数)は、周波数信号の値によって定められることを特徴とする。

(もっと読む)

デジタルPLL回路及びそれを備えた光ディスク装置

【課題】動作周波数が低く、安価にIC化を行うことができ、設計が容易なデジタル回路を用いて時間分解能の高いクロック信号を生成することができるDPLL回路を備えた光ディスク装置を提供する。

【解決手段】デジタルPLL回路部は、エッジ検出回路部と、クロックデータ生成回路部と、位相差検出回路部とを備え、一周期毎に、デジタルクロックデータから、デジタルクロック信号の立ち上がりエッジ又は立ち下がりエッジの有無を時間分解能単位で示した書き込みタイミング信号を生成して出力する。

(もっと読む)

マルチパス角度変調器の利得を常時較正する方法

マルチパス角度変調は、メイン制御ループに追加されたクローズドの二次ループを含み、高周波利得に関して較正ファクタを自動的に調整する。メイン制御ループは、主要パスとして角度変調信号の低周波部分を処理するように構成され、二次ループは、補助ループとして角度変調信号の高周波部分を処理するように構成されている。二次ループは較正情報を検知し、システムが主要動作を行っている間、較正情報を用いて変調ループ内で常時利得をリアルタイムで較正する。その結果、中断時間などのシステム停止または較正に特異的なタイミングが必要でなくなり、変調パスのバランスがとれる。較正は背景プロセスとして常時行われる。角度変調はすべての変調タイプのシステムに適用可能である。 (もっと読む)

PLL回路およびICチップ

【課題】非接触ICチップに設けられる発振器の周波数を上げることなく、通信の転送レートを上げることができるようにする。

【解決手段】外部からの制御信号に従ってφの値が変更され、cosφで表される発振出力信号と、sinφで表される発振出力信号が可変型発振器71から出力される。可変型発振器71から出力された信号の掛け算、加算等が行われ、信号sin(ωt+φ)と、それを基準としてπ/2だけ位相がずれた信号である信号cos(ωt+φ)が出力される。この出力に基づいて、いまの、クロック信号との位相差などが判断され、位相差に応じた制御信号が可変型発振器71に供給されてくる。本発明は、非接触ICチップに搭載されるPLLに適用することができる。

(もっと読む)

クロックデータリカバリ回路

【課題】 データ信号とクロックとの周波数に差がある場合でも、2相の内部クロックを必要とせずに、データ信号とクロックとの同期が可能なCDR回路を提供すること。

【解決手段】 PD14は、DATAとVDL11からのVDL出力との位相差を検出する。CODE Operator13は、出力クロックの1周期と同じ遅延に相当する制御コードの値を検出する。そして、PD14による検出結果に応じて制御コードを変更しながら出力クロックをデータ信号に同期させる際、VDL11の遅延量がクロックの1周期分を超えるときに、制御コードに対して出力クロックの1周期と同じ遅延に相当する制御コードを一度に加算または減算する。したがって、データ信号とクロックとの周波数に差がある場合でも、同一のクロック位相を与えながらデータ信号とクロックとの同期をとることが可能となる。

(もっと読む)

信号処理装置、信号処理方法

【課題】デジタルPLLのループ遅延の短縮化と、そのデジタルPLLによって位相同期が取られた再生データの高精度化とを両立させる。

【解決手段】ビタビ検出用の位相補間フィルタ9と、PLL8にある位相誤差検出用の位相補間フィルタ81とを設ける。位相オフセット演算器84において位相誤差の積算値である位相オフセット量φに応じて、位相補間フィルタ9および位相補間フィルタ81では、タップ係数が逐次更新されるが、位相補間フィルタ81は、位相補間フィルタ9と比較して、タップ数/ビット幅が小さく設定され、PLL8内のループ遅延時間を短縮する。

(もっと読む)

121 - 140 / 156

[ Back to top ]