Fターム[5J106DD44]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | デジタル回路 (2,545) | 演算回路 (156)

Fターム[5J106DD44]に分類される特許

141 - 156 / 156

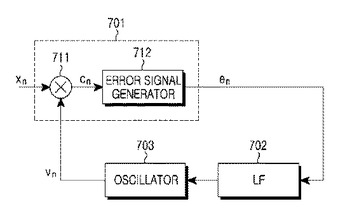

位相固定ループと位相固定ループでの位相検出方法及びこれを用いる受信器

位相固定ループ(PLL)の位相検出動作が行われる間に、低いSNR環境下の定常状態での性能劣化を防止しつつも、獲得状態での収束性能を向上させる位相固定ループと位相固定ループでの位相検出方法及びこれを用いる受信器を提供する。位相固定ループは、入力信号及びフィードバック信号に従って、入力信号が属する期間を判定し、判定された期間に対して設定された式(又はアルゴリズム)を使用することによって、入力信号に対応する誤差信号を出力し、誤差信号に従って所定の周波数信号を発振し、発振された信号をフィードバックする。  (もっと読む)

(もっと読む)

PLL制御のためのシステム及び方法

【課題】フェーズロックループ(PLL)回路に対するロジックの動作の影響を弱めるためのシステム及び方法を提供する。

【解決手段】システムと方法は、PLL回路が命令の予期される影響を命令の実行前、同時、あるいは後で補償することを実質的に許してもよい。より特に、システムの命令の発行に関連したロジックは、命令に基づいたシステムでのPLLに信号を供給してもよい。その後、PLLはこの制御信号に基づいた命令の予期される影響を補償するために調節されてもよい。

(もっと読む)

変調制御回路

【課題】 本発明は、変調された光信号を出射する外部変調器に好適な動作点を設定しつつ変調信号を与える変調制御回路に関し、広範なビットレートによる高品質の変調を可能とすることを目的とする。

【解決手段】 変調信号に重畳される第一のパイロット信号またはこの変調信号に重畳された第一のパイロット信号と、その変調信号に応じて外部変調器11が出射する光信号から抽出した第二のパイロット信号との位相差を検出する位相差検出手段12と、検出された位相差を外部変調器11に帰還し、その外部変調器11の動作点をこの位相差が抑圧される動作点に保つ制御手段13とを備えた変調制御回路において、帰還を実現する帰還路に配置され、かつ変調信号の成分の内、この変調信号の波形に伴う波形の乱れに応じてその帰還路の通過域に分布し得る成分を抑圧する濾波手段14を備えて構成される。

(もっと読む)

デジタル位相同期ループおよび位相同期ループにおける干渉成分を補正する方法

【課題】デジタル位相同期ループが発生させる干渉信号を低減させる。

【解決手段】第1端子(1)と、第2端子(2)と、離散値的な同調発振器(6)と、積算器(10)と、ループフィルタ(11)と、フィードバック経路とを含んだデジタル位相同期ループ内に、補正回路(4)を備えることを提案する。この補正回路(4)は、入力側においては、上記積算器(10)の入力に接続され、そして出力側においては、上記積算器(10)の出力に接続されている。上記補正回路(4)は、上記積算器(10)の入力に供給される作動ワードと第2周波数ワード(FwF)から得られるワードとから、補正ワード(KS)を生成するために設定される。このため、上記積算器(10)から出力される周波数設定ワード内の周期的誤差成分が、上記補正回路(4)によって補正される。

(もっと読む)

位相同期ループ回路のロック検出のためのシステム及び方法

【課題】位相同期ループ回路のロックを検出するためのシステム及び方法。特に、PLLロック検出された出力をアサートする前のユーザー定義の期間に対するPLLの安定性を検出するために構成されたロック検出器。

【解決手段】安定性は、PLL回路に挿入され位相−周波数検出器とチャージポンプとの間に配置されたカウンタにより示されることができる。カウンタ値は位相−周波数検出器により作動されるので、PLLロックはカウンタ値の安定性により示される。デジタルカウンタ値は、デジタルチャージポンプとロック検出回路に同時に供給されることができる。ロック検出器は、いつカウンタ値間の差がユーザー定義の許容値未満になるかを判定するためにレジスタと差検出器を含む。ロック検出器は、カウンタ値がカウンタ値の変動周波数と同じ周波数でサンプリングされる場合に生じる可能性があるロックの誤表示を避けるために、可変タイマーを含むことができる。

(もっと読む)

クロックリカバリ回路

【課題】 回路構成が簡単で、かつデータの伝送速度が高くてもデータ受信後直ちにクロックを再生することのできるクロックリカバリ回路を提供する。

【解決手段】 クロックリカバリ回路100は、受信データの遷移を検出してパルス信号を発生するパルス信号発生回路1と、受信データの最大無遷移期間数より1つ少ない数に相当する複数の遅延素子を直列に接続した遅延素子群2と、予め設定されている受信データの伝送速度に基づいて遅延素子群2のそれぞれの遅延素子の遅延時間が受信データの1データ期間分となるように遅延時間制御信号により制御する遅延時間制御回路3と、遅延素子群2にパルス信号を入力して受信データの1データ期間分ずつ順次遅延させた複数の遅延パルス信号を出力する遅延パルス信号生成回路4と、パルス信号および複数の遅延パルス信号の論理和をとって再生クロック信号として出力する論理和回路5とを有する。

(もっと読む)

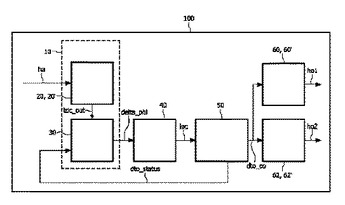

位相ロックループ回路装置及びこれを利用したクロック信号発生方法

回路装置(100)、特にサブクロックまたはサブピクセルの正確な位相測定及び位相発生用の位相ロックループ、並びにこれに対応する方法を、クロック乗算器位相ロックループを時間−ディジタル変換器の後方に設けず、アナログ遅延線も信号除算器ユニットも、ディジタルランプ発振器または離散時間発振器とディジタル−時間変換器との間に設けず、ディジタル環境におけるノイズ及び接地バウンスの影響を受け易いアナログ回路がより少ない方法でさらに発展させるために、少なくとも1つの位相測定ユニット(10);少なくとも1つの位相検出器ユニット(30)の少なくとも1つの出力信号(delta_phi)を供給される少なくとも1つのループフィルタユニット(40, 40’);ループフィルタユニット(40, 40’)少なくとも1つの出力信号、特に少なくとも1つの増分(inc)を供給される少なくとも1つのディジタルランプ発振器ユニットまたは離散時間発振器ユニット(50, 50’)を設け、ディジタルランプ発振器ユニットまたは離散時間発振器ユニット(50, 50’)の少なくとも1つのレジスタユニット(54, 54’)の状態信号(dto_status)は位相検出器ユニット(30)に入力信号として供給され、さらに、少なくとも1つのディジタルランプ発振器ユニットまたは離散時間発振器ユニット(50, 50’)の少なくとも1つの出力信号(dto_co)を供給されて少なくとも1つの出力信号(ho1, ho2)発生する少なくとも1つのディジタル−時間変換器ユニット(60, 62, 60’, 62’)を設けることを提案する。  (もっと読む)

(もっと読む)

位相同期ループ回路および半導体集積回路

【課題】 動作状態を正確に判定することができ、かつ低消費電力の位相同期ループ回路および半導体集積回路を提供する。

【解決手段】 動作状態判定部6は、ループフィルタ3から出力される制御電圧が所定の電圧範囲内にあるか否かに基づいて、PLL周波数シンセサイザが所望の動作状態であるか否かを判定する。電流制御回路51は、判定回路13からの判定信号に基づいて、PLL周波数シンセサイザが所望の動作状態を維持する範囲内において、帰還分周回路5の駆動電流を小さくするように制御する。したがって、PLL周波数シンセサイザの動作状態を正確に判定することができる。また、帰還分周回路5の誤動作を検出することも可能になる。さらに、電流制御回路51を設けたことによって、PLL周波数シンセサイザの低消費電力化が図られる。

(もっと読む)

圧電発振器の周波数調整方法及び周波数調整装置、並びに圧電発振器

【課題】 外部から基準周波数信号を得られないVC−TCXOにおける基板実装後の周波数調整を、簡易に行うことができる周波数調整装置を提供する。

【解決手段】 上記課題を解決するためのVC−TCXOの周波数調整装置は、周波数温度特性を補正する多項式に基づいて補償電圧を発生する電子回路を備えた圧電発振器の基板実装後における発振周波数の調整方法であって、基板実装後の前記圧電発振器の発振周波数を検出し、前記圧電発振器に要求される基準周波数と前記検出した発振周波数との差分を求め、求めた前記差分を前記メモリに予め記憶された前記多項式の定数項の単位定数値あたりの前記発振周波数の前記周波数変化量と比較し、比較結果に基づいて前記圧電発振器に内蔵したメモリに記録された前記定数項の定数値を変える、ことを特徴とする。

(もっと読む)

高符号間干渉耐性位相比較器

【課題】デジタルPLLの位相比較器に於いて、振幅の小さな信号に由来するエッジの誤検出を回避する。

【解決手段】エッジ候補の信号列の符号に加えて、それぞれの絶対値がある閾値を超えた場合のみエッジと判定し位相検出を行う。

【効果】デジタル方式の位相比較器に於いて誤ったエッジを検出する場合を大幅に削減することが出来、本方式の位相比較器を用いたPLLは、従来方式の位相比較器を用いたものの安定性、位相追従精度が著しく劣化するような状況下に於いても良好な動作を実現することが可能になる。

(もっと読む)

分数周波数シンセサイザ

【課題】周波数シンセサイザ回路は、入力基準信号に対して所望する周波数関係を有する出力クロック信号を発生し、適用可能な回路制限範囲において、基本的に任意に関係する値及び調整の解決を提供する。

【解決手段】周波数シンセサイザはその出力クロック信号の複数の位相を提供するリング発振器回路(12)と、位相選択の順序に従って、基準信号の各サイクルにおいて、発振器制御回路(16)に帰還する出力クロック信号の位相を選択する位相選択回路(18)を含む。発振器制御回路は、出力クロック信号の選択された位相と基準信号との比較に応答して制御信号を発生し、位相選択回路は、任意の周波数の調整を可能とする、所望する時間平均値を有する位相選択の順序を発生する変調器(34)を含んでもよい。

(もっと読む)

周波数合成器

要約書なし。 (もっと読む)

通信用半導体集積回路

【課題】 広い周波数範囲で高精度に発振動作ができ、占有面積を増大させずにVCOの使用周波数帯を短時間に選択できる通信用半導体集積回路の提供。

【解決手段】 発振器と発振信号を任意の分周比(整数I+分数F/G)で分周可能な可変分周器とを有する発振回路を備えた通信用半導体集積回路で、外部からの送信開始指示と使用周波数帯情報により、可変分周器に与える分周比を算出の分周比算出回路と、分周比算出回路により算出の分周比により可変分周器を動作させ、発振器に所定レベルの電位を制御電圧として供給した状態で可変分周回路の出力信号の位相と基準信号を分周する固定分周回路の出力信号の位相とを比較して発振器の発振周波数帯を選択のバンド選択回路とを設け、バンド選択回路により発振器の発振周波数帯を選択後、発振器の制御電圧もしくは制御電流を周波数制御回路の出力に切り替えて発振回路を動作させる。

(もっと読む)

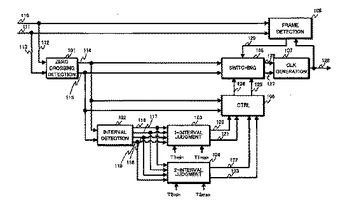

クロック再生回路およびこれを用いた受信装置

信号からシンボルの識別点判定のためのクロック再生回路において、信号に周波数ずれや雑音を含むと、クロック再生の位相引き込みが困難になる。

検波信号には、シンボル交番するプリアンブル部を先頭として、ユニークワード部とデータ部とが含まれている。ゼロクロス検出部は、検波信号の符号変化であるゼロクロスを検出し、ゼロクロス間隔検出部はゼロクロスが発生した時間間隔をカウントする。ゼロクロス1間隔判定部は、ゼロクロス間隔信号が所定範囲内であるかを判定し、ゼロクロス2間隔判定部は、隣接する2つのゼロクロス間隔信号を加算し、ゼロクロス2間隔信号が所定範囲内であるかを判定する。ゼロクロス制御部は、判定結果をもとにゼロクロス信号を制御して、有効ゼロクロス信号を出力する。ゼロクロス切替部はフレーム受信検出部が出力するフレーム受信信号をもとにゼロクロス信号と有効ゼロクロス信号とを切り替え、有効位相誤差情報を出力する。クロック生成部は有効位相誤差情報を入力として、シンボルクロックを生成する。  (もっと読む)

(もっと読む)

サブμ技術に適したデジタル位相同期回路

本発明は、デジタル制御発振器(4)と、位相検出器(11、12、13)と、デジタルループフィルタ(14)とを含む、デジタル位相同期回路に関するものである。上記デジタル制御発振器(4)は、出力周波数を生成するためのものである。上記の位相検出器(11、12、13)は、基準周波数と発振器(4)の出力周波数との位相差を検出するためのものであり、デルタシグマ周波数決定器(11)を含んでいる。上記デジタルループフィルタは、位相検出器の下流に接続されており、デジタル制御発振器(4)を駆動するためのものである。  (もっと読む)

(もっと読む)

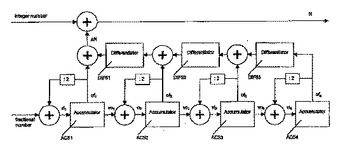

シグマデルタ変調器を有する可変周波数シンセサイザ

シグマデルタ変調器を有する可変周波数シンセサイザが提供される。そのようなシンセサイザは瞬時的な周波数が変化しても正確な平均周波数を与える。シグマデルタ変調器はカスケード接続された複数のアキュムレータ段を有する。シグマデルタ変調器の一部をなすアキュムレータ(51,52,53,54)の少なくとも1つの入力値は、ある因子の乗算されたオーバーフロー信号(of1,of2,of3,of4)に等しい第2成分を有する。このフィードバックは瞬時的な周波数の最大変動を減らす。位相検出器、チャージポンプ及びVCOの非線形性に起因して生じる位相ジッタはそれ故に減少する。

(もっと読む)

(もっと読む)

141 - 156 / 156

[ Back to top ]