Fターム[5J106DD48]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | デジタル回路 (2,545) | 論理回路 (611) | フリップフロップ (296)

Fターム[5J106DD48]に分類される特許

21 - 40 / 296

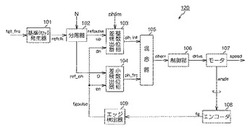

モータ速度制御装置、及び画像形成装置

【課題】安価な構成で、基準パルスと検出パルスの位相差を広範囲、且つ精密に検出でき、外乱に対しても同期はずれの生じる危険性を少なくして、精密なPLL制御が可能な速度制御装置を提供する。

【解決手段】本発明のモータ速度制御装置120は、tgt_frqに基づくrefclkを出力する基準クロック発生器101と、モータ107の所定回転角度ごとに所定数のfgを出力するエンコーダ108と、refpulseを出力する分周器102と、整数位相差ph_intとして出力する整数位相差検出器103と、refpulseのエッジとfgpulseとの時間差を検出してrefclk単位で計測してph_frcとして出力する小数位相差検出器104と、ph_intとph_frcを混合器105で所定の比率で加算してpherrとし、pherrに基づいてモータ107を駆動制御する制御部106と、を備えて構成されている。

(もっと読む)

クロック発生回路、表示装置用駆動回路及びクロック発生回路の制御方法

【課題】電源投入時や通常動作時でも、より確実にクロックの生成が停止した状態から回復することが可能となるクロック発生回路を提供する。

【解決手段】クロック発生回路1は、クロックとデータとが重畳されたエンベデッド信号から抽出クロックを抽出するクロック抽出回路10と、前記エンベデッド信号と前記抽出クロックとに基づき前記抽出クロックの停止を検出し、前記クロック抽出回路を初期状態にリセットするリセット信号を出力する停止検出回路30と、を備えるものである。

(もっと読む)

位相比較回路

【課題】入力信号の周波数比が整数でない場合にも、±180度の範囲で位相差検出ができる位相比較回路を得る。

【解決手段】RF信号と基準信号との立ち上がりエッジを比較してアップ信号またはダウン信号を生成する位相比較コア回路1と、RF信号と基準信号との周波数比をN+K/M(但し、N,K,Mは任意の自然数)とし、RF信号の周波数をfrfとしたとき、アップ信号の立ち上がりの直前のRF信号の立ち上がりに同期して立ち上がり、パルス幅は基準信号の1周期分とほぼ等しく、周期は(M×N+K)/frfとなるマスク制御信号MSK1を生成するマスク信号生成回路2と、位相比較コア回路1により生成されたアップ信号およびダウン信号を、マスク信号生成回路2により生成されたマスク制御信号MSK1に従いマスクする信号マスク回路3とを備えた。

(もっと読む)

PWM信号生成装置

【課題】PWM信号生成装置において、回路規模を小さくして効果的に放射雑音等のノイズを低減する。

【解決手段】CPU204、カウンタ201、レジスタ202、及びコンパレータ205は基準クロックの周波数をその一周期未満の時間で変動させた変動クロックを生成する。TFF206は基準クロックに応じて変動クロックを第1のPWM信号として出力する。TFF251は基準クロックを所定の時間遅延させた遅延クロックに応じて変動クロックを第2のPWM信号として出力する。セレクタ252は第1及び第2のPWM信号を選択的にPWM信号として出力する。

(もっと読む)

PLL回路

【課題】サイクルスリップが発生することでPLL回路の引き込み時間が遅れるという問題がある。そのため、サイクルスリップを低減し、高速にロックを行なうPLL回路の提供が望まれる。

【解決手段】図1に示すPLL回路は、位相比較器と、位相比較器と接続されるチャージポンプと、を備えている。さらに、位相比較器は、基準クロックを遅延させたクロック及びフィードバッククロックを遅延させたクロックに基づき、チャージポンプの出力電圧を上昇させる第1のUP信号及びチャージポンプの出力電圧を下降させる第1のDW信号を生成する制御信号生成回路と、基準クロックに同期させ、第1のUP信号に基づきチャージポンプの出力電圧を上昇させる第2のUP信号を出力する第1の保持回路と、フィードバッククロックに同期させ、第1のDW信号に基づきチャージポンプの出力電圧を下降させる第2のDW信号を出力する第2の保持回路と、を含んでいる。

(もっと読む)

信号生成装置及び周波数シンセサイザ

【課題】PLLを用いた周波数シンセサイザにおいて、簡素な構成でありかつスプリアス特性が良好であること。

【解決手段】位相比較部に入力する参照周波数信号を、ディジタル信号からなる鋸波のゼロクロスポイントを検出したときのクロックに基づいて生成する。しかしこの場合ディジタル値が飛び飛びの値であることから正負の符号が逆転するときにディジタル値がゼロとなるとは限らない。そこで前記ディジタル値が徐々に変化する領域において正、負の符号が逆転するゼロクロス時の直前のディジタル値及び直後のディジタル値を読み出したクロック信号を夫々P1及びP2とし、クロック信号P2の次のタイミングのクロック信号をP3とすると、P1とP2で読み出されるディジタル値の比率に対応する比率でP1、P3を使用する。

(もっと読む)

半導体集積回路およびその動作方法

【課題】ループフィルタをオンチップ化する際、トランジスタの素子サイズのバラツキによるPLL回路の特性バラツキを軽減して、回路規模と消費電力の増大を軽減する。

【解決手段】半導体集積回路は、位相周波数比較器1とループアッテネータ2とチャージポンプ3とループフィルタ4と電圧制御発振器5と分周器6を具備するフェーズロックドループ回路を内蔵する。アッテネータ2は、サンプリング回路21とカウンタ22とを含む。回路21にサンプリングパルスSPL_CLKと位相周波数比較器1から出力される第1と第2の出力信号が供給され、回路21はサンプリング出力信号を出力する。カウンタ22は回路21から出力される所定個数のサンプリングパルスのカウントアップを完了すると、カウントアップ完了出力信号を出力する。チャージポンプ3は、カウントアップ完了出力信号に応答してループフィルタ4に充電電流または放電電流を出力する。

(もっと読む)

サンプリングクロック生成回路、画像読取装置及び電子機器

【課題】アパーチャディレイをより小さくするアパーチャディレイ調整機能を有するサンプリングクロック生成回路を提供する。

【解決手段】SSCG11からの出力クロック信号に対して所定の遅延量だけ遅延してサンプリングクロック信号を発生してサンプリングホールド回路に供給する、遅延回路21,22及びクロック発生器23からなるサンプリングクロック生成手段と、SSCG11の出力クロック信号に基づいて生成されたCCD駆動クロック信号と、上記サンプリングクロック信号とを位相比較して位相比較結果を出力する遅延型フリップフロップ24と、上記位相比較結果に基づいて、上記駆動クロック信号と上記サンプリングクロック信号との位相差が実質的にゼロとなるように上記サンプリングクロック生成手段の遅延量を制御する制御ロジック回路20とを備えた。

(もっと読む)

クロック生成装置及びDLL(DigitalLockedLoop)回路及びクロック生成方法

【課題】回路規模が小さく、また設計が容易な構成にて、高精度なクロックを生成するDLL回路を実現する。

【解決手段】DLL回路は、外部から入力される動作クロックclksと前記動作クロックと周波数が異なるもしくは等しい入力クロックと所望の周波数を表す設定値kから前記動作クロック周波数の前記設定値k分の一の周波数を有する生成クロックclkcを生成するクロック生成部100と、前記生成クロックclkcと外部から入力される参照クロックclkrの位相差を比較し、その位相差を出力する位相比較部200と、前記位相比較部200の出力である位相差から、前記位相差を“0”とするように前記設定値kへ補正をする補正値を生成し、前記設定値kへ補正値を加算する補正部300とを備える。

(もっと読む)

シリアルデータの受信回路、受信方法およびそれらを用いたシリアルデータの伝送システム、伝送方法

【課題】単一の伝送路で、高速なシリアルデータを伝送可能な伝送技術を提供する。

【解決手段】受信回路100は、pビットに2×q回(p、qは実数)の割合で第1レベルから第2レベルへの遷移が生ずるように生成されたシリアルデータDSOUTを受ける。VCO60は、入力された制御電圧Vcnt2に応じた周波数を有するサンプリングクロック信号CLK4を発生する。第1分周器22は、サンプリングクロック信号CLK4を分周比Mで分周する。第2分周器24は、受信したシリアルデータに応じたクロック信号CLKINを分周比Nで分周する。周波数比較器20は、第1分周器22の出力信号と第2分周器24の出力信号の位相差に応じた位相周波数差信号PFDを発生する。制御電圧生成回路42は、位相周波数差信号PFDに応じて、チャージポンプ回路40の周波数を調節するための制御電圧Vcnt2を生成する。

(もっと読む)

PLL回路、PLL回路の誤差補償方法及び通信装置

【課題】デジタル制御発振器を持つPLL回路に用いられるTDC回路の有限な分解能により発生する周期性誤差を補償することが可能なPLL回路を提供する。

【解決手段】発振回路の累積クロック数をデジタル値として検出する累積クロック数検出部と、前記発振回路の累積クロック数の小数部のデジタル値の、第1の基準クロックを基準とする周期性を検出する周期検出部と、前記発振回路の出力クロックの1周期のデジタル値、前記発振回路の累積クロック数の小数部が持つ周期性の1周期のデジタル値、および前記発振回路の累積クロック数の小数部が持つ周期性の各周期の開始点から前記第1の基準クロック数をカウントした値から補正値を算出する補正値算出部と、前記周期性の各周期の開始点から前記第1の基準クロックの周期で、前記累積クロック数の小数部に前記補正値を加算する加算部と、を備える、PLL回路が提供される。

(もっと読む)

周波数シンセサイザおよび時間デジタル変換器

【課題】周波数シンセサイザにおいて、ループ帯域内位相ノイズの低減を小面積かつ低電流の構成で実現する。

【解決手段】周波数シンセサイザは、発振器1と、発振器1出力の分周信号CKVと参照信号Frefとの正規化された位相差を検出するTDC回路7とを備え、TDC回路7によって検出された正規化された位相差に基づいて発振器1の周波数を制御する。TDC回路7は、第2の発振器711と、第2の発振器711の出力信号OSC2の周期数をカウントするカウンタ712とを備え、カウンタ712の出力から、分周信号CKVの周期に相当するカウンタ値と、分周信号CKVと参照信号Frefとの位相差に相当するカウンタ値とを得て、これらのカウンタ値に基づいて、正規化された位相差を算出する。

(もっと読む)

デジタル位相比較器およびこれを備えたデジタルPLL回路

【課題】デジタル位相比較器におけるスタートアップ時のキャリブレーションを不要とする。

【解決手段】基準信号を遅延させて遅延基準信号として出力し、遅延量に相当する時間差を有する遅延量信号を出力する手段と、遅延基準信号と発振器出力信号との時間差をデジタル値に変換し第1のデジタル値として出力する手段と、第1の時間量子化器で発生した時間残差を検出し、時間残差に応じた時間差を有する時間残差信号を出力する手段と、基準信号の状態に応じて時間残差信号を出力するか遅延量信号を出力するかを切り替える手段と、時間残差信号の時間差をデジタル値に変換して第2のデジタル値として出力し、遅延量信号の時間差をデジタル値に変換して第3のデジタル値として出力する手段と、第2のデジタル値および前記第3のデジタル値を用いて第1のデジタル値を補正することで小数位相を算出する手段と、を有する。

(もっと読む)

位相周波数比較回路及びPLL回路

【課題】入力クロックが停止しても出力クロックの周波数を保持するPLLを用いて、ロジック回路を駆動する方法を提供する。

【解決手段】位相周波数比較回路をPFD主要部と基準クロック停止検出部202Bの二つのモジュールから構成する。基準クロック停止検出部202BはPFD主要部のRS−FFのデータ端子に基準データ信号pfd_in_enを出力する。この基準データ信号pfd_in_enは、基準クロック停止検出部202B内のフリップフロップ202B−1に由来して生成される。このフリップフロップ202B−1は位相比較動作の終了を表すオーバラップ信号overlapをタイミングとし、基準クロックref_clkによってリセットされる。基準クロックref_clkが停止すると、基準データ信号pfd_in_enは「L」のままとなり、結果PFD主要部の動作が停止する。

(もっと読む)

クロック発振回路及び半導体装置

【課題】起動時にTDCにキャリブレーション処理を加えることで、時間分解能のばらつきが発生することを防ぎ、合わせて、遅延用の素子の冗長度を減らすことで回路規模の増大を防ぐ手段を提供する。

【解決手段】電源投入時等に多相発振器型TDCであるPDC_c及びバーニア型TDCであるPDC_fのキャリブレーションを実行する。キャリブレーション時にはPDC_fに入力するタイミング入力を参照クロックCLK_REFからDCCOの出力信号のうち一つを選択する。またデータは、先のDCCOの出力信号に隣接し、位相が進んだ出力信号とし、その間の遅延を導出する。これを全出力信号繰り返すことで、DCCOの出力信号1周期を導出する。

(もっと読む)

半導体装置

【課題】再開トリガ信号を生成できないことによってリードデータの出力タイミングと外部クロック信号の同期が外れてしまうことを防止する。

【解決手段】DLL回路100には、当該DLL回路100を初期起動させるリセット信号RESETと、内部クロック信号LCLKの内部クロック信号ICLKに対する遅延量の制御を当該DLL回路100に再開させる再開トリガ信号RESTARTとが入力され、DLL回路100は、リセット信号RESET又は再開トリガ信号RESTARTが活性化されたことに応じて遅延量の制御を開始し、リセット信RESET号が活性化された後再開トリガ信号RESTARTが活性化される前には、当該DLL回路100のロック後にも遅延量の制御を継続し、再開トリガ信号RESTARTが活性化された後には、当該DLL回路100のロックに応じて遅延量の制御を停止する。

(もっと読む)

インテグレーテッドPLLを備えたPWMコントローラ

【課題】PWMコントローラチップのサイズ、コスト及び製造上の複雑を減らす。

【解決手段】位相ロックループ(PLL)を用いた電子部品に電力を供給するためのパルス幅変調(PWM)コントローラが、提供される。PWMコントローラは、基準信号を受信する入力ノードと、位相ロックループ(PLL)とを備えている。このPLLは、位相信号を受信し且つ前記誤り訂正信号に関係する周波数を有する発振器信号を生成する発振器と、前記発振器に結合され、前記基準信号を受信し、且つ前記基準信号と、フィードバック信号との間の位相差に基づいて前記位相信号を生成させる位相周波数検出器(PFD)と、前記PFDに結合され、周期的にPFDが前記位相信号を生成することができるようにする抑制回路と、前記PFDに結合され、前記位相信号が同時に活性である時間の長さを制限するように動作可能なフィードフォワード回路とを備えている。

(もっと読む)

位相比較器およびクロックデータリカバリ回路

【課題】充放電流を切り替えるスイッチを確実に動作させ、高速化に対応できチャージポンプ回路の機能を保持できる位相比較器およびクロックデータリカバリ回路を提供する。

【解決手段】入力データと第1のラッチ111のラッチデータの論理不一致を検出する第1の検出回路と、第1のラッチのラッチデータと第2のラッチ112のラッチデータの論理不一致を検出する第2の検出回路と、第1の検出回路および第2の検出回路の検出結果に応じて、電流を充電または放電を切り替えるための切替スイッチ機能を含むチャージポンプ回路と、を有し、第1の検出回路、第2の検出回路、およびチャージポンプ回路は、第1および第2の検出回路の論理不一致判定部とチャージポンプ回路の充放電流を切り替える切替スイッチとが複合化された検出回路複合型チャージポンプ回路120として形成されている。

(もっと読む)

局部発振器

【課題】PVTに依存しない安定した位相雑音特性を短時間で得ることができる局部発振器を提供する。

【解決手段】局部発振器は、デジタル制御発振器と、位相データ生成器と、減算器と、ループフィルタと、乗算器と、係数算出器と、を備える。前記デジタル制御発振器は、第1の発振器制御値により発振信号の発振周波数を制御可能である。前記発振周波数は、前記第1の発振器制御値と、前記第1の発振器制御値の単位値あたりの前記発振周波数の変化量と、の積に等しい。設定周波数データは、設定周波数を基準信号の基準周波数で除算して得られる。前記乗算器は、前記ループフィルタからの規格化制御値に第1の係数を乗算した前記第1の発振器制御値を出力する。前記係数算出器は、前記発振周波数が前記設定周波数に略等しくなった時の前記第1の発振器制御値を、前記設定周波数データで除算し、その除算結果を新たな前記第1の係数として前記乗算器に設定する。

(もっと読む)

半導体集積回路および無線通信装置

【課題】小規模かつ低消費電力で発振信号を生成可能な半導体集積回路およびこれを用いた無線通信装置を提供する。

【解決手段】半導体集積回路は、デジタル制御発振器と、カウンタと、時間デジタル変換器と、加算器と、制御信号生成部と、を備える。時間デジタル変換器は、発振信号と参照信号との位相差に対応する第3のデジタル信号を生成する。前記時間デジタル変換器は、分周器と、複数のインピーダンス素子と、位相差検出部と、を有する。分周器は、前記発振信号を分周して複数の分周信号を生成する。複数のインピーダンス素子は、前記複数の分周信号を分圧して、前記発振信号を遅延させた複数の遅延信号を生成する。位相差検出部は、前記参照信号と、前記複数の遅延信号のそれぞれと、を比較することにより、前記参照信号と前記発振信号との位相差に対応する前記第3のデジタル信号を出力する。

(もっと読む)

21 - 40 / 296

[ Back to top ]