Fターム[5J106DD48]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | デジタル回路 (2,545) | 論理回路 (611) | フリップフロップ (296)

Fターム[5J106DD48]に分類される特許

61 - 80 / 296

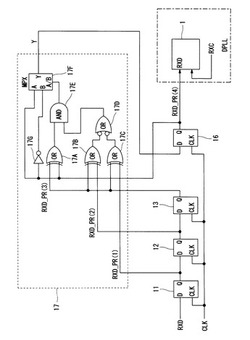

DPLL回路

【課題】入力データに混入したノイズの幅がクロック周期程度にまで大きくなり、ノイズ位置が入力データの中間位置に発生した場合にも、入力データからノイズを除去できる。

【解決手段】1ビットを4クロック幅で構成する入力データからノイズフィルタで雑音を除去し、この雑音を除去した入力データと同期したクロックを生成するDPLL回路において、ノイズフィルタは、入力データに対して、4段縦続接続のシフトレジスタを設け、このシフトレジスタのレジスタ11,12,13のクロック同期した出力の一致・不一致状態に応じて最終段のレジスタ16の入力を切り替える入力ロジック17を設ける。

さらに、ノイズフィルタでは除去しきれない入力データの歪みを歪み除去回路で除去する。

(もっと読む)

受信回路及びサンプリングクロック制御方法

【課題】1ユニットインターバルに対するサンプリング数を一定に保つことができる受信回路を提供することを課題とする。

【解決手段】1サイクル内で複数の異なる位相のクロック信号を生成するクロック発生回路(301)と、複数の異なる位相のクロック信号により入力データをオーバーサンプリングするオーバーサンプリング回路(303)と、オーバーサンプリング回路により出力されたデジタルデータの時系列の変化点を検出し、1ユニットインターバルの両端の2個のデータバウンダリを判定するデータバウンダリ判定回路(305)と、判定された2個のデータバウンダリの間の1ユニットインターバルのサンプリング数が閾値より多いときには、隣接する1ユニットインターバルのサンプリング数が一定となるようにクロック発生回路で生成するクロック信号の位相を制御するクロック位相制御回路(306)とを有する受信回路が提供される。

(もっと読む)

PLL周波数シンセサイザ

【課題】デジタル制御発振器の周波数を安定して制御する。

【解決手段】PLL周波数シンセサイザ(101)は、基準クロック信号とPLL周波数シンセサイザの出力信号との位相差を検出する位相比較器(2)と、位相差に応じた整数値および小数値の和からなる制御値を出力するループフィルタ(4)と、第1のクロック信号に同期して、整数値に相当する第1のデジタル制御信号を出力する周波数制御部(6)と、第1のクロック信号よりも高い周波数の第2のクロック信号に同期して、平均値として小数値を表す第2のデジタル制御信号を出力する周波数制御部(7)であって、当該PLL周波数シンセサイザがロック状態にあるとき、第2のデジタル制御信号の取り得る値の範囲をロック時の範囲に制限する周波数制御部と、第1および第2のデジタル制御信号によるそれぞれの周波数制御の組み合わせに応じた周波数で発振するデジタル制御発振器(10)とを備えている。

(もっと読む)

受信装置及びゲイン設定方法

【課題】受信特性を向上させることのできる受信装置を提供する。

【解決手段】受信装置は、受信データD1に基づいて抽出クロックCLKを生成するクロックデータリカバリ回路2と、受信データD1のジッタ量に応じて、上記クロックデータリカバリ回路2内のフィルタ回路11のゲインパラメータG1を設定するゲイン設定部3とを有する。

(もっと読む)

半導体集積回路

【課題】チップ面積の更なる縮小化を図ることができる半導体集積回路を提供する。

【解決手段】ディジタル制御発振器50−1〜50−nと、位相データ出力部100−1〜100−nと、積分処理部150と、フィルタ部151と、フィルタ部151からの時分割された出力信号に所定の係数を乗算した値を発振器制御値OTWとして出力する乗算器(第1の乗算器)40と、リファレンス周波数Frefに同期して、発振器制御値OTWを各ディジタル制御発振器50−1〜50−nに振り分ける出力セレクタ(制御値分離部)42と、を備える。

(もっと読む)

アンロック検出回路

【課題】2つの信号間の位相差の発生を正確に検出するアンロック検出回路を提供する。

【解決手段】アンロック検出回路は、論理値を基準信号の変化に応じて記憶する第1フリップフロップと、論理値を入力信号の変化に応じて記憶する第2フリップフロップと、当該第1及び第2フリップフロップの出力の否定論理積を算出するNAND回路とを備えた位相比較器と、第1フリップフロップの出力を基準信号の変化に応じて記憶する第3フリップフロップと、第2フリップフロップの出力を入力信号の変化に応じて記憶する第4フリップフロップとを備えた第1アンロック検出器と、NAND回路の出力を基準信号の変化に応じて記憶する第5フリップフロップと、NAND回路の出力を入力信号の変化に応じて記憶する第6フリップフロップとを備える第2アンロック検出器と、第3、第4、第5及び第6フリップフロップの出力の論理和を算出するOR回路とを具備する。

(もっと読む)

CDR回路

【課題】入力データと再生クロックの確実な同期と再生クロックの適切なジッタ低減とを両立させる。

【解決手段】CDR回路は、入力データが遷移したときにパルスを出力するゲーティング回路2と、ゲーティング回路2の出力パルスのタイミングに合うように出力クロックの位相を調整するG−VCO3と、G−VCO3から出力されるクロックのタイミングに合うように出力クロックの位相を調整するVCO4と、入力データのデータ識別をVCO4から出力される再生クロックに基づいて行うフリップフロップ1と、G−VCO3の出力端子とVCO4の入力端子との間に設けられたバッファ増幅器6aとを備える。バッファ増幅器6aは、外部から入力される駆動力制御信号に応じて駆動力が調整される駆動力調整機能付きバッファ増幅器である。

(もっと読む)

PLLロック検出回路、及びPLLロック検出回路を有するPLLシンセサイザ回路

【課題】適切にPLL回路ロックがなされているか否かを検出する。

【解決手段】PLL回路ロックがなされているか否かを検出するPLLロック検出回路を構築する。ここにおいて、そのPLLロック検出回路は、基準発振器から供給される基準発振周波数を示す基準発振周波数信号と、前記基準発振周波数を分周して得られたリファレンス周波数を示し位相比較器に供給されるリファレンス周波数信号と、VCOから供給される電圧制御発振周波数を分周して得られた比較周波数を示し前記位相比較器に供給される比較周波数信号とを受ける、そして、前記リファレンス周波数信号と前記比較周波数信号とに基づいて、前記PLL回路ロックを示すロック検出信号を出力する。

(もっと読む)

CDR回路

【課題】周波数安定度が高くジッタの少ない再生クロックを生成する。

【解決手段】CDR回路は、入力データ4が遷移したときにパルスを出力するゲーティング回路10と、位相同期ループ中に配置されたVCO12と、ゲーティング回路10の出力パルスのタイミングに合うように再生クロック7の位相を調整することにより、入力データ4とタイミングの合った再生クロック7を出力するG−VCO13と、入力データ4のデータ識別を再生クロック7に基づいて行うフリップフロップ3とを備える。入力データ4のデータレートと等しい周波数の参照クロック5またはVCO12の出力クロックは、注入信号9としてG−VCO13に入力される。

(もっと読む)

CDR回路

【課題】入力データに対する瞬時応答特性を備えかつジッタが大きな入力データが入力された時にも出力ジッタを低減可能な小型低消費電力のCDR回路を提供する。

【解決手段】CDR回路は、入力データ4のタイミングに合うように出力クロックの位相を調整するVCO11と、VCO11の出力クロックのタイミングに合うように再生クロック7の位相を調整するVCO13と、VCO11,13の発振周波数を制御する制御信号8を発生する周波数制御回路である周波数比較器2およびVCO12と、VCO11の出力端子とVCO13の入力端子との間に挿入された減衰器30とを備える。

(もっと読む)

CDR回路

【課題】入力データに対する瞬時応答特性を備えかつジッタが大きな入力データが入力された時にも安定的な動作が可能でかつ出力ジッタを低減可能な小型低消費電力のCDR回路を提供する。

【解決手段】CDR回路は、入力データ4が遷移したときにパルスを出力するゲーティング回路10と、ゲーティング回路10の出力パルスのタイミングに合うように出力クロックの位相を調整するVCO11と、VCO11の出力クロックのタイミングに合うように再生クロック7の位相を調整するVCO13と、入力データ4のデータ識別を再生クロック7に基づいて行うフリップフロップ3と、ゲーティング回路10の出力端子とVCO11の入力端子との間に設けられたバッファ増幅器16と、VCO11の出力端子とVCO13の入力端子との間に設けられたバッファ増幅器17とを備える。

(もっと読む)

周波数ジェネレータ

【課題】 DDSを用いて高速スイープを可能にすると共に、周波数設定を容易に行うことができる周波数ジェネレータを提供する。

【解決手段】 スイープ制御部1が、スタート周波数やスイープ周波数ステップ設定値等の周波数設定値を入力して十進数の周波数設定データを出力し、周波数設定データ変換部2が、スイープ制御部1から入力された十進数に、動作周波数、DDS3への入力設定データのビット数、スイープ周波数のステップ設定値に基づく係数をスイープ制御部から入力される十進数の周波数設定データに乗算することで二進数に変換するbitデータ変換部21と、丸め処理を行う丸め処理部22とを備え、DDS3が、入力された二進数の周波数設定データに従って周波数信号を生成して出力する周波数ジェネレータである。

(もっと読む)

スペクトラム拡散クロックジェネレータ

【課題】入力クロックの周波数変化に依存して変調プロファイルが変化しないスペクトラム拡散クロックジェネレータを提供する。

【解決手段】スペクトラム拡散クロックジェネレータは、切替信号に応じて入力クロックを遅延し、出力クロックとして出力する遅延ラインと、入力クロックの周期を計測する入力クロック周期計測部と、入力クロック周期計測部の計測結果に応じて、1変調周期当たりの出力クロックのサイクル数、および、あらかじめ設定された変調度に対応する入力クロックの所定サイクル当たりの出力クロックの周期の変調ステップ幅を算出し、算出されたクロックサイクル数および変調ステップ幅に基づいて切替信号を生成する遅延ライン制御部とを備えている。

(もっと読む)

クロック装置

【課題】複数のクロック信号を出力するPLL回路において、その特性を問わず、リセットを従来よりも適切なタイミングで行うことを目的とする。

【解決手段】クロック装置は複数のクロック信号を出力するクロック回路を備え、出力するクロック信号を使用して動作している複数の周辺回路からエラー信号を受信し、受信したエラー情報を用いて、前記クロック回路をリセットするか否かを判定し、リセットすると判定した場合に、前記クロック回路をリセットする。

(もっと読む)

ディレイロックループのディレイロック状態の情報の使用が可能な半導体素子

【課題】階層的遅延ラインを有するディレイロックループのディレイロック状態を検出し、ディレイロック状態の情報の使用が可能な半導体素子を提供する。

【解決手段】

コース遅延ライン及びファイン遅延ラインを有する階層的遅延ライン構造のディレイロックループブロックと、ディレイロックループブロックから出力された位相比較信号及びコース遅延調整終了信号に応答してコース遅延調整終了時点での比較対象クロックの位相状態を記憶する位相状態記憶手段と、位相比較信号、コース遅延調整終了信号及び位相状態記憶手段から出力された位相状態信号に応答して、ファイン遅延調整に係る位相比較信号の遷移時点を検出して、その時点にアサートされるディレイロック信号を生成するディレイロック状態検出手段とを備えてなる。

(もっと読む)

位相同期ループのジッタ検出方法及び装置

【課題】別途のジッタ計測装備を使用せずとも位相同期ループのジッタ水準を検出できる位相同期ループのジッタ検出方法及び装置を得る。

【解決手段】基準クロックとフィードバッククロックとの位相差信号を検出し、その位相差信号によって一定の周波数の発振信号を生成する位相同期ループと、入力遅延制御信号によって多数のキャパシタをスイッチングし、前記位相同期ループからの前記位相差信号を前記遅延制御信号によって遅延させる可変位相遅延部と、前記位相同期ループからの前記位相差信号と前記可変位相遅延部によって遅延された位相差信号とを比較し、前記位相差信号の遅延期間を検出する比較部と、前記比較部から検出された遅延期間以後にロック範囲内に位置することを検出するロック検出部とを備える。

(もっと読む)

多相クロック間の相間スキュー検出回路、相間スキュー調整回路、および半導体集積回路

【課題】N相クロックの相間スキューの検出を行なうための基準クロックを半導体集積回路内で生成する。

【解決手段】分周回路14は、N相(4相)クロックCLK1/CLK2/CLK3/CLK4をN+1個(6個)の分周クロックA4(−1)/A1(0)/A2(0)/A3(0)/A4(0)/A1(+1)に分周し、位相比較対象クロック生成回路12は、分周クロックA1(0)/A2(0)/A3(0)/A4(0)から位相比較対象クロックB1/B2/B3/B4を生成する。位相比較基準クロック生成回路13は、分周クロックA4(−1)/A1(0)/・・・/A1(+1)から所定の組み合わせと演算規則に従いN個(4個)の基準クロックC1/C2/C3/C4を生成する。そして、位相比較対象クロックB1/B2/B3/B4と基準クロックC1/C2/C3/C4のそれぞれの位相差を検出する。

(もっと読む)

ADPLL回路、半導体装置及び携帯情報機器

【課題】ADPLL環境下またはADPLL環境に近い環境下において、ABSの精度向上手段を提供し、ABSの処理時間短縮を実現する。

【解決手段】ABS103中のデジタル周波数比較器103−1に、DPFD102の出力するDPE信号の初期位相差を格納するDFFを用意する。ABS動作開始直後に、DPFD102が出力するDPE信号はDPFD102の内部回路の初期位相差を表すものであるとしてDFFに記録する。以後デジタル周波数比較器103−1は入力されるDPE信号からDFFに記録された初期位相誤差を引いたものでABSを行い、高速かつ安定したABS動作の実現を図る。

(もっと読む)

デジタルPLL回路とその制御方法

【課題】比較的簡易な回路構成で、制御時定数を短くしても超高安定な位相同期を実現する。

【解決手段】基準クロックを1/m分周器12で1/m倍し、VCXO11で発生される発振クロックを1/n分周器13で1/n倍し、両クロックを量子化位相比較器14に送り、両クロックのずれ量に相当する量子化位相差δを取得して予測制御器15に送る。予測制御器15では、入力された量子化位相差を、その極性が負から正に反転してから再び負に反転するまで、または正から負に反転してから再び正に反転するまで積分し、この積分値に-0.5倍〜-0.05倍の予測係数を掛けた値を予測重み値として求め、この予測重み値を積分値に加算して制御電圧値を予測する。この予測制御器15で予測された制御電圧値を、D/A変換器16でアナログ電圧に変換し、LPF17によって決まるループ時定数でフィルタリングして、周波数制御電圧としてVCXO11に送る。

(もっと読む)

半導体装置

【課題】デジタルDLL回路における消費電力を低減するとともに、ノイズによる電源電圧の変動の影響を軽減することが可能な半導体装置を提供すること。

【解決手段】デジタルDLL回路を備える半導体装置において、位相比較の間欠間隔を設定する間欠間隔設定回路を設ける。間欠間隔設定回路による間欠間隔の設定は、外部から入力される設定信号に基づいて制御する。これにより、ノイズによる電源電圧の変動の影響を軽減し、平均化された遅延素子の段数の調整が可能となる。

(もっと読む)

61 - 80 / 296

[ Back to top ]