Fターム[5J106DD48]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | デジタル回路 (2,545) | 論理回路 (611) | フリップフロップ (296)

Fターム[5J106DD48]に分類される特許

141 - 160 / 296

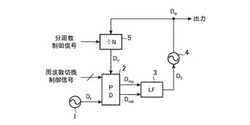

位相同期ループ形周波数シンセサイザ

【課題】サイクルスリップの発生を防止して、短時間で周波数の切り換えを行うことができる位相同期ループ形周波数シンセサイザを得ることを目的とする。

【解決手段】 VCO4により発振される高周波信号Doの周波数が切り換えられる場合、位相比較器2が第1の位相比較信号Dnuと第2の位相比較信号Dndの差分を一定に保持するように構成する。これにより、サイクルスリップの発生を防止して、短時間で周波数の切り換えを行うことができる効果を奏する。

(もっと読む)

DLL回路、および半導体装置

【課題】DLLクロックが消失した場合に、位相検知における誤判定の結果を基に、遅延量が更新されることを回避し、ロック制御におけるDLLクロックサイクルの短縮化と、DLL回路の動作安定性の向上を図る。

【解決手段】本発明のDLL回路は、入力されるクロック信号の遅延量を制御する遅延信号を出力する遅延制御回路13と、この遅延信号に基づいた遅延量をクロック信号に付加し、DLLクロックとして出力する遅延回路12と、DLLクロック信号のクロッキング動作の有無を検知するDLLクロック検知回路31とを備える。そして、DLLクロック検知回路31は、DLLクロックのクロッキング動作が検知されない場合に、遅延制御回路13による遅延量の更新制御を停止させる。

(もっと読む)

位相比較器、位相同期回路及び位相比較制御方法

【課題】入力断検出部を位相比較器に内蔵することで位相比較器を実装するPLL回路の小型化を図る。

【解決手段】参照信号を入力すると共に、参照信号に基づく被参照信号を帰還入力し、これら入力した参照信号及び被参照信号の立ち上がりエッジを検出し、参照信号の立ち上がりエッジ及び被参照信号の立ち上がりエッジ間の位相差を検出する位相差検出部21と、位相差検出部21にて検出した位相差に基づき、位相差を小さくすべく、定電流出力動作を実行する定電流出力部24と、被参照信号のエッジを検出した後、参照信号のエッジを検出する前に、被参照信号のエッジを再度検出した場合、参照信号の入力断として検出する入力断検出部23とを有している。

(もっと読む)

PLL回路

【課題】ディジタル回路で構成されるADPLLにおいて、位相差0近傍における位相差検出を改善することができる技術を提供する。

【解決手段】基準信号VREFフィードバック信号VDIVとの位相及び周波数を比較するPFDと、PFDの出力をディジタル値に変換するTDCと、TDCの出力から高周波雑音成分を除去するDLFと、DLFの出力に基づいて制御されるDCOと、DCOの出力を分周しフィードバック信号VDIVを出力するDIVによりフィードバックループが構成される。フィードバックループのいずれかの箇所にオフセット値が加算され、フィードバック信号VDIVの位相が制御され、ロック時にもTDCに0ではない値が入力される。

(もっと読む)

PLL回路

【課題】同期信号の位相が大きく変化する場合にも、短時間で位相を同期させる。

【解決手段】本PLL回路における位相比較器10は、映像信号に含まれる同期信号SYNと位相比較信号BLKとの位相誤差を示す比較出力信号PDPを出力し、VCO30は、比較出力信号PDPを積分するLPF20から与えられる直流電圧に応じた周波数のクロック信号CKを出力する。カウンタ40は、クロック信号CKを分周した位相比較信号BLKを出力する。ロック確認回路50は、位相比較信号BLKと同期信号SYNとの位相が同期すべきロック状態であるか否かを確認し、ロック状態でない場合にはリセット信号RSTを出力し、カウンタ40をリセットすることにより強制的にロック状態にすることができる。よって、短時間で位相を同期させることができる。

(もっと読む)

デジタル位相ロックループ(DPLL)における電力消費を制御するシステム及び方法

【解決手段】相異なる周波数クロックの組から選択された参照クロックを生成するように適合されたプログラマブル周波数デバイスを備えた装置であって、プログラマブル周波数デバイスは更に、相異なる周波数クロック間での切り替えの際に、参照クロックのトリガエッジの同じ時間的関係を維持するように適合される。装置は更に、入力信号と出力信号との間の所定の位相関係を確立するために選択された参照クロックを使用する、デジタルPLL(DPLL)のような位相ロックループを備える。相異なる周波数クロック間の切り替えの際に参照信号の同じ時間的関係を実質的に維持することで、参照クロックが変化しても、位相ロックループ(PLL)の連続且つ有効な動作は、大きくはディスターブされない。これは、装置の電力消費を制御するために使用され得る。 (もっと読む)

タイミングリカバリー回路

【課題】 構成を簡易にしたタイミングリカバリー回路を提供する。

【解決手段】 クロック入力信号に対するデータ入力信号の位相差を検出して位相差信号を出力すると共に異常時に異常信号を出力する位相比較器100と、VCXO109の制御電圧の中間値若しくはその付近の値の電圧が定電圧として供給され、平滑化された位相差信号と定電圧とを比較し、両信号の差分によりクロック入力信号に対するデータ入力信号の位相が進んでいる場合は位相を遅らせる制御電圧を、位相が遅れている場合は位相を進める制御電圧をVCXO109に出力するオペアンプ105と、オペアンプ105の位相差信号が入力される端子とVCXO109の入力端子との接続を制御し、異常信号によって接続をオンにするスイッチとを有するタイミングリカバリー回路である。

(もっと読む)

クロックデータリカバリ回路

【課題】本発明はクロックデータリカバリ回路に関し,受信データに同期したクロックを生成し,データのタイミングを調整し,ジッタ特性を改善することを目的とする。

【解決手段】入力データ変化を検出し,パルス生成するデータ変化パルス生成手段とこの信号を平滑化する第1ループフィルタと第2クロック信号の間の位相差信号を生成する位相差信号生成手段と,この信号を平滑化する第2ループフィルタと制御信号生成手段の信号を平滑化する第3ループフィルタと,第1及び第2ループフィルタの信号から制御信号を生成する制御信号生成手段と,位相差信号生成手段の信号に基づき第1クロック信号周期に応じた時間幅の第3クロック信号を供給する高周波ジッタ吸収用クロック生成手段と,第3ループフィルタからの信号の電圧レベルに応じて第1クロック周波数を可変供給する電圧制御発振手段で入力データに同期した第1クロック信号を再生するよう構成する。

(もっと読む)

デューティ検出回路およびCDR回路

【課題】入力データが交播パターン以外の場合であっても、高速かつ高精度にデューティを検出する。

【解決手段】デューティ検出回路は、入力データDinとこの入力データDinに周波数および位相が同期したクロックCKとを入力とし、入力データDinをクロックCKに同期してラッチして基準パルス幅を示すパルス信号Refを出力するフリップフロップ1と、入力データDinの平均電圧レベルとパルス信号Refの平均電圧レベルとの差を、入力データDinのデューティ100%からの変動分を示す検出信号Outとして出力する出力回路2とを備える。

(もっと読む)

CDR回路

【課題】製造のばらつきや環境変化あるいは入力データのパルス幅歪に対して強い耐性を持つCDR回路を提供する。

【解決手段】CDR回路は、入力データが遷移したときにパルスを出力するゲーティング回路2と、周波数制御信号に応じて発振周波数が制御されかつゲーティング回路2の出力パルスにより発振位相が制御される再生クロックを生成するゲーテッドVCO3と、入力データを遅延させる遅延回路4と、遅延回路4を通過した入力データのデータ識別を再生クロックに基づいて行うフリップフロップ1とを備える。遅延回路4は、ゲーティング回路2と同じ構成の遅延回路であるレプリカ回路40と、ゲーテッドVCO3と同じ構成の遅延回路であるレプリカ回路41とから構成される。

(もっと読む)

クロック信号分周回路および方法

【課題】大きな回路規模を必要とすることなく、有理数分周した出力クロック信号のサイクル時間変動を抑制するとともに、分周時に出力クロック信号の位相を調整する。

【解決手段】クロック選択制御回路100により、入力クロック信号のサイクルごとに、分周比に応じた一定サイクル時間を有する基準分周クロック信号と入力クロック信号との位相関係を示す位相計算値111を計算するとともに、位相調整信号に応じてその値を増減し、この位相計算値111に基づいて、出力動作のうち、基準分周クロック信号の位相と近いクロック信号を生成するための出力動作を指示する制御信号102,103を生成する。クロック選択回路101により、制御信号102,103に基づいて、入力クロック信号のクロックパルスをそのまま非反転で出力するか、反転して出力するか、マスクして出力しないか、のいずれかの出力動作を選択して実行することにより、出力クロック信号を生成する。

(もっと読む)

信号再生回路

【課題】受信マージンを拡大可能な信号再生回路を提供する。

【解決手段】例えば、クロック信号CLKa,CLKb,CLKcを生成するクロック生成部CLK_GENと、CLKaとCLKbの間、又はCLKbとCLKcの間にデータ信号Diのエッジが入り込んだ際に、位相検出信号(EARLY,LATE)を生成するクロック・データ判定部CD_JGEと、ウインドウ幅制御部WW_CTL等を設ける。CLK_GENは、この位相検出信号に基づいて、前述したDiのエッジが入り込まないように、CLKa,CLKb,CLKcの全体位相を互いの位相差を保ったままで制御すると共に、WW_CTLからの信号(Sww)に基づいて、CLKaとCLKbの位相差、およびCLKbとCLKcの位相差を制御する。

(もっと読む)

位相検出装置、位相比較装置およびクロック同期装置

【課題】クロック同期システムに用いる位相比較器として、次段のカウンタに影響を与えることなく、クロックの同期がとれた際に確実にロックをかけること。

【解決手段】本発明は、基準クロックの位相に対する比較クロックの位相のずれを検出する第1の位相比較部K1aと、基準クロックおよび比較クロックのいずれか一方について所定時間遅延または進んだ状態での両クロックの位相のずれを検出する第2の位相比較部K1bと、第1の位相比較部K1aの出力と第2の位相比較部K1bの出力との論理積を位相ずれの検出結果として出力する論理積部AND1とを備える

(もっと読む)

半導体集積回路装置および逓倍クロック生成方法

【課題】 エージング時に使用可能な同期逓倍クロック発生回路を提供することである。

【解決手段】 可変ディレイヤを用いた発振回路と、カウンタを用いた発振周波数制御回路とを有し、入力クロック周波数の逓倍の周波数のクロックを発生するクロック発生回路において、上記発振回路を入力クロックに同期させて動作させることで、入力クロックと同期した逓倍クロックを発生させる。

(もっと読む)

位相同期装置

【課題】本発明は、短いロッキングタイムを有しながらも、安定的に動作できる位相同期装置を提供する。

【解決手段】本発明の位相同期装置は、入力クロックを所定の分周比で分周した後、順次遅延させる動作により周波数を判別し、前記判別された周波数情報を用いて発振器ゲイン設定信号を生成する発振器ゲイン設定手段と、前記入力クロックに応じて、前記発振器ゲイン設定信号に対応する周波数を有する出力クロックを発振させるPLL回路を含むことを特徴とする。

(もっと読む)

発振周波数制御回路、その発振周波数制御回路を有するDC−DCコンバータ及び半導体装置

【課題】マイコン等の特別な制御回路が不要で、しかも無線送受信回路で使用する周波数に関係なく、スイッチングノイズの影響を無視できるレベルまでスイッチングノイズを軽減することができる発振周波数制御回路、その発振周波数制御回路を有するDC−DCコンバータ及び半導体装置を得る。

【解決手段】アップ/ダウン制御回路11は、第1クロック信号CLKAと第1分周クロック信号CLKB1との周波数を比較する第1周波数比較回路12と、第1クロック信号CLKAと第2分周クロック信号CLKB2との周波数を比較する第2周波数比較回路13の各出力信号UP及びDOWNに応じて、第2クロック信号CLKB2の周波数が所定の下限値から所定の上限値の間を連続的に変化しながら往復するように、発振回路2に対して、第2クロック信号CLKBの周波数制御を行うようにした。

(もっと読む)

クロック発振回路

【課題】簡単な回路構成でスペクトラム拡散を行うことが可能なクロック発振回路を提供する。

【解決手段】基本クロック信号を発振する基本クロック発振器と、基本クロック信号と非同期で、かつ基本クロック信号より短い周期としたクロック調整信号を発振する調整クロック発振器と、基本クロック信号をクロック調整信号の1周期分シフトして、クロックシフト信号として出力するシフト回路23cと、基本クロック信号およびクロックシフト信号を1周期ごとに切り替えて、調整クロック信号として出力する切替回路として機能するカウンタ回路23aおよびセレクタ回路23bとを備えている。シフト回路23cは、基本クロック信号をクロック調整信号の立ち上がりで同期する第2フリップフロップ23c1で形成され、カウンタ回路23aは、基本クロック信号を2分周する第1フリップフロップ23a1および第1インバータ23a2で形成されている。

(もっと読む)

周波数制御回路およびCDR回路

【課題】調整のための外部接続端子を必要とする部品や外部接続部品を必要とする部品を不要にする。

【解決手段】CDR回路は、周波数制御回路と、制御電圧に応じて発振周波数が制御されかつ入力データにより発振位相が制御される再生クロックを生成する第1のVCO2と、再生クロックによって入力データのデータ識別を行うFF1と、制御電圧に応じて発振周波数が制御される第2のVCO3とを備える。周波数制御回路は、第2のVCO3の出力信号の周波数を参照クロックの周波数と比較し、検出した周波数差に応じた信号を出力する周波数比較器4と、周波数比較器4の出力信号に応じて出力するデジタル値を上下させるアップダウンカウンタ5と、アップダウンカウンタ5の出力をアナログ信号に変換してVCO2,3の制御電圧として出力するD/A変換器6とから構成される。

(もっと読む)

PLL回路、無線端末装置、および周波数検出方法

【課題】DCOの最低発振周波数を検出し、分周比Nに比例した制御データから、DCOの制御データへの変換を精度良く行うことが可能な、新規かつ改良されたPLL回路を提供すること。

【解決手段】ディジタル値を用いて制御される発振回路を有するPLL回路であって、搬送波周波数値を設定する搬送波周波数設定部と、搬送波周波数値が変化したことを検出する検出部と、搬送波周波数値が変化したことを示す信号に同期して、発振回路を最低周波数で発振させるための制御信号を送信し、基準周波数の1周期内の発振回路の出力クロック数を計測する計測部と、を含むことを特徴とする、PLL回路が提供される。

(もっと読む)

同期クロック生成回路及び同期クロック生成回路を備えたアナログ/ディジタル角度変換器と角度検出装置

【課題】安価に構成することができる同期クロック生成回路を提供する。

【解決手段】角度検出器10の出力する2相の角度信号S1とS2を、第1二乗回路11と第2二乗回路12でそれぞれ二乗し、それぞれの二乗信号を加算回路14で加算し、加算回路14の出力信号の直流成分をフィルタ16で除去する。フィルタ16の出力信号と基準電位とを比較するコンパレータ18で矩形波に変換し、その矩形波の位相を移相器20で所定量遅らせる。移相器20の出力信号を、同期化分周回路22で角度検出器10に供給する励磁信号に同期して1/2分周して同期クロックSQ3を得る。

(もっと読む)

141 - 160 / 296

[ Back to top ]