Fターム[5J106DD48]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | デジタル回路 (2,545) | 論理回路 (611) | フリップフロップ (296)

Fターム[5J106DD48]に分類される特許

161 - 180 / 296

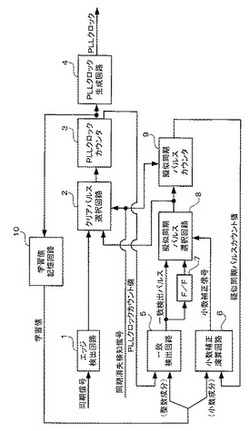

デジタルPLL回路

【課題】同期信号消失時の同期維持精度が向上されるとともに簡素な回路構成のデジタルPLL回路を提供することである。

【解決手段】同期信号の入力があるときの2つのクリアパルスの間に含まれる内部クロックの数の時系列的な平均値を学習値として記憶する学習値記憶回路と、PLLクロックカウンタのカウント値が学習値の整数成分と一致したとき一致検出パルスを生成する一致検出回路と、一致検出パルスを内部クロックの1周期分遅延して遅延パルスを生成するフリップフロップと、一致検出パルスまたは遅延パルスのいずれか一方を小数補正信号に従って選択し擬似同期パルスとして出力する擬似同期パルス選択回路と、補正区間において遅延パルスの数の擬似同期パルスの数に対する割合が学習値の小数成分に近似するよう選択する小数補正信号を出力する小数補正演算回路と、を有する。

(もっと読む)

位相比較器及び測定装置

【課題】2つの信号の位相比較結果を確実に保持できる位相比較器を提供する。

【解決手段】2つの信号CMP、REFの位相を比較して、その位相関係を出力する比較部10と、比較部より出力される位相比較結果を入力信号として受信し信号OUTとして出力するホールド回路30と、比較部の出力に基づいて位相比較結果が確定したか否かを判定し、位相比較結果が確定したと判定した場合にホールド信号Cを出力するホールド信号生成部20とを備え、ホールド回路は、ホールド信号が出力されている期間は前記入力信号を保持するようにして、比較部による位相比較結果が確定する前に状態が保持されることを防止し、位相比較結果を確実に保持できるようにする。

(もっと読む)

発振周波数制御回路、その発振周波数制御回路を有するDC−DCコンバータ及び半導体装置

【課題】デジタルオーディオ回路で使用する第1クロック信号CLKAとDC−DCコンバータで使用する第2クロック信号CLKBとの周波数差によって生ずる可聴周波数帯域のノイズ信号を除去することができる発振周波数制御回路、その発振周波数制御回路を有するDC−DCコンバータ及び半導体装置を得る。

【解決手段】発振周波数制御回路23は、第1クロック信号CLKAの第1周波数FAと第2クロック信号CLKBの第2周波数FBとの差が可聴周波数帯域に入ると、第2発振回路21に対して、該帯域に留まらないように第2周波数FBを変化させるようにし、第2周波数FBが可聴周波数帯域に入った場合は、第2発振回路21に対して、第2周波数FBを上昇させて最大可聴周波数以下にならないようにした。

(もっと読む)

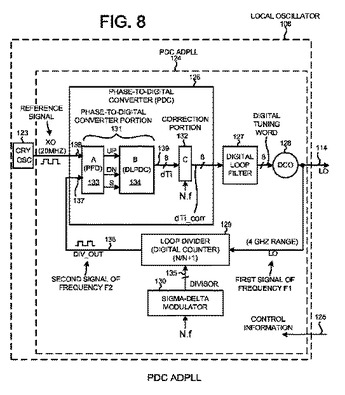

自己訂正する位相デジタル伝達関数を有する位相ロックループ

位相ロックループは、位相デジタル変換器部分、ならびに新規訂正部分を含む。位相デジタル変換器(PDC)部分は、第1の位相誤差ワードのストリームを出力する。新規訂正部分は、第1の位相誤差ワードを受け取り、そしてループフィルタへと供給される第2の位相誤差ワードのストリームを生成する。PDC部分は、ある種の不完全性を示す位相デジタル伝達関数を有する。第1の例においては、訂正部分は、第1の位相誤差ワードの対の間の平均差を決定し、そして遅延要素伝搬遅延の変化に起因したPDC部分の伝達関数の傾斜における変化について訂正するために第1の位相誤差ワードを正規化するためにこの平均差を使用する。第2の例においては、訂正部分は、PDC部分の伝達関数における利得ミスマッチについて訂正する。第3の例においては、訂正部分は、PDC部分の伝達関数におけるオフセットミスマッチについて訂正する。  (もっと読む)

(もっと読む)

ゲート時間/デジタル変換器を有するデジタル位相ロックドループ

デジタルPLL(DPLL)、時間/デジタル変換器(TDC)および制御ユニットを含む。TDCは、位相情報を量子化するために、短い時間の間、周期的に有効され、電力消費を削減するために、残り時間の間、無効にされる。TDCは、第1のクロック信号と第1の基準信号を受信し、第1のクロック信号と第1の基準信号との位相差を示す出力をTDCに提供する。制御ユニットは、主基準信号に基づいてイネーブル信号を生成し、イネーブル信号でTDCを有効および無効にする。ある設計において、制御ユニットは、第1の基準信号および第2の基準信号を獲得するために、主基準信号を遅らせ、主基準信号および第2の基準信号に基づいてイネーブル信号を生成し、TDCに対する第1のクロック信号を獲得するために、イネーブル信号で主クロック信号をゲートする。 (もっと読む)

PLL回路

【課題】ハイブリッド制御方式PLL回路の定常状態における位相ジッタを低減する。

【解決手段】ハイブリッド制御方式PLL回路内の位相比較回路PHASE_COMPの出力S_PHが頻繁に変化しているか否かを判定する定常状態検出回路CONV_DETを設け、位相比較回路の出力S_PHが暫く変化していない時は定常状態に達していないと判定し、頻繁に変化している時は定常状態に達したと判定し、その判定結果に基づいて、電圧制御発振回路VCOの発振周波数をデジタル制御信号S_DGによって制御する制御幅を変更し、もしくは(および)、アナログ制御信号S_AGを変化させる頻度を変更する。これにより、定常状態に達する前の収束性を損なうことなく、定常状態に達した後のデジタル制御信号による発振周波数の制御幅を小さくできる。よって、定常状態における位相ジッタを低減できる。

(もっと読む)

信号生成回路

【課題】基準クロックの周期より細かい周期で制御された複数の出力信号を出力する信号生成回路を提供する。

【解決手段】本発明にかかる信号生成回路は、基準クロックを出力する状態と、基準クロックに基準クロックの1周期より短い第1時間の遅延を持たせた信号を出力する状態と、を切り換え可能な入力段遅延回路10と、入力段遅延回路10の出力が変化した時点から入力段遅延回路10の出力を基準クロックの1周期より短い第2時間保持するゲート回路33を有し、ゲート回路33の出力に対応する信号を出力する制御部30と、制御部30の出力信号に第2時間の遅延を持たせた信号を出力する出力段遅延回路20と、を備え、入力段遅延回路10は、制御部30の出力信号の変化に応答して出力状態の切り換えを行う。

(もっと読む)

注入同期型発振器

【課題】より小型化が可能な周波数逓倍器を提供する。

【解決手段】注入同期型発振器20は、インバータ(22a、22b、22c)を3段リング状に接続してリングオシレータを備えている。そして、2段目のインバータ22bの出力と、3段目のインバータ22cの出力とをnMOSトランジスタ24で接続する構成を採用している。このnMOSトランジスタ24のゲートは、外部から基準周波数信号が供給される。このような構成によって、、リングオシレータの自励発振周波数に近い周波数であって、注入された基準周波数信号と同期した整数倍の周波数で発振が行われる。このように、インジェクションロックを用いて、位相雑音を減らすことができるので、ループフィルタを必要とせず、より小面積で周波数逓倍器を構成することが可能である。

(もっと読む)

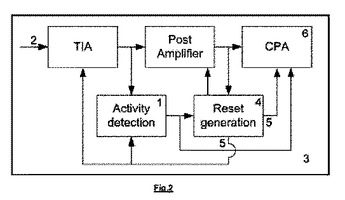

TDMAネットワークにおける信号検出のための装置及び方法

本発明は、バーストモード受信機における動作状態を検出するための回路(1)に関する。本回路は、プリアンブルを含む入力信号(2)を受けるように構成される。本回路は、入力信号(2)における信号遷移を検出する微分器(11)を備え、微分器(11)を動作させる情報をそのプリアンブルが含む。好ましい実施形態において、上記情報は時定数である。本回路は、微分器の出力が供給されるように構成された積分器(12)をさらに備える。結果として得られる信号は基準(16)に対して比較される。この基準と交差するとき、動作状態が検出される。ある実施形態ではフロントエンド回路が提供され、フロントエンド回路は、動作状態を検出する回路の後段に、フロントエンド回路をリセットするように構成されたリセット回路と、位相を復元するように構成されたクロック位相アラインメント回路を備える。  (もっと読む)

(もっと読む)

PLL回路及び無線通信システム

【課題】複数の発振周波数帯域を有するVCOを備えたPLL回路において、設定されたPLL出力周波数に対応する最適な発振周波数帯域の検出動作に要する時間を短縮する。

【解決手段】TDC回路30は、固定分周器2からの所定の基準信号11の立ち上がり時に、その基準信号11と可変分周器7のPLL分周信号15との位相差を求め、更に、前記基準信号の次の立ち上がり時においても同様に、その基準信号とPLL分周信号15との位相差を求める。その求めた2つの位相差情報により、基準信号11の1周期の間にPLL分周信号15が基準信号11に対して進んだ又は遅れた位相量を検出して、基準信号11とPLL分周信号15との周波数の高低を検出する。よって、1つの発振周波数帯域に対して、基準信号11の1周期で周波数比較を完了でき、発振周波数帯域選択回路8は、設定されたPLL出力周波数に対応する最適な発振周波数帯域を短時間で検出する。

(もっと読む)

PLL回路

【課題】簡単に暴走状態から正常動作に復帰可能なPLL回路を提供する。

【解決手段】比較部140により制御電圧Vcntlが上限電圧値Vref1を超えたことが検出されると、指示信号切替部150は制御電圧Vcntlを強制的に下降させる他の指示信号(グランド電圧を指示信号Vu2、電源電圧を指示信号Vd2)を制御電圧生成部130に供給し、制御電圧生成部130は制御電圧Vcntlを下降させる。そして、比較部141により制御電圧Vcntlが下限電圧値Vref2を下回ったことが検出されると、指示信号切替部150は制御電圧生成部130への供給を他の指示信号から位相比較器からの指示信号(アップ信号Vu1、ダウン信号Vd1)に切り替え、制御電圧生成部130は指示信号に応じて制御電圧Vcntlを生成する。電圧制御発振回路110は、制御電圧Vcntlに応じて発振周波数を制御する。

(もっと読む)

フェーズロックドループ回路

【課題】入力される水平同期信号に対して、サンプリングクロックの周期の値に制約されることなく、位相誤差量を低減することができるフェーズロックドループ回路を提供する。

【解決手段】入力される水平同期信号(H-sync)は、逓倍PLL回路2から出力される、周期が等しく、1/4周期分づつずれた位相関係の4種の第1〜第4サンプリングクロックによりサンプリング回路でそれぞれサンプリングされ、各サンプリングクロックに位相同期した4種の水平同期出力データが生成され、これらはさらに加算回路6で加算されて加算水平同期出力データが生成された後、位相比較器13に入力され、分周器14で分周されたシステムクロック(第1サンプリングクロック)と位相比較される。

(もっと読む)

データリカバリ方法およびデータリカバリ回路

【課題】入力データのジッタの影響を簡単な構成で低減でき、データを正確に復元できるデータリカバリ方法およびデータリカバリ回路を提供すること。

【解決手段】入力データから位相データを検出する選択信号生成部を備え、選択信号生成部が検出した位相データに基づいて入力データをサンプリングするデータリカバリ回路において、選択信号生成部は、入力データの位相と検出済みの位相データが表す位相との位相差を検出する位相差検出部530a〜530dと、位相差の絶対値が位相補正用規定値を超える場合に、位相差の絶対値が位相補正用規定値にクリップするよう位相データを補正するクリップ回路531a〜531dとを備える。

(もっと読む)

タイミング制御回路及び半導体記憶装置

【課題】プロセスや動作環境等の変化に対して、遅延変動の小さいタイミングを生成しアクセス時間を短縮可能とする、タイミング制御回路及び該タイミング制御回路を備えた半導体記憶装置を提供する。

【解決手段】周期T1を持つ第1のクロック信号と、周期T2の第2のクロック群(CKb)が入力され、疎調遅延回路(CD)と微調遅延回路(FD)を備え、疎調遅延回路(CD)は活性化信号の活性化から第1のクロック信号の立ち上がりエッジをカウントするカウンタを有し、第1のクロック信号からの遅延量がほぼm・T1である疎調タイミング信号(CT)を生成し、微調遅延回路(FD)はL個の並列した多相クロック制御遅延回路からなり、それぞれL相の第2のクロック群による疎調タイミング信号(CT)のサンプリングのタイミングをn・(T2/L)だけ遅延させ、遅延されたパルスのORをとることで微調タイミング信号(FT)とする。

(もっと読む)

位相調整装置

【課題】設計時以降に生じる位相差の変動を内部で自動的に調整することで、予め設定された位相差を有する2つの信号を出力する。

【解決手段】2つのクロック信号の位相差を予め定められた位相差に調整する位相調整装置であって、第1クロック信号に対する第2クロック信号の遅延量を選択的に変更可能な遅延部11と、前記遅延量を制御する制御部12とを備え、前記制御部12は、準備モードにおいて、前記遅延量を第1の時間間隔で段階的に増加又は減少させ、遅れ期間、又は、進み期間を検出し、調整モードにおいて、前記遅れ期間又は前記進み期間と同じ長さの期間において第2の時間間隔で前記遅延量を段階的に変化させることで、前記第2クロック信号の位相差を予め定められた位相差に調整し、前記第2の時間間隔と前記第1の時間間隔との比は、180度と予め定められた位相差との比に等しい。

(もっと読む)

PLLシンセサイザー回路

【課題】 電源変動等が生じると、外部からの割込信号により不定期間を待って再度分周データをPLLシンセサイザーICに書き込むことで、安定的にロック状態に復帰させることができるPLLシンセサイザー回路を提供する。

【解決手段】 PLLシンセサイザーIC106の電源投入時又は電源変動時にマイクロプロセッサ(CPU)104への割込を監視手段が発生させ、CPU104はPLLシンセサイザーIC106の電源投入後又は電源変動後の不定期間に相当する期間を待って、分周データをPLLシンセサイザーIC106に出力して書き込みを行い、更に分周データ出力後にロック状態となるまでの期間ウエイトするPLLシンセサイザー回路である。

(もっと読む)

半導体集積回路

【課題】ロック動作の初期において高速引き込みを可能とすると伴に入力信号ジッタや入力雑音の影響の小さなディジタルフェーズロックドループを提供すること。

【解決手段】半導体集積回路は、位相比較器10、11、ディジタルループフィルタ12、ディジタル制御発振器13、フィードバック分周器14を含むディジタルフェーズロックドループADPLLを具備する。ディジタルループフィルタ12は、第1ゲインαを有して位相比較器10、11のディジタル位相出力信号θが供給される比例パス12aと、第2ゲインβを有して信号θが供給される積分パス12b、12c、12dと、信号θの大きさを判定する判定器12g、12hを含む。ディジタル位相出力信号θの大きさが所定の基準値θthよりも大きい場合には、判定器12g、12hは第2ゲインβと第1ゲインαとの比β/αを大に設定する。

(もっと読む)

従属同期クロック信号生成装置

【課題】従属同期クロック信号生成装置に関し、従属同期用クロック信号の系切替え時に瞬断なくクロック信号を供給し、擾乱の無い装置供給用クロック信号を供給する。

【解決手段】外部から2系統の従属同期クロック信号を入力し、該従属同期クロック信号の1周期分の信号の開始部分を検出してハイレベル信号を出力し、該従属同期クロック信号の1周期未満のタイミングでローレベル信号を出力する2系統のクロック信号生成部(#0)1−1,(#1)1−2と、該クロック信号生成部から出力される信号の論理和信号をクロック信号としてPLO部6−7出力する論理和信号出力部1−3を備える。クロック信号生成部は、内部自走クロック源1−4のクロックをカウントして従属同期クロック信号の1周期未満のタイミングでローレベル信号をフリップフロップ回路1−12,1−22のリセット端子に入力して強制的にローレベル信号を出力させる。

(もっと読む)

クロック生成回路、記録装置及びクロック生成方法

【課題】入力信号の欠落により発生する出力クロック信号のずれを適切に補正しつつ、入力信号に同期した出力クロック信号を生成することができるクロック生成回路を提供する。

【解決手段】所定の周波数を有する入力信号を所定の逓倍比で逓倍して出力クロック信号を生成するクロック生成回路10を提供する。このクロック生成回路10は、入力信号を逓倍して出力クロック信号を生成するPLL回路100と、PLL回路100の逓倍比を変更する補正回路200と、を備え、補正回路200は、入力信号に同期した入力同期信号と出力クロック信号に同期した出力同期信号との時間差が減少するにように、入力信号の1周期より長い補正周期毎の補正区間においてのみPLL回路100の逓倍比を所定の逓倍比から当該所定の逓倍比を増加又は減少した逓倍比に変更し、PLL回路100は、補正区間において、変更された逓倍比で入力信号を逓倍する。

(もっと読む)

可変タイミングメモリ

【課題】同期回路装置の設計に於いて、タイミング最適化の作業工程を削減化する。

【解決手段】同期回路装置10内の可変タイミングメモリ20のモジュールは、メモリアレイ21とその入出力メモリ制御回路22,23に加えて、クロック端子Tに入力したクロック信号CLKを遅延する信号線24と、クロック信号CLKをそのまま伝送する信号線25と、両信号線24,25を入力とするセレクタSL1と、メモリライト/リード信号が印加され且つセレクタSL1のセレクト端子と繋がったタイミングモード端子TMTとを有する。セレクタSL1は、メモリライト信号の受信に応じて信号線24を選択し、遅延されたクロック信号を入出力メモリ制御回路22,23に印加する。他方、メモリリード信号の受信に応じてセレクタSL1は信号線25を選択し、クロック信号CLKをそのまま入出力メモリ制御回路22,23に印加する。

(もっと読む)

161 - 180 / 296

[ Back to top ]