Fターム[5J106FF01]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 入出力、ループ構成 (832) | 複数入力 (24)

Fターム[5J106FF01]に分類される特許

1 - 20 / 24

マイクロコントローラー

【課題】誤動作を確実に防止する。

【解決手段】クロック信号が供給されて動作する演算回路と、第1クロック信号を生成する発振回路と、基準クロックに基づいて第2クロック信号を生成するPLL回路と、第2クロック信号の異常を検出する異常検出回路と、第1クロック信号と第2クロック信号のいずれかを選択して演算回路に供給する選択回路であって、電源起動時には第1クロック信号を選択し、異常検出回路で異常が検出されない場合には、ファームウェアの設定に応じて第1クロック信号から第2クロック信号に切り換え、異常検出回路で異常が検出された場合には、ファームウェアの設定に関わらずに、第1クロック信号から第2クロック信号への切り換えを行わない選択回路と、異常検出回路で異常が検出された場合に、第1クロック信号から第2クロック信号への切り換えが行われなかったことを演算回路に知らせるステータスレジスタと、を備える。

(もっと読む)

デューティ補正付き位相調整回路及びシリアライザ

【課題】クロックのばらつきが引き起こすジッタを抑制することが可能なデューティ補正付き位相調整回路及びシリアライザを提供することを目的としている。

【解決手段】正クロック信号及び負クロック信号が入力され前記正クロック信号と前記負クロック信号のデューティ及び位相を調整した正クロック出力信号及び負クロック出力信号を出力する。

(もっと読む)

信号伝搬遅延を補償するための装置及び方法

【課題】1以上の伝送接続上の電気信号など、1以上の信号の伝搬遅延または時間を補償する装置及び方法を提供し、実装のための複雑な演算手段を必要とせず、自動的に伝搬時間の補償を行なうことを可能とする。

【解決手段】第1伝送接続(104)の第1端(106)と第2端(108)の間を伝搬中に第1周期信号ref(t)が受ける遅延τを補償するための装置(100)であり、前記第1信号ref(t)に対応し、その位相が遅延τに等しい時間により位相前進された第2信号ref(t+τ)を生成可能な第1手段(114)と、前記第1伝送接続の前記第2端で取得され前記第1信号ref(t)に対応し、その位相が遅延τにより遅延された第3信号ref(t-τ)と、前記第2信号ref(t+τ)とから、前記第1信号ref(t)と同位相である第4信号を生成可能な第2手段(116)とを少なくとも備える。

(もっと読む)

クロック発生回路

【課題】 PLLを動作させた状態で、同期外れを起させず、入力クロックの切り替えおよびそれに伴う分周比の切り替えを行うことが可能なクロック発生回路を提供する。

【解決手段】 タイミング制御部8は、入力クロックを指定するクロック選択情報が切り替わった後、分周器1がリファレンスクロックCLKREFを出力するのに応じて、クロック選択指令SELCKを切り替える動作と、分周器1に1個のリファレンスクロックCLKREFを出力させるための入力クロックの個数Rと、分周器6に1個のフィードバッククロックCLKFBを出力させるための出力クロックCLKOの個数Fのうちの少なくとも一方の設定を切り替え、切り替え後の設定個数Rに対応した入力クロックの分周器1によるカウント動作および切り替え後の設定個数Fに対応した出力クロックの分周器6によるカウント動作の両方を開始させる。

(もっと読む)

位相調整回路及び位相調整方法

【課題】消費電力を低減し、かつ回路面積も小さい位相調整回路を提供すること

【解決手段】位相調整回路100は、複数の遅延素子回路121〜124をリング状に結合したVCO120を有するPLL発振回路100を備える。また位相調整回路100は遅延素子回路を所望の遅延量に応じた数(125〜127)だけ有し、入力信号に前記所望の遅延量を与える位相遅延回路200、210を備える。PLL発振回路100は基準クロックの入力に応じた基準信号に、基準信号の所定周期分の遅延を与えた発振信号をVCO120において生成する。PLL発振回路100は、基準信号と、発振信号に応じた信号と、が略同位相となるように算出された遅延量に応じた遅延制御信号を遅延素子回路121〜124、及び遅延素子回路125〜127の各々に対して入力する。

(もっと読む)

半導体集積回路

【課題】チップ面積の更なる縮小化を図ることができる半導体集積回路を提供する。

【解決手段】ディジタル制御発振器50−1〜50−nと、位相データ出力部100−1〜100−nと、積分処理部150と、フィルタ部151と、フィルタ部151からの時分割された出力信号に所定の係数を乗算した値を発振器制御値OTWとして出力する乗算器(第1の乗算器)40と、リファレンス周波数Frefに同期して、発振器制御値OTWを各ディジタル制御発振器50−1〜50−nに振り分ける出力セレクタ(制御値分離部)42と、を備える。

(もっと読む)

基準信号発生装置及び方法

【課題】 GPS信号の受信障害が発生しても、内蔵オシレータよりも高い周波数安定度の基準信号を発生することと、受信障害の発生前後で連続性の高い基準信号を出力することとを両立した基準信号発生装置を提供する。

【解決手段】 GPS受信機にて取得したGPS受信時刻と、そのGPS受信時刻の直前或いはその直後に標準電波受信機にて取得した標準電波受信時刻との時刻差を、予め定められた時間間隔毎に算出し、算出した時刻差と日時とを関連づけた時刻差データベースを構築する。GPS受信障害の発生を未検出のときGPS受信時刻に基づいて電圧制御発振器を制御して基準信号を発生し、GPS受信障害の発生を検出中は、時刻差データベースから取得した現在の日時に対応する時刻差に基づいて標準電波受信時刻を補正して電圧制御発振器を制御して基準信号を発生する。

(もっと読む)

信号受信装置、信号受信装置の制御方法及びコンピュータプログラム

【課題】1つの位相比較器及びループフィルタを複数の同期保持チャネルで共有することで、同期保持チャネルの増加に伴う回路規模の増大を抑えることが可能な信号受信装置を提供すること。

【解決手段】所定の周波数のキャリアを生成する信号生成器を含む位相同期ループ部と、衛星から受信した信号のキャリアと信号生成器が生成したキャリアとの位相差を検出して出力する1以上の位相比較器と、位相比較器が出力する位相差情報からノイズを除去して所望のループの応答を実現する1以上のループフィルタと、を備え、同時に追跡可能な最大衛星数N(Nは2以上)に対して、位相比較器及びループフィルタの数MはN>Mである、信号受信装置が提供される。

(もっと読む)

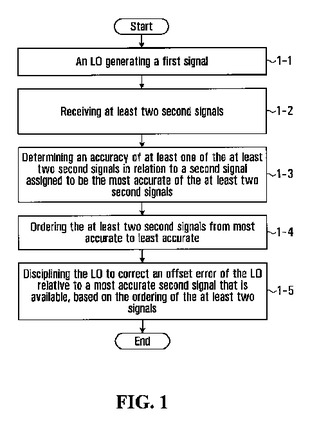

局部発振器を調整する装置及び方法

装置は、タイミング情報、周波数情報、位相情報及びそれらの組み合わせの内の少なくとも1つを有する第1信号を生成する局部発振器(LO)と、少なくとも2つの入力を有する優先制御部とを有し、入力の各々は、タイミング情報、周波数情報、位相情報及びそれらの組み合わせの内の少なくとも1つを有する第2信号をそれぞれ受信し、優先制御部は、少なくとも2つの第2信号の内の少なくとも1つの第2信号の精度を判定し、何れかの第2信号は少なくとも2つの第2信号の内で精度が最高であるように指定され、優先制御部は、最高精度から最低精度へ少なくとも2つの第2信号を順番に並べ、少なくとも2つの第2信号の順番に基づいて、装置に利用可能な最高精度の第2信号に対してLOのオフセットエラーを補正するように、LOが調整される。  (もっと読む)

(もっと読む)

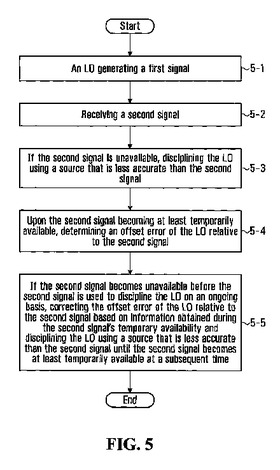

局部発振器を調整する装置及び方法

装置は、タイミング情報、周波数情報、位相情報及びそれらの組み合わせの内の少なくとも1つを有する第1信号を生成する局部発振器(LO)と、タイミング情報、周波数情報、位相情報及びそれらの組み合わせの内の少なくとも1つを有する第2信号を受信する入力を有するLOエラー補正部とを有し、第2信号はLOを調整するために使用され、LOエラー補正部は、第2信号がLOを調整するために利用可能でなくなった場合に、第2信号より精度が低いソースを用いてLOを調整し、第2信号が少なくとも一次的に利用可能になった場合に、第2信号に対するLOのオフセットエラーを判定し、当該装置が継続的にLOを調整するために第2信号を利用する前に、第2信号が利用可能でなくなった場合、第2信号が一次的に利用可能であった期間内に取得された情報に基づいて、第2信号に対するLOのオフセットエラーを補正し、第2信号が以後に少なくとも一次的に利用可能になるまで、第2信号よりも精度が低いソースを用いてLOを調整する。  (もっと読む)

(もっと読む)

半導体装置

【課題】リード動作時における位相調整精度を低下させることなく、DLL回路の消費電力を低減する。

【解決手段】ODT機能を有するデータ入出力回路80と、データ入出力回路80の動作タイミングを規定する内部クロックLCLKを生成するDLL回路100とを備える。DLL回路100は、内部クロックLCLKを高精度に位相制御する第1のモードと、低消費電力で動作する第2のモードとを有し、データ入出力回路80がODT動作を行っていない場合には第1のモードで動作し、データ入出力回路80がODT動作を行っている場合には第2のモードで動作する。このように、ODT動作の有無によってDLL回路100の動作モードを切り替えていることから、厳密な位相制御が不要なODT動作時における消費電力を低減することが可能となる。

(もっと読む)

基準周波数発生装置及び基準周波数発生システム

【課題】冗長化された基準周波数発生システムにおいて、現用側と予備側での出力切替時に出力信号のタイミングが急激に変動するのを防止する。

【解決手段】現用側の基準周波数発生装置51においては、自機のGPS受信機21aが生成する1PPS信号がPLL回路22aに供給される。予備側の基準周波数発生装置52においては、現用側の基準周波数発生装置51のPLL回路22aから出力された1Hzの信号が、第1伝送経路を経由してPLL回路22bに供給される。予備側に入力された1Hzの信号は、前記第1伝送経路と遅延量が等しい第2伝送経路を経由して現用側に戻される。現用側の基準周波数発生装置51は、自機のPLL回路22aからの1Hzの信号と、予備側に出力して戻された1Hzの信号と、の時間差に基づき補正用信号を出力する。予備側の基準周波数発生装置52は、補正用信号に基づいて、PLL回路22bの出力信号の位相を調整する。

(もっと読む)

マルチチャネル・データ検出システム用に構成された周波数エラー組み合わせ論理および周波数エラーを生成するための方法

【課題】 各チャネル用のフェーズ・ロック・ループを有するマルチチャネル・データ検出システムの周波数エラー組み合わせ論理を提供することにある。

【解決手段】 この周波数エラー組み合わせ論理は、各チャネルに関する周波数エラー情報を受信することと、受信周波数エラー情報を結合し、結合された位相エラーを生成し、各チャネルからの受信周波数エラー情報に重みを付けるように構成された組み合わせ論理と、結合された周波数エラーを少なくとも1つのチャネル・フェーズ・ロック・ループに適用するように構成された周波数エラー出力とを含む。

(もっと読む)

クロック信号生成回路とクロック信号生成方法

【課題】複数系統の基準信号のいずれか、又は全てが断となってしまった場合でも、安定してクロック信号を生成することができるようにする。

【解決手段】断検出部2−A,2−Bで現用系の基準信号Aと予備系の基準信号Bの断を検出するようにし、断検出時には断検出信号を制御部8へ出力する。制御部8は、断検出部2−Aからの断検出信号を受け取ると、入力切替部1の導出を基準信号Bに切り替え、その後、断検出部2−Bからの断検出信号を通知されると、制御電圧保持部6の保持電圧の更新を停止させ、切替部7の導出を制御電圧生成部5で生成される制御電圧から制御電圧保持部6に保持される保持電圧に切り替える。

(もっと読む)

半導体集積回路装置

【課題】製造プロセスなどに依存することなく、安定した高精度なサンプリングクロックを生成する。

【解決手段】遅延段検出回路14は、位相検出部13の位相検出結果から、デジタル可変遅延ライン12の出力信号が基本クロックCLKrefから1周期遅延するバッファの遅延段数を検出する。遅延段数選定部21は、遅延段検出回路14が検出した最新の検出結果と過去の任意の回数分の検出結果との差を算出し、設定された遅延段数以下の際に最新の検出結果を出力する。位相/遅延段数変換部15は、入力された位相遅延の設定信号と使用検出遅延段数保持部22の遅延段数のデータとから、位相遅延に必要なバッファの遅延段数を算出し、遅延設定データとして算出し、デジタル可変遅延ライン111 〜11n は、遅延設定データに基づいて遅延したサンプリング信号を生成する。

(もっと読む)

クロック供給装置

【課題】上位からのクロックに位相同期したクロックを供給するクロック供給装置に関し、現用系と予備系とのクロックの位相を一致させる。

【解決手段】システムクロックに位相同期した現用系クロックを出力する現用系システムクロック供給装置1aと予備系クロックを出力する予備系システムクロック供給装置1bとを有し、システムクロックに位相同期したクロックを出力するDPLL部2a,2bと、このDPLL部2a,2bからのクロックを遅延制御する可変遅延回路4a,4bと、この可変遅延回路4a,4bを介して出力する現用系クロックと予備系クロックとの位相を比較する位相比較部7a,7bと、この位相比較部7a,7bによる現用系クロックと予備系クロックとの位相比較結果により、可変遅延回路4a,4bの遅延量を制御する位相比較判定部5a,5bとをそれぞれ備えている。

(もっと読む)

位相同期回路

【課題】 セレクタ3によるクロックの切り替え時に、効果的に出力クロックfoの波形の乱れを抑制することは困難であった。

【解決手段】 複数のクロックのいずれかを入力クロックとして選択するセレクタ3と、入力クロックを分周する1/m分周器4と、出力クロックfoを分周する1/n分周器5と、1/m分周器4により分周されたクロックと1/n分周器5により分周されたクロックとの位相差を検出する位相差検出器7と、位相差検出器7により検出されたその位相差に応じて電圧レベルが変動する入力電圧に基づいて出力クロックfoを出力する電圧制御発振器9と、を備え、その入力電圧の電圧レベルが実質的に一定に保持されたうえで、セレクタ3によって入力クロックとして選択されるクロックが変更される。

(もっと読む)

複数個の出力信号を発生させるフェーズロックループ

【課題】入力クロック信号と同期した複数個の出力クロック信号を調節可能な相対的位相差でもって供給する。

【解決手段】制御可能なオシレータDCOがフェーズロックループの出力信号CKoutを発生し、且つ位相検知器PDがPLL12の入力クロック信号CKinとPLL出力信号CKoutとの間の位相差を決定し、且つオシレータDCOを使用されているクロック信号CKinと同期させる位相検知器出力信号を供給する。ここで、クロック信号CKinと同期されている調節可能な相対的な位相差を有する複数個のPLL出力信号を供給可能にするために、位相差の決定のためにPLLの出力信号CKoutの位相シフトをしたバージョンCK<1:8>を発生し且つ使用されているクロック信号CKinの位相と比較し、且つPLL出力信号CKoutの調節し位相シフトしたバージョンCK<1:8>を更なるPLL出力信号CK<1:8>として供給する。

(もっと読む)

スイッチ可能なフェーズロックループ及びスイッチ可能なフェーズロックループの動作方法

【課題】PLL及びPLLの動作方法に関し、制御可能なオシレータが出力信号を発生し且つPLLの入力クロック信号として使用するために第一クロック信号及び第二クロック信号の間でスイッチオーバーさせる。

【解決手段】現在使用されているクロック信号(CKin1又はCKin2)が出力信号を発生するために、このクロック信号と出力信号との間の位相差が決定され且つオシレータの制御のために使用され、一方現在使用されていないクロック信号(CKin2又はCKin1)が出力信号を発生するために、出力信号に関してのその周波数差が決定され且つ格納され且つ継続的にアップデートされ且つ、前に使用されていないこのクロック信号へのスイッチオーバーの後にオシレータの制御のために提供される。PLL出力信号はどのようなスイッチオーバーに関連する周波数変化よりも迅速に追従することが可能である。

(もっと読む)

局部発振装置及びこれを用いた無線送受信機

【課題】周波数安定性と位相雑音特性に優れた局部発振装置を提供すること。

【解決手段】所定の信号処理手段に入力される少なくとも2つの局部発振信号を出力する局部発振装置であって、固定周波数である第1の局部発振信号を発する第1の発振手段と、可変周波数である第2の局部発振信号を発する第2の発振手段と、を備え、第2の発振手段は、第1の局部発振信号を入力して当該第1の局部発振信号の変化を補正する第2の局部発振信号を出力する。

(もっと読む)

1 - 20 / 24

[ Back to top ]