Fターム[5J106FF04]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 入出力、ループ構成 (832) | 複数出力 (55) | 周波数・位相の異なる複数出力 (31)

Fターム[5J106FF04]に分類される特許

1 - 20 / 31

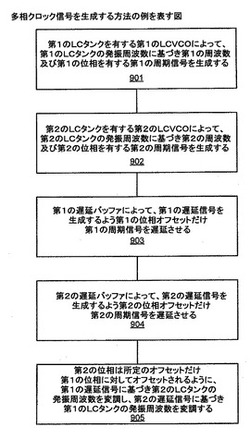

多相信号を生成するための方法、回路及びシステム

【課題】位相誤差を補償しながら設定可能な位相オフセットで多相信号を生成するための方法等を提供する。

【解決手段】一実施形態において、回路は、第1の周波数及び第1の位相を有する第1の周期信号を生成する第1のLC型電圧制御発振器(LCVCO)と、第2の周波数及び第2の位相を有する第2の周期信号を生成する第2のLCVCOとを有し、第2の位相は、90度オフセットで第1の位相に対してオフセットされる。

(もっと読む)

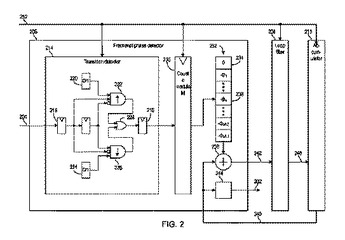

位相同期回路

【課題】位相同期回路においてロックアップを高速化する。

【解決手段】位相同期回路100は、基準信号の周波数にXを乗じて得られる出力周波数を有し、基準信号源180と、電圧制御発振器110と、位相比較器120と、第1チャージポンプ130と、ループフィルタ150と、カウンタ161と、第2チャージポンプ170と、制御回路164とを備える。電圧制御発振器110は、第1信号、および逆相の第2信号を生成する。スイッチ140は、第1チャージポンプ130で生成された電流信号をループフィルタ150に供給する。カウンタ161は、基準信号の1周期期間に含まれる、第2信号のサイクル数をカウントする。第2チャージポンプ170は、互いに反対符号の第1電流信号と第2電流信号をループフィルタ150に供給可能である。制御回路164は、サイクル数とXの値との比較に基づき、スイッチ140および第2チャージポンプ170を制御する。

(もっと読む)

位相調整回路及び位相調整方法

【課題】消費電力を低減し、かつ回路面積も小さい位相調整回路を提供すること

【解決手段】位相調整回路100は、複数の遅延素子回路121〜124をリング状に結合したVCO120を有するPLL発振回路100を備える。また位相調整回路100は遅延素子回路を所望の遅延量に応じた数(125〜127)だけ有し、入力信号に前記所望の遅延量を与える位相遅延回路200、210を備える。PLL発振回路100は基準クロックの入力に応じた基準信号に、基準信号の所定周期分の遅延を与えた発振信号をVCO120において生成する。PLL発振回路100は、基準信号と、発振信号に応じた信号と、が略同位相となるように算出された遅延量に応じた遅延制御信号を遅延素子回路121〜124、及び遅延素子回路125〜127の各々に対して入力する。

(もっと読む)

半導体集積回路及びそれを用いた電子機器

【課題】低速ディジタル回路において発生するノイズがアナログ回路に与える影響を小さくし、回路ブロック毎のレイアウト変更を容易にする。

【解決手段】半導体集積回路は、(a)第1及び第2のVCOと、第1及び第2のVCOによって生成される信号を分周する第1及び第2の分周回路と、2つの分周信号の内の一方を選択する選択回路と、選択された分周信号に基づいて制御電圧を生成する制御電圧生成回路とを含むアナログ回路ブロックと、(b)変復調回路を含む第1のディジタル回路ブロックと、(c)制御回路を含む第2のディジタル回路ブロックとを備え、アナログ回路ブロックが、基板の第1及び第2の辺に沿って配置され、第2のディジタル回路ブロックが、基板の第3及び第4の辺に沿って配置され、第1のディジタル回路ブロックが、アナログ回路ブロックと第2のディジタル回路ブロックとの間に配置されている。

(もっと読む)

クロック装置

【課題】複数のクロック信号を出力するPLL回路において、その特性を問わず、リセットを従来よりも適切なタイミングで行うことを目的とする。

【解決手段】クロック装置は複数のクロック信号を出力するクロック回路を備え、出力するクロック信号を使用して動作している複数の周辺回路からエラー信号を受信し、受信したエラー情報を用いて、前記クロック回路をリセットするか否かを判定し、リセットすると判定した場合に、前記クロック回路をリセットする。

(もっと読む)

半導体集積回路装置

【課題】ノーマルなクロックとSSCとを生成するクロック発生回路における回路面積を低減しながら、高精度のSSCを生成する。

【解決手段】電圧制御発振器から出力されたクロック信号vco1は、分周器13によって分周され、分周クロックph0としてセレクタ15に出力される。分周器13は、制御回路12の制御信号Pconに基づいて、周期の1/mずつ位相のシフトした分周クロックph1〜phmを出力する。セレクタ15は、分周クロックph0〜phmのうち、最も近い位相シフトをもつ2つの分周クロックphj,phj+1を選択する。位相補間回路16は、制御回路12から出力される重み付けデータ信号Aに基づいて、分周クロックphj,phj+1間の位相差の間を更に細分化した位相シフト量で位相シフトさせ、出力クロックfout1として出力する。

(もっと読む)

2分周インジェクションロックリング発振器回路

【解決手段】周波数分周器は、複数のインジェクションロックリング発振器(ILRO)を含む。第1ILROは、クロスカップルされたNチャネルトランジスタの対、負荷抵抗の対、インテグレイトキャパシタ、及び電流注入回路を含む。各トランジスタのドレインは、他方のトランジスタのゲートに結合される。各負荷抵抗は、各トランジスタのドレインを回路電圧源に結合する。インテグレイトキャパシタは、各トランジスタのソースに結合する。電流注入回路は、第1周波数の発振入力信号に応答して、各トランジスタのソースから回路グランドへのパスを交互にオープン及びクローズする。これに応答して、各トランジスタのドレインの電圧状態は交互にラッチ及びトグルされて、2分周された発振信号の差動対が生成される。逆位相で駆動される第1及び第2ILROは、位相直交する2つの差動出力信号を生成する。 (もっと読む)

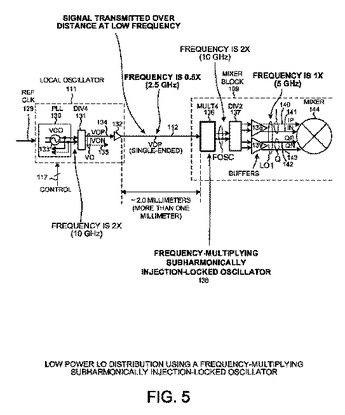

周波数逓倍サブハーモニック注入同期発振器を使用した低電力LO分配

局部発振器は、相対的に低い周波数の信号を、集積回路にわたりミキサの位置まで伝達する。ミキサの近くでは、周波数逓倍サブハーモニック注入同期発振器(SHILO)が、その信号を受信し、それからより高い周波数の信号を発生させる。SHILOがIおよびQ直交位相信号を出力する場合には、IおよびQ信号がミキサをドライブする。SHILOが直交位相信号を発生させない場合には、直交位相発生回路が、SHILO出力信号を受信し、それからミキサをドライブするIおよびQ信号を発生させる。1つの有利な態様において、局部発振器からSHILOまでの距離を越えて伝達される信号の周波数は、近くでミキサをドライブするIおよびQ信号の周波数よりも低い。距離を越えて伝達される信号の周波数を低くすることは、従来のシステムと比較すると、50パーセント以上、LO信号分配システムの電力消費を減じることができる。  (もっと読む)

(もっと読む)

遅延同期ループ回路およびインターフェース回路

【課題】外部クロック信号に対して所定の位相差を有する遅延クロック信号を精度良く生成することができるDLL回路を提供する。

【解決手段】DLL回路1は、制御部10と、第1および第2のノードND(0),ND(n)間に直列接続されたn個(nは2以上の整数)の遅延部D(1)〜D(n)とを含む。第1のノードND(0)には外部クロック信号CLKINが入力される。制御部10は、n個の遅延部D(1)〜D(n)のうち所定の2個の遅延部D(4),D(n)の出力信号CLKA,CLKBの位相差に応じた制御電圧VCを出力する。各遅延部Dは互いに同一の構成を有し、入力された信号に対して制御電圧VCに応じた遅延時間だけ遅延した信号を出力する遅延バッファIと、遅延バッファIの出力を電源電圧の振幅を有する矩形波に整形して出力する整形バッファJとを含む。遅延部D(4)〜D(n)の出力信号が遅延クロック信号として用いられる。

(もっと読む)

クロック生成回路

【課題】位相ロックの精度を向上する。

【解決手段】クロック生成回路は、出力クロックの周期または位相を段階的に遅延する第1の遅延回路および前記第1の遅延回路の遅延時間を設定し制御する第1のカウンタを有する逓倍回路と、前記逓倍回路内の第1の遅延回路から出力された前記出力クロックを入力し、前記出力クロックを所定時間遅延させる第2の遅延回路および前記第2の遅延回路の遅延時間を設定し制御する第2のカウンタを有する位相同期回路を備え、前記逓倍回路は、初期値が第1の値であり第1のカウンタのカウンタ値が一定時間以内で変化しない場合に第2の値が設定される第3のカウンタをさらに有し、前記第3のカウンタのカウンタ値が前記第1の値から前記第2の値に変化した時、前記第2の遅延回路の遅延時間が前記第1の遅延回路の遅延時間と同じかあるいは少し長い遅延時間となるように前記第2のカウンタのカウンタ値を設定する。

(もっと読む)

基準周波数発生装置及び基準周波数発生システム

【課題】冗長化された基準周波数発生システムにおいて、現用側と予備側での出力切替時に出力信号のタイミングが急激に変動するのを防止する。

【解決手段】現用側の基準周波数発生装置51においては、自機のGPS受信機21aが生成する1PPS信号がPLL回路22aに供給される。予備側の基準周波数発生装置52においては、現用側の基準周波数発生装置51のPLL回路22aから出力された1Hzの信号が、第1伝送経路を経由してPLL回路22bに供給される。予備側に入力された1Hzの信号は、前記第1伝送経路と遅延量が等しい第2伝送経路を経由して現用側に戻される。現用側の基準周波数発生装置51は、自機のPLL回路22aからの1Hzの信号と、予備側に出力して戻された1Hzの信号と、の時間差に基づき補正用信号を出力する。予備側の基準周波数発生装置52は、補正用信号に基づいて、PLL回路22bの出力信号の位相を調整する。

(もっと読む)

水晶発振器

【課題】実装スペースとコストの更なる低減のため、電子機器内の水晶部品を1つに集約するためには、消費電流や周波数精度の問題があった。

【解決手段】本発明の水晶発振器は、音叉型水晶振動体と、この振動体の温度による発振周波数の変化を、時間領域で連続的に補正するための温度補償回路を含んだ発振回路とを備え、この発振回路の出力を源振として高周波クロック信号を出力する、複数のPLL(フェイズロックループ)回路を備える。このような構成にすることにより、電子機器内で必要とされる全てのクロック信号を、精度良く提供することができる。

(もっと読む)

基準周波数発生装置

【課題】ユーザ側装置で立上りタイミングが一致した2つの信号を容易に得られる基準周波数発生装置を提供する。

【解決手段】基準周波数発生装置は、ユーザ側装置へ10MHz及び1Hzの信号をそれぞれ出力する2つの出力端子と、ユーザ側装置から戻された上記信号をそれぞれ入力する2つの入力端子と、を備える。基準周波数発生装置を初めてユーザ側装置に接続したときは、2つの出力端子から出力される波形は何れも、その立上りタイミングがUTCの1秒に正確に同期している。この基準状態で、出力する1Hzの波形と、ユーザ側装置から戻された1Hzの波形との間で、立上りタイミングの差が測定される。また、ユーザ側装置から戻された1Hzの波形と、同様に戻された10MHzの波形との間で、立上りタイミングの差が測定される。CPUは、得られた時間差に基づき、10MHz及び1Hzの出力信号波形の位相を所定の関係に従って調整する。

(もっと読む)

PLL回路、及び無線機

【課題】 位相誤差の小さい、発振信号の精度が高いPLL回路及び無線機を提供する。

【解決手段】 第一差動信号を生成する第一発振部と、前記第一差動信号を90度の位相差をもつ第二差動信号を生成する第二発振部と、を有する電圧制御発振器と、前記第一及び第二差動信号に基づく第三差動信号の位相と、基準信号の位相とを比較する位相比較器と、前記位相比較器の比較結果に基づいて、前記電圧制御発振器を制御する制御電圧を生成するループフィルタと、を具備することを特徴とするPLL回路。

(もっと読む)

多相クロック生成回路、オーバーサンプリング回路及び位相シフト回路

【課題】より位相差の微小な多相クロックを生成しつつ、消費電流の増大を抑制した多相クロック生成回路及びオーバーサンプリング回路を提供する。

【解決手段】1対の入出力端子と、遅延量制御端子にバイアスした電圧に応じた遅延量を発生させる2つの遅延ラインの出力の位相差を検出する位相比較器13と、位相比較器13の出力を平均化する平均化フィルタ14とを備え、一方の遅延量制御端子に基準電圧を接続し、他方の遅延量制御端子に平均化フィルタ14の出力を接続し各遅延ラインの出力が所定の位相差を持つように制御する遅延量制御部11と、複数かつ同数個の遅延素子を直列に接続した複数の遅延ライン21を備え、各遅延ライン21は基準電圧を接続した遅延素子22の数及び平均化フィルタ14の出力電圧を接続した遅延素子の数の組み合わせを異ならせたクロック遅延部20とを備え、所定の位相差を持つ多相クロックを生成する。

(もっと読む)

小数位相検出器を用いたクロック生成

入力信号から、低減されたスキューを有する1つまたはより多くの出力クロック信号を生成する回路が提供される。入力信号は、出力クロック信号の周波数とは異なった周波数を有するオリジナルクロックの遷移から導き出される遷移を有する。出力クロック信号の周波数は、入力信号についての周波数と、整数比との乗算からの積である。回路は、積算器と、小数位相検出器と、ループフィルタを含む。積算器は、数値的オフセット値を数値的位相値に周期的に追加する。出力クロック信号は、この数値的位相値から生成される。小数位相検出器は、数値的位相値から、入力信号の遷移の各々についてのそれぞれの数値的位相誤差を生成する。ループフィルタは、それぞれの数値的位相誤差のフィルタリングから数値的オフセット値を生成する。  (もっと読む)

(もっと読む)

位相制御装置、位相制御プリント板、制御方法

【課題】出力信号の位相を微小に制御することを課題とする。

【解決手段】第1の遅延ラインでは、入力信号の入力を受け付けると、信号の位相に対して遅延量を加える遅延器各々によって当該入力信号の位相に対して遅延量を加えるとともに当該遅延器ごとの遅延信号を出力し、DLL回路では、第2の遅延ラインが、外部にて周波数の異なる信号に切り替えることが可能である外部信号の入力を受け付けると、遅延器各々によって当該外部信号の位相に対して遅延量を加え、第2の遅延ラインの複数の遅延器すべてによって遅延された遅延信号と、当該第2の遅延ラインにて遅延量が加えられていない外部信号との位相差を比較し、位相比較器によって比較される遅延信号を外部信号に同期させる電圧であって、当該位相比較器によって出力された位相差から生成された制御電圧を、第1の遅延ラインおよび第2の遅延ラインの複数の遅延器各々に入力する。

(もっと読む)

無線受信機及び電子機器

【課題】低消費電力の振幅変調無線受信機を提供すること。

【解決手段】無線受信機は、無線周波数入力信号および利得制御信号を受信し、増幅信号

を提供する増幅器と、高閾値コンパレーターの出力を受信し利得制御信号を提供する自動

利得制御回路と、増幅信号および局部振動信号を組み合わせて混合出力を提供するミキサ

ーと、混合出力を基準レベルと比較し高閾値コンパレーターの出力を提供する高閾値コン

パレーターと、混合出力を基準レベルと比較し無線受信機の出力を提供する低閾値コンパ

レーターとを含む。

(もっと読む)

遅延ロックループ回路

【課題】クロック信号CKに対し、1周期Tだけ正確に遅れた出力信号OT、及び、可変遅延回路70に用いたn個の各遅延セルにて均等な遅延時間T/nの出力信号を得る。

【解決手段】DLL回路は、制御信号CTLに基づき遅延時間が変わる同一構成の遅延セル50−11,〜,50−3nにより構成される第1、第2の入力ゲート40−1,40−2及び可変遅延セル70と、遅延セル50−11と入力容量が同一の位相比較回路80内の第3、第4の入力ゲート82−1,82−2とを有している。位相比較回路80は、クロック信号CKが入力ゲート40−1を経た出力信号CK−Aと、クロック信号CKが入力ゲート40−2と可変遅延回路70とを経て遅延した出力信号OTとの各信号波形の位相を比較する。その比較結果は、負帰還を掛ける制御信号CTLとして、入力ゲート40−1、40−2及び可変遅延回路70へ与えるようにした。

(もっと読む)

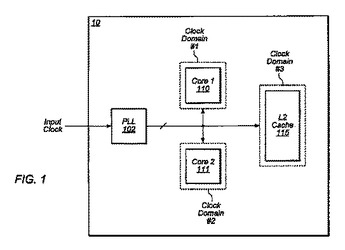

クロックサイクルスチールのための方法および装置

複数のクロック信号を生成するための方法。前記方法は、位相ロックループ(PLL)を使用して基準クロック信号を生成するステップを有する。前記基準クロックが、複数のクロック分周器ユニットのそれぞれに供給され、前記複数のクロック分周器ユニットのそれぞれが、前記受信基準クロック信号を分周して、対応する分周クロック信号を生成する。前記方法は、前記対応する受信分周クロック信号の周波数と、除去するサイクル数とに基づいて、それぞれが有効周波数を有する複数のドメインクロック信号を生成するために、(所定の数のサイクルにつき)1以上のクロックサイクルを除去する。  (もっと読む)

(もっと読む)

1 - 20 / 31

[ Back to top ]