Fターム[5J106GG10]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 制御対象 (2,074) | 位相変換回路 (225)

Fターム[5J106GG10]に分類される特許

1 - 20 / 225

自励発振型D級アンプおよび自励発振型D級アンプの自励発振周波数制御方法

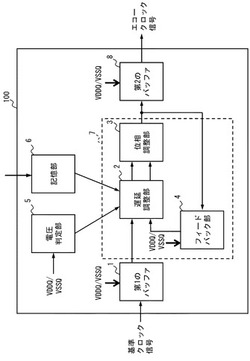

半導体装置

【課題】半導体装置の入出力クロックスキューを抑制する。

【解決手段】I/O電圧電源で駆動される第1のバッファ1及び第2のバッファ8と、I/O電圧電源の電圧レベルを示す電圧判定信号を生成する電圧判定部5と、第1のバッファ1を介して入力された入力クロック信号に基づいて出力クロック信号の位相を調整して第2のバッファへ出力するエコークロック生成部7と、電圧判定信号と位相の調整量との関係を選択するモード情報を記憶する記憶部6と、を有し、エコークロック生成部7は、電圧判定信号とモード情報とに基づいて出力クロック信号の位相の調整量を決定する。

(もっと読む)

周波数調整装置及びそれを含むDLL回路

【課題】半導体集積回路の電磁干渉を減少させる周波数調整装置及びそれを含むDLL回路を提供する。

【解決手段】本発明の周波数調整装置は、基準クロックの周波数を複数の分周比に分周して複数のビットの周波数制御信号を生成する周波数制御信号生成部、及び前記複数のビットの周波数制御信号に応答して、入力される前記基準クロックの周波数を調整する周波数調整部とを含むことを特徴とする。

(もっと読む)

DLL回路、逓倍回路、及び半導体記憶装置

【課題】例えば、遅延クロックの位相と基準クロックの位相とを同期させるためのロック時間を低減する。

【解決手段】1つの実施形態によれば、ディレイチェーン、複数の位相比較器、制御部を有するDLL回路が提供される。ディレイチェーンでは、複数段の遅延素子が直列に接続されている。複数段の遅延素子は、基準クロックに対して互いに異なる遅延量のクロックを発生させる。複数の位相比較器は、基準クロックをそれぞれ受けるとともに、複数段の遅延素子における互いに異なる段の遅延素子からクロックを受ける。制御部は、複数の位相比較器による比較結果に基づいて、複数段の遅延素子のうち基準クロックに対して位相が同期するクロックを発生させる段数を決定する。制御部は、遅延クロックを出力するように、その決定された段数に基づいて複数段の遅延素子における出力段数を選択する。遅延クロックは、基準クロックが要求に応じた遅延量で遅延されたクロックである。

(もっと読む)

デューティ補正付き位相調整回路及びシリアライザ

【課題】クロックのばらつきが引き起こすジッタを抑制することが可能なデューティ補正付き位相調整回路及びシリアライザを提供することを目的としている。

【解決手段】正クロック信号及び負クロック信号が入力され前記正クロック信号と前記負クロック信号のデューティ及び位相を調整した正クロック出力信号及び負クロック出力信号を出力する。

(もっと読む)

多相クロック発生回路、及び多相クロック発生方法

【課題】回路規模の増加を抑えかつ出力信号のジッタ特性を低下させずに、複数の動作周波数に対応できる多相クロック発生回路を提供する。

【解決手段】多相クロック発生回路は、位相の異なる複数のリファレンスクロック信号が入力され、該リファレンスクロック信号が取り得る複数の周波数ごとに設けられた遅延パスであって該リファレンスクロック信号に対して予め定められた位相差を生じさせる複数の遅延パスと、リファレンスクロック信号の周波数に基づいて、複数の遅延パスのうち、リファレンスクロック信号の周波数に対応する遅延パスを選択するスイッチ部と、スイッチ部が選択した遅延パスにより、位相差が変更された複数のリファレンスクロック信号から所定の位相差を有する複数のクロック出力信号を生成する位相補間回路とを備える。

(もっと読む)

半導体装置

【課題】サンプル間、温度等の変位に伴い発生するロック位相の変動を補正し、ロック位相を一定とすることができるDLLを備えた半導体装置を提供する。

【解決手段】位相検出回路(PD)105を構成する複数のMOSFETのうち所定のMOSFETのバックゲート電位を変更するPDバックゲート電位変更回路106と、温度センサ107と、サンプル別閾値電圧(Vt)情報を記憶したFuse(ヒューズ)108を備える。温度センサ107の温度情報、Fuse(ヒューズ)108に記憶されたサンプル別閾値電圧(Vt)情報は、PDバックゲート電位変更回路106に読み出され、閾値電圧を制御し、ロック位相の変動を補正する。

(もっと読む)

遅延ロックループ回路及びロックアップ方法

【課題】レイアウト面積の増加を抑えつつロックアップ時間の高速化を実現する。

【解決手段】本発明に係る遅延ロックループ回路1は、遅延ライン3と、初期遅延モニタリング部4と、位相比較部5と、遅延制御部6と、ファイン遅延部7とを備え、初期遅延モニタリング部4は、基準クロックと複数の単位遅延部のうちの一部の単位遅延部が出力する単位遅延クロックとの位相を比較する複数の位相比較用フリップフロップを備え、これら位相比較用フリップフロップの数を単位として当該比較を段階的に繰り返すことにより、全範囲について初期遅延モニタリングを行うものである。

(もっと読む)

位相調整回路及び位相調整方法

【課題】LSIチップ面積の増大を抑制しつつ、製造ばらつきや使用条件の影響を受けない安定的な位相調整を実現する

【解決手段】入力クロックと出力クロックの位相差を調整する位相調整回路を以下のように構成する。その位相調整回路は、出力クロックに遅延を付加するクロック遅延回路と、入力クロック、もしくは、入力クロックと出力クロックの位相差のパルスを入力として受け、パルス除去幅設定値によって遅延素子の段数を変化させて、入力クロック、もしくは、入力クロックと出力クロックの位相差のパルスの幅を検出する位相差検出回路とを有することが好ましい。そして、位相差検出回路で検出した入力クロックと出力クロックの位相差が入力クロックに対して目標の位相差になるようにクロック遅延回路にて出力クロックに遅延を付加する。

(もっと読む)

半導体集積回路装置、及び、クロックデータ復元方法

【課題】インターポレータ方式のクロックデータ復元回路において、インターポレータ回路の広帯域化を行わず、マルチレートに対応したクロックデータ復元回路を実現する。

【解決の手段】インターポレータ回路の生成クロックを分周し、リカバリクロックを生成する。また、インターポレータ回路が生成するクロックの位相を制御するポインタは分周前のクロックを使い、その他の回路は分周後のリカバリクロックを使い動作する。

(もっと読む)

クロック生成装置および電子機器

【課題】レプリカ回路が不要で、小面積化を図ることが可能であり、しかもジッタの増加を防止でき、低ジッタ出力クロックを生成することが可能なクロック生成装置および電子機器を提供する。

【解決手段】アキュムレータの値に応じて目標とするNCOクロックと実際のNCOクロックとの位相差を取得する位相差取得部と、入力クロックに位相同期した信号に応じて入力クロックに複数の遅延を与えた複数の遅延クロックを生成する遅延同期回路と、位相差取得部の位相差情報を受けて複数の遅延クロックから目標とする上記NCOクロックの位相に近づくような遅延が与えられた遅延クロックを選択し、選択クロックとして出力する選択部と、選択部で選択された上記選択クロックに上記NCOクロックを同期させて出力クロックを得る第2の同期回路とを有する。

(もっと読む)

シリアル・データ通信装置のDPLL回路

【課題】PLCで設計・構成するシリアル・データ通信の高速化を図ることができ、しかも受信データのジッタ許容範囲を明確にできる。

【解決手段】DPLL回路10のうち、データシフト回路DS1〜DS3は受信データからソースクロックCLKで同期を取った複数のシリアル・データを生成する。排他的論理和回路EX_ORは一対のシリアル・データから受信データの変化点を検出する。カウンタDPLCNTは、最大カウント値nが設定され、変化点から次の変化点までをソースクロックをカウントする。一致判定回路ANDはカウンタのカウント値が予め設定したカウント値n/2に一致したときに受信クロックとして出力する。ハイレベル・データ・リンク・コントローラ・モジュール(HDLC−IP)20は、受信クロックを使って受信データ(シリアル・データ)の転送制御を行う。

(もっと読む)

アキュムレータ型フラクショナルN−PLLシンセサイザおよびその制御方法

【課題】フラクショナル分周器の分周数を周期的に切り替えることに起因するフラクショナルスプリアスを抑制したアキュムレータ型フラクショナルN−PLLおよびその制御方法を実現する。

【解決手段】アキュムレータ型フラクショナルN−PLLシンセサイザ100を、その参照信号入力側の位相検出器の前段にアキュムレータ120からの誤差信号によって上記参照信号に対し位相調整を行う位相調整回路130を介挿して構成し、出力段のVCO114の出力を前段側にフィードバックするフラクショナル分周器115の出力である帰還信号と、上記位相調整された参照信号との両信号の位相差が生じないようにして、該両信号の位相差に応じた出力を得る位相検出器111の出力によってチャージポンプ112が駆動されないようにすることによって、フラクショナル分周器115の分周数を周期的に切り替えることに起因するフラクショナルスプリアスを抑制するように構成する。

(もっと読む)

デジタルPLL回路及びクロック生成方法

【課題】位相差検出値の範囲の制限により引き込み動作が影響されることのないデジタルPLL回路を提供する。

【解決手段】デジタルPLL回路は、マスタクロックとスレーブクロックとの位相差を検出し、長さが2πの範囲内の値をとる位相差検出値を出力するデジタル位相比較器10と、位相差検出値と閾値とを比較した結果に応じて、位相差検出値を範囲に限定されない位相値に補正する補正部11と、補正部の出力する位相値に応じてスレーブクロックを生成するスレーブクロック生成部15とを含む。

(もっと読む)

スペクトラム拡散クロック発生回路

【課題】分周器の分周比を変化させることを動作原理としない新規なフラクショナルPLL回路を含むSSCG回路であって、出力クロック信号のジッタを低減する。

【解決手段】SSCG回路は、位相周波数比較器1、チャージポンプ2、ループフィルタ、電圧制御発振器4、位相コントローラ5、及び位相選択回路6を備える。位相選択回路6は、電圧制御発振器4からの出力クロック信号vco_ckのクロックの1周期を等分した位相のうちのいずれかを選択し、選択された位相に立ち上がりエッジを有する移相クロック信号pi_outを生成し、これを帰還信号として位相周波数比較器1に送る。位相コントローラ5は、移相クロック信号pi_outの周期を出力クロック信号vco_ckの周期から予め決められた第1の移相量で変化させるように、さらに、所定の範囲内で周期的に変化する第2の移相量を第1の移相量に加算するように、位相選択回路6を制御する。

(もっと読む)

サンプリングクロック生成回路、画像読取装置及び電子機器

【課題】アパーチャディレイをより小さくするアパーチャディレイ調整機能を有するサンプリングクロック生成回路を提供する。

【解決手段】SSCG11からの出力クロック信号に対して所定の遅延量だけ遅延してサンプリングクロック信号を発生してサンプリングホールド回路に供給する、遅延回路21,22及びクロック発生器23からなるサンプリングクロック生成手段と、SSCG11の出力クロック信号に基づいて生成されたCCD駆動クロック信号と、上記サンプリングクロック信号とを位相比較して位相比較結果を出力する遅延型フリップフロップ24と、上記位相比較結果に基づいて、上記駆動クロック信号と上記サンプリングクロック信号との位相差が実質的にゼロとなるように上記サンプリングクロック生成手段の遅延量を制御する制御ロジック回路20とを備えた。

(もっと読む)

フラクショナルPLL回路

【課題】分周器の分周比を変化させることを動作原理としない新規なフラクショナルPLL回路を提供する。

【解決手段】フラクショナルPLL回路は、位相周波数比較器1、チャージポンプ2、ループフィルタ、電圧制御発振器4、位相コントローラ5、及び位相選択回路6を備える。位相選択回路6は、電圧制御発振器4からの出力クロック信号vco_ckのクロックの1周期を等分した位相のうちのいずれかを選択し、選択された位相に立ち上がりエッジを有する移相クロック信号pi_outを生成し、これを帰還信号として位相周波数比較器1に送る。位相コントローラ5は、移相クロック信号pi_outの周期を出力クロック信号vco_ckの周期から予め決められた移相量で変化させるように、位相選択回路6によって選択される移相クロック信号pi_outの立ち上がりエッジの位相を決定し、決定された位相を選択するように位相選択回路6を制御する。

(もっと読む)

クロック生成装置及びDLL(DigitalLockedLoop)回路及びクロック生成方法

【課題】回路規模が小さく、また設計が容易な構成にて、高精度なクロックを生成するDLL回路を実現する。

【解決手段】DLL回路は、外部から入力される動作クロックclksと前記動作クロックと周波数が異なるもしくは等しい入力クロックと所望の周波数を表す設定値kから前記動作クロック周波数の前記設定値k分の一の周波数を有する生成クロックclkcを生成するクロック生成部100と、前記生成クロックclkcと外部から入力される参照クロックclkrの位相差を比較し、その位相差を出力する位相比較部200と、前記位相比較部200の出力である位相差から、前記位相差を“0”とするように前記設定値kへ補正をする補正値を生成し、前記設定値kへ補正値を加算する補正部300とを備える。

(もっと読む)

PLL回路

【課題】PLL回路の引き込時間を短縮する。

【解決手段】位相比較器10は、PLL回路100への入力クロックの位相と、PLL回路100の出力から分周器40を介して帰還される帰還クロックの位相とを比較し、その位相差に応じた信号を生成する。LPF20は、位相比較器10の出力信号に応じた直流電圧を生成する。電圧制御発振器30は、LPF20により生成された電圧に応じた周波数のクロックを出力する。サイクルスリップ予測回路50は、位相比較器10により生成される信号を監視し、サイクルスリップの発生を予測する。サイクルスリップ予測回路50によりサイクルスリップの発生が予測されたとき、入力クロックの位相、帰還クロックの位相および電圧制御発振器に入力される電圧のいずれかが調整される。

(もっと読む)

遅延制御回路、チャージポンプ回路、及びチャージポンプ回路における充放電電流制御方法

【課題】トランジスタがアンバランスであってもチャージポンプ回路に最適なバイアス電圧を与えられる遅延制御回路を提供する。

【解決手段】所定の信号を受けて電流入出力端子から充放電を行うチャージポンプ回路と、電流入出力端子の端子電圧に基づく電圧が電源として供給される遅延回路と、チャージポンプ回路の充放電電流の基準となるバイアス電圧を生成するバイアス生成回路と、を備え、チャージポンプ回路及び遅延回路が、それぞれ、第1導電型トランジスタと、第2導電型トランジスタを含んで構成され、バイアス生成回路が、第1導電型トランジスタの相互コンダクタンスと第2導電型トランジスタの相互コンダクタンスの和に基づいて、バイアス電圧を生成する。チャージポンプ回路の充放電により遅延回路の電源電圧を制御し、これにより遅延回路の遅延時間を制御する。

(もっと読む)

1 - 20 / 225

[ Back to top ]