Fターム[5J106HH01]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 制御量 (1,632) | 周波数 (367)

Fターム[5J106HH01]に分類される特許

1 - 20 / 367

自励発振型D級アンプおよび自励発振型D級アンプの自励発振周波数制御方法

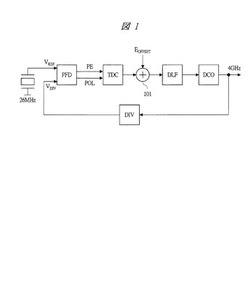

PLL回路

【課題】ディジタル回路で構成されるADPLLにおいて、位相差0近傍における位相差

検出を改善することができる技術を提供する。

【解決手段】基準信号VREFフィードバック信号VDIVとの位相及び周波数を比較するPFDと、PFDの出力をディジタル値に変換するTDCと、TDCの出力から高周波雑音成分を除去するDLFと、DLFの出力に基づいて制御されるDCOと、DCOの出力を分周しフィードバック信号VDIVを出力するDIVによりフィードバックループが構成される。フィードバックループのいずれかの箇所にオフセット値が加算され、フィードバック信号VDIVの位相が制御され、ロック時にもTDCに0ではない値が入力される。

(もっと読む)

原子発振器

【課題】磁気量子数mF=0におけるEIT信号のピーク値を高くした原子発振器を提供する。

【解決手段】本発明の原子発振器100は、アルカリ金属原子に電磁誘起透過現象を発現させるための第1の共鳴光、及び第2の共鳴光を発生する半導体レーザー(光源)1と、半導体レーザー1から発生した共鳴光1aを円偏光するλ/4波長板2と、アルカリ金属原子が封入された原子セル3と、原子セル3から出射した共鳴光3aの強度を検出する光検出手段5と、アルカリ金属原子に所定の強度の直流磁場を与える直流磁場発生手段4と、直流磁場の強度に応じた所定の周波数の交流磁場をアルカリ金属原子に与える交流磁場発生手段8と、光検出手段5から出力された共鳴光の中心波長を制御する中心波長制御手段9と、アルカリ金属原子にEIT現象を発現させるように、第1の共鳴光と第2の共鳴光との周波数差を制御する制御手段10と、を備えて構成されている。

(もっと読む)

原子発振器

【課題】専用の電源を不要として、小型化と省エネを実現した原子発振器を提供する。

【解決手段】本実施形態に係る原子発振器100は、アルカリ金属原子(Na、Rb、Cs)が封入された原子セル3と、アルカリ金属原子に電磁誘起透過現象を発現させるための共鳴光2を照射する半導体レーザー(光源)1と、原子セル3を透過した透過光(共鳴光対)4を検出する光検出手段5と、アルカリ金属原子が発する蛍光6の強度に応じた電力を発電する太陽電池(発電手段)7と、太陽電池7から供給された電力によってアルカリ金属原子に与える磁場を発生するコイル(磁場発生手段)8と、光検出手段5で検知した信号を同期制御する制御手段9と、を備えて構成されている。

(もっと読む)

電子機器

【課題】局所的な温度上昇が発生した場合であっても、温度センサによる補正値と水晶振動子の周波数ドリフトとの追従ができる電子機器を提供する。

【解決手段】温度センサ素子で計測された温度を用いて水晶振動子の振動に対する補正を行う電子機器1は、基板上に配置された水晶振動子13と、温度を計測する温度センサ素子14とを備え、前記主表面のうち前記水晶振動子13で覆われた部分領域の基板内部に前記温度センサ素子14の少なくとも一部が配置される。

(もっと読む)

周波数調整装置及びそれを含むDLL回路

【課題】半導体集積回路の電磁干渉を減少させる周波数調整装置及びそれを含むDLL回路を提供する。

【解決手段】本発明の周波数調整装置は、基準クロックの周波数を複数の分周比に分周して複数のビットの周波数制御信号を生成する周波数制御信号生成部、及び前記複数のビットの周波数制御信号に応答して、入力される前記基準クロックの周波数を調整する周波数調整部とを含むことを特徴とする。

(もっと読む)

無線機

【課題】煩雑なメンテナンスを行わなくても周波数精度を高く保つことができ、かつ変調信号による周波数偏移を大きくすることができる無線機を提供する。

【解決手段】基準信号を出力する電圧制御水晶発振器と、高周波信号を出力する電圧制御発振器と、基準信号と高周波信号とが入力され、高周波信号の位相が基準信号と同じになるように位相同期を行う位相同期回路と、参照信号を発生する参照信号発生部と、基準信号の周波数を補正する周波数補正信号を電圧制御水晶発振器に出力するとともに、基準信号と参照信号とに基づき、基準信号の周波数が参照信号の周波数に対して所定の範囲内となるように周波数補正信号の値を変更する制御部と、から無線機を構成する。

(もっと読む)

PLL回路およびそのキャリブレーション方法

【課題】1回のキャリブレーションによって電圧制御発振器のフリーラン発振周波数がPLLロックレンジ内に入るようにして、キャリブレーション時間の大幅な時間短縮が可能となり、低消費電流化に貢献できるようにする。

【解決手段】PLLループをオープンにし、電圧制御発振器1に制御電圧Vcとして基準電圧Vaを入力したとき、基準信号f3のパルスによって帰還信号f2のパルス幅をカウントし、得られたカウント値に基づき、電圧制御発振器1の発振周波数f1を調整するキャリブレーションを実行するキャリブレーション回路10を設ける。

(もっと読む)

クロック発振回路

【課題】発振周波数のトリミングを行うクロック発振回路であって、CR発振回路の特性に起因する発振周波数のばらつきを低減することが可能なクロック発振回路を提供する。

【解決手段】クロック発振回路は、周波数調整コードに応じた発振周波数のクロック信号を生成する発振部101と、発振部101の発振周波数をカウントするOSCクロックカウンタ102と、外部接続された水晶発振器の発振周波数をカウントする基準クロックカウンタ103と、両発振周波数の比較を行う比較回路104とを備える。また、周波数調整コードの自動探索を行う探索回路105を備える。探索回路105は、周波数調整動作時において、発振部101に対する周波数調整コードの設定と、比較回路104による比較結果に応じた周波数調整コードの更新とを繰り返し行うことにより、周波数調整コードの自動探索を行う。

(もっと読む)

PLL回路

【課題】本発明は、C/Nの向上及び高速な周波数の切り替えを両立するPLL回路を提供することを目的とする。

【解決手段】本発明は、基準信号FREFと出力信号CKVの間の位相差が0になるような出力信号CKVを出力するDCO1と、位相差を示すデジタル信号を出力する位相検出器10と、位相差を示すアナログ信号を出力し、デジタル信号の少なくとも最下位1ビットに相当し位相差として0を含む位相差の範囲内で、位相差とアナログ信号の間の線形特性を有するEXOR型位相比較器21と、デジタル信号が示す位相差が、デジタル信号の最下位1ビットに相当し位相差として0を含む位相差の範囲内に入ったとき、位相比較の主体を位相検出器10からEXOR型位相比較器21へ切り替える切替制御部Sと、を備えることを特徴とするPLL回路Pである。

(もっと読む)

無線送信機

【課題】局部発振器の位相雑音性能の改善により、送信信号に含まれる隣接チャネル漏洩信号を大幅に低減することができる無線送信機を提供する。

【解決手段】ディジタルデータ信号を出力するデータ信号生成回路と、ディジタルデータ信号をディジタル/アナログ変換し、中間周波数のIF信号を出力するディジタル/アナログ変換回路と、IF信号と局部発振器から出力されるローカル信号とをミキシングし、無線周波数のRF送信信号を出力する直交ミキサ回路とを備えた無線送信機において、データ信号生成回路は、ディジタル/アナログ変換回路から出力されるIF信号の周波数が送信チャネルに応じて切り替わるディジタルデータ信号を出力する構成であり、局部発振器は、RF送信信号のチャネル周波数間隔のn倍(nは3以上の整数)の周波数間隔のローカル信号を切り替えて出力する構成である。

(もっと読む)

高周波信号処理装置および無線通信システム

【課題】ディジタル型PLL回路を備えた高周波信号処理装置および無線通信システムにおいて、スプリアスの影響を低減する。

【解決手段】例えば、ディジタル位相比較部DPFD、ディジタルロウパスフィルタDLPF、ディジタル制御発振部DCO、マルチモジュールドライバ部(分周部)MMDを備えたディジタル型PLL回路において、DLPFのクロック信号CKDLPFのクロック周波数が複数の選択肢の中から選択可能に構成される。当該クロック周波数は、基準発振信号Frefの整数倍の周波数の中から、DCOの発振出力信号RFdcoに対して規格上のどの周波数帯を設定するかに応じて選択される。

(もっと読む)

周波数調整回路、位相同期回路、通信装置及び記憶装置

【課題】帯域制限フィルタを含むPLLのロックアップ時間を短縮する。

【解決手段】実施形態によれば、周波数調整回路200は、レジスタ213と、デジタルアナログ変換器220と、帯域制限フィルタ250と、バッファアンプ240とを含む。レジスタ213は、第1の動作モードの終了時にデジタル制御コード12を保存し、第3の動作モードの開始時に出力する。第1の動作モードにおいて、制御電圧15を持つアナログ制御信号14が電圧制御発振器110の制御端子に供給される。第2の動作モードにおいて、アナログ制御信号14がバッファアンプ240に供給され、バッファアンプ240は帯域制限フィルタ250を駆動し、帯域制限フィルタ250は制御電圧15を生成する。第3の動作モードにおいて、アナログ制御信号14が帯域制限フィルタ250に供給され、帯域制限フィルタ250は制御電圧15を生成する。

(もっと読む)

発振回路およびそれを用いた電子機器

【課題】スペクトルのピークを抑制する。

【解決手段】発振回路2は、基準クロック信号CKREFを受け、出力クロック信号CKOUTを生成する。プログラマブル分周器18は、その分周比が少なくとも2値で切りかえ可能に構成され、出力クロック信号CKOUTを設定された分周比で分周し、分周クロック信号CKDIVを生成する。位相比較器10は、基準クロック信号CKREFと分周クロック信号CKDIVの位相差に応じた位相差信号S1を生成する。ループフィルタ12は、位相差信号S1を平滑化する。VCO(電圧制御発振器)14は、ループフィルタ12から出力される位相差信号S2に応じた周波数で発振し、出力クロック信号CKOUTを生成する。制御部20は、プログラマブル分周器18の分周比を、時分割的に切りかえることにより出力クロック信号CKOUTのスペクトルを拡散させる。

(もっと読む)

発振装置

【課題】メモリの容量を抑えることができる発振装置を提供すること。

【解決手段】第1の発振回路の発振周波数をf1、基準温度における第1の発振回路の発振周波数をf1r、第2の発振回路の発振周波数をf2、基準温度における第2の発振回路の発振周波数をf2rとすると、f1とf1rとの差分に対応する値と、f2とf2rとの差分に対応する値と、の差分値に対応する差分対応値を求める周波数差検出部と、この周波数差検出部にて検出された前記差分対応値xに基づいて環境温度が基準温度と異なることに起因するf1の周波数補正値を取得する補正値取得部と、を備え、装置固有の除算係数をkとすると、前記補正値取得部は、x/kに相当する値であるXについてn次の多項式を演算することによりf1の周波数補正値を求める機能を備えるように装置を構成して、多項式の係数を小さくする。

(もっと読む)

クロック生成装置

【課題】 異なる複数の基準周波数に同期したクロックを生成でき、また、自走動作時に、ノイズの発生と消費電力を低減することができるクロック生成装置を提供する

【解決手段】 複数の外部基準クロックを入力可能とし、信号レベル検出回路24,25部が入力された外部基準信号の帯域毎にレベル検出し、マイクロコントローラ4が、検出された信号レベルに応じて、一つの外部基準信号のみが適正レベルであった場合に、自走制御信号によりクロック選択回路34の外部基準クロックの出力をイネーブルとし、選択制御信号により適正レベルであった外部基準クロックを選択させ、それ以外の場合には、自走制御信号によりクロック選択回路34の外部基準クロックの出力をディセーブルとすると共に、PLL−IC5をパワーダウンさせて、電圧制御発振器9に自走制御用直流電圧生成回路6からの電圧に基づいて自走発振を行わせるクロック生成装置としている。

(もっと読む)

レベル調整装置

【課題】 基準発振器、VCO、位相比較器の純度が低くても位相雑音特性を良好にする。

【解決手段】 基準発振器28aが発振する基準周波数frefをBS放送波のチャンネル間隔とされる38.36MHzに設定する。そして、中間周波数を282.28(=7×38.36+13.76)MHzとした場合は、1049.48MHzのチャンネル周波数とされるBS−1チャンネルがアサインされるBS−IFレベル調整ユニット10では、局部発振器28の出力周波数foutが767.2MHzになり、分周器28eの分周数Nを20とすればよい。基準周波数frefを38.36MHzと高くすることができるため、局部発振器28の位相雑音特性が良好になる。

(もっと読む)

半導体集積回路装置、及び、クロックデータ復元方法

【課題】インターポレータ方式のクロックデータ復元回路において、インターポレータ回路の広帯域化を行わず、マルチレートに対応したクロックデータ復元回路を実現する。

【解決の手段】インターポレータ回路の生成クロックを分周し、リカバリクロックを生成する。また、インターポレータ回路が生成するクロックの位相を制御するポインタは分周前のクロックを使い、その他の回路は分周後のリカバリクロックを使い動作する。

(もっと読む)

クロック供給回路及び半導体集積回路

【課題】高速なクロックを内部回路に供給するためには、消費電力の高いクロックバッファを必要とする。そのため、高速なクロックを低消費電力で供給するクロック供給回路及び半導体集積回路が、望まれる。

【解決手段】クロック供給回路は、電圧制御発振器を含むPLL回路と、電圧制御発振器の発振周波数を制御する発振制御電圧に基づいて、電圧制御発振器の発振周波数と略同一の周波数を持つクロックを、PLL回路のリファレンスクロックに同期させて出力する自己発振型バッファ回路と、を備えている。

(もっと読む)

PLL回路

【課題】短時間でかつ正確に、所望の周波数の発振信号にロック可能なPLL回路を提供する。

【解決手段】PLL回路は、粗調整ループ部と微調整ループ部を有する。前記粗調整ループ部は、前記複数の第1切替部の切替情報を記憶する切替情報記憶部と、複数の第1切替部の新たな切替情報を設定する切替情報設定部と、切替情報設定部で設定した複数の第1切替部の切替情報に基づいて調整した電圧制御型発振器の発振信号を分周した分周信号を生成する分周器と、分周信号の周波数と基準信号の周波数とを比較した結果に基づいて、切替情報設定部に対して切替情報の再設定を指示する発振周波数調整部と、切替情報設定部で設定した切替情報と、切替情報記憶部に記憶されている切替情報と、の差分情報を生成し、該差分情報が所定の閾値範囲内であれば、ループ制御部に粗調整の終了を報知し、差分情報が閾値範囲外の場合には、切替情報設定部に対して切替情報の再設定を指示する比較器と、を有する。

(もっと読む)

1 - 20 / 367

[ Back to top ]