Fターム[5J106KK37]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、効果 (3,441) | IC化,LSI化 (197)

Fターム[5J106KK37]に分類される特許

1 - 20 / 197

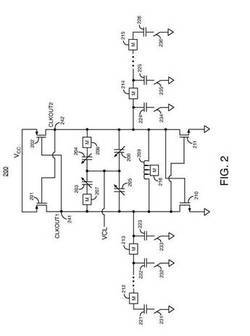

発振回路内で構成要素を接続するオプションコンダクタを提供する技術

【課題】発振回路内で構成要素を接続するオプションコンダクタの使用を可能とする技術の提供。

【解決手段】発振回路200は、第1の伝導層内でルーティングコンダクタを介して相互結合されるトランジスタを含む。発振回路はまた、第2の伝導層内に、バラクタ203〜206、コンデンサ221〜226、及びオプションコンダクタ207、208,212〜216も含む。オプションコンダクタは、トランジスタのうちの1つとコンデンサまたはバラクタとの間の接続の少なくとも一部を形成する。上記発振回路は、第1の伝導層内のルーティングコンダクタを介して前記複数の第1のトランジスタのうちの1つに結合されるインダクタと、該インダクタの第1の部分を形成する、前記第2の伝導層内の第2のオプションコンダクタとをさらに備え得る。

(もっと読む)

半導体集積回路装置

【課題】半導体集積回路装置の内部回路に供給されるクロック信号の周波数が、正常時よりも高くなった場合の上記内部回路の暴走を回避する。

【解決手段】半導体集積回路装置(1)において、内部回路(17)と、水晶振動子を用いた発振動作によりクロック信号を形成する水晶発振回路(11)と、上記内部回路が正常に動作可能な周波数のクロック信号を形成する内蔵発振器(14)とを設ける。また上記水晶発振回路で形成されたクロック信号の周波数が、上記内部回路の正常動作の周波数範囲よりも上昇したことを検出可能な異常高速発振検出回路(13)を設ける。さらに上記異常高速発振検出回路での検出結果に基づいて、上記水晶発振回路で形成されたクロック信号に代えて、上記内蔵発振器で形成されたクロック信号を上記内部回路に供給するための制御回路(16)を設けることで、内部回路の暴走を回避する。

(もっと読む)

半導体装置

【課題】半導体装置の入出力クロックスキューを抑制する。

【解決手段】I/O電圧電源で駆動される第1のバッファ1及び第2のバッファ8と、I/O電圧電源の電圧レベルを示す電圧判定信号を生成する電圧判定部5と、第1のバッファ1を介して入力された入力クロック信号に基づいて出力クロック信号の位相を調整して第2のバッファへ出力するエコークロック生成部7と、電圧判定信号と位相の調整量との関係を選択するモード情報を記憶する記憶部6と、を有し、エコークロック生成部7は、電圧判定信号とモード情報とに基づいて出力クロック信号の位相の調整量を決定する。

(もっと読む)

時間−デジタル変換器及びPLL回路

【課題】本発明は、発振器が出力する出力信号の1周期に小数分周の分解能つまり位相の分解能が依存しないTDCを提供することを目的とする。

【解決手段】本発明は、直列に接続され入力端で発振器が出力する出力信号CKVを入力される複数の遅延素子21と、複数の遅延素子21が出力する複数の遅延クロック信号を、PLL回路が入力される基準信号FREFのエッジタイミングでそれぞれラッチする複数のラッチ回路22と、直列接続された複数の遅延素子21の入力端で入力される出力信号CKVと、直列接続された複数の遅延素子21の出力端で出力される出力デジタル信号が、エッジタイミングを等しくするように、複数の遅延素子21の遅延時間を調整する遅延時間調整回路32と、を備えることを特徴とするTDC2である。

(もっと読む)

発振回路、発振装置およびクロックジェネレータ

【課題】消費電力を低減することができる発振回路を提供する。

【解決手段】入力信号が含むアナログ成分をデジタル信号に変換するアナログ/デジタル変換回路100と、アナログ/デジタル変換回路100で変換されたデジタル信号D1について、予め設定された周波数帯域成分のみを基準信号として通過させるバンドパスフィルタ101と、バンドパスフィルタ101を通過した基準信号D2と、PLLループ内に設けられる電圧制御発振器203からの出力信号D3との位相差が一定となるように電圧制御発振器203にフィードバック制御を行って発振させるPLL回路200とを備え、バンドパスフィルタ101は、所定の条件に基づいて、アナログ/デジタル変換回路100で変換されたデジタル信号D1の所定ビット幅について、「0」に固定するマスク処理を実行するマスク処理部102を備える。

(もっと読む)

半導体装置

【課題】調整コードの変化に伴うジッタの発生が低減されたDLL回路を提供する。

【解決手段】内部クロック信号ECLKを受けるインバータ回路210〜217と、内部クロック信号OCLKを受けるインバータ回路220〜227とを有し、調整コードC0〜C7を受けて選択されたインバータ回路の出力を合成することによって、内部クロック信号LCLKの位相を16段階に調整する。インバータ回路210,220は内部クロック信号LCLKの位相を1段階変化させる能力を有し、インバータ回路211〜217,221〜227は内部クロック信号LCLKの位相を2段階変化させる能力を有する。このように、内部クロック信号LCLKの位相を調整するインバータ回路の最大能力が抑制されていることから、調整コードの変化に伴うジッタの発生が低減される。

(もっと読む)

無線受信機

【課題】PLLのループフィルタの帯域を大きくすることにより、局部発振器の位相雑音性能が大幅に改善し、隣接チャネル選択性能を改善する受信機を提供する。

【解決手段】受信信号と局部発振器から出力されるローカル信号とをミキサでミキシングし、生成された中間周波数(IF)信号をバンドパスフィルタで選択して復調する無線受信機において、局部発振器は、受信信号のチャネル周波数間隔のn倍(nは3以上の整数)の周波数間隔のローカル信号を切り替えて出力する構成であり、バンドパスフィルタは、受信信号の受信すべきチャネルによって通過帯域の中心周波数を切り替える構成である。

(もっと読む)

位相調整回路及び位相調整方法

【課題】LSIチップ面積の増大を抑制しつつ、製造ばらつきや使用条件の影響を受けない安定的な位相調整を実現する

【解決手段】入力クロックと出力クロックの位相差を調整する位相調整回路を以下のように構成する。その位相調整回路は、出力クロックに遅延を付加するクロック遅延回路と、入力クロック、もしくは、入力クロックと出力クロックの位相差のパルスを入力として受け、パルス除去幅設定値によって遅延素子の段数を変化させて、入力クロック、もしくは、入力クロックと出力クロックの位相差のパルスの幅を検出する位相差検出回路とを有することが好ましい。そして、位相差検出回路で検出した入力クロックと出力クロックの位相差が入力クロックに対して目標の位相差になるようにクロック遅延回路にて出力クロックに遅延を付加する。

(もっと読む)

発振器およびPLL回路

【課題】半導体集積回路上に小面積で形成でき、かつ、適切な周波数の発振信号を生成できる発振器と、これを用いたPLL回路を提供する。

【解決手段】発振器は、第1のノードと第2のノードと間に並列接続される抵抗と、反転増幅器と、半導体素子とを備える。前記半導体素子は、半導体基板と、前記半導体基板に、長辺および短辺を有する形状で形成される音響波伝播層と、少なくとも前記音響波伝播層の長辺方向の両端に形成される音響波反射層と、前記音響波伝播層上に形成され、前記第1のノードと電気的に接続される第1のコンタクトと、前記音響波伝播層上に前記第1のコンタクトとは離れて形成され、前記第2のノードと電気的に接続される第2のコンタクトと、を有する。前記第1のノードまたは前記第2のノードから発振信号を出力する。

(もっと読む)

シリアル・データ通信装置のDPLL回路

【課題】PLCで設計・構成するシリアル・データ通信の高速化を図ることができ、しかも受信データのジッタ許容範囲を明確にできる。

【解決手段】DPLL回路10のうち、データシフト回路DS1〜DS3は受信データからソースクロックCLKで同期を取った複数のシリアル・データを生成する。排他的論理和回路EX_ORは一対のシリアル・データから受信データの変化点を検出する。カウンタDPLCNTは、最大カウント値nが設定され、変化点から次の変化点までをソースクロックをカウントする。一致判定回路ANDはカウンタのカウント値が予め設定したカウント値n/2に一致したときに受信クロックとして出力する。ハイレベル・データ・リンク・コントローラ・モジュール(HDLC−IP)20は、受信クロックを使って受信データ(シリアル・データ)の転送制御を行う。

(もっと読む)

半導体集積回路およびその動作方法

【課題】ループフィルタをオンチップ化する際、トランジスタの素子サイズのバラツキによるPLL回路の特性バラツキを軽減して、回路規模と消費電力の増大を軽減する。

【解決手段】半導体集積回路は、位相周波数比較器1とループアッテネータ2とチャージポンプ3とループフィルタ4と電圧制御発振器5と分周器6を具備するフェーズロックドループ回路を内蔵する。アッテネータ2は、サンプリング回路21とカウンタ22とを含む。回路21にサンプリングパルスSPL_CLKと位相周波数比較器1から出力される第1と第2の出力信号が供給され、回路21はサンプリング出力信号を出力する。カウンタ22は回路21から出力される所定個数のサンプリングパルスのカウントアップを完了すると、カウントアップ完了出力信号を出力する。チャージポンプ3は、カウントアップ完了出力信号に応答してループフィルタ4に充電電流または放電電流を出力する。

(もっと読む)

電流−モード利得分割デュアル−パスVCO

【課題】大きな電圧制御オシレータ(VCO)利得を効率的に取り扱うための技術の提供。

【解決手段】VCOの中心周波数を調節する平均制御電流を供給するための低速高利得パス、及び通常動作の間VCO周波数を調節する瞬間的な制御電流を供給するための高速低利得パス、を利用する。1つのデザインでは、VCOは、電圧−電流コンバータ252、電流増幅器254、総和器256、及び電流制御オシレータ(ICO)260を含む。電圧−電流コンバータは、制御電圧VCTRLを受け取り、そして第1電流I1と第2電流I2とを発生する。電流増幅器は、第1電流を増幅しそしてフィルタし、そして第3電流I3を発生する。総和器は、第2電流と第3電流を合算し、そして制御電流を発生する。ICOは、制御電流CTRLを受け取り、そして制御電流により決定される周波数を有するオシレータ信号を発生する。

(もっと読む)

PLL

【課題】ジッタが抑制されたPLLを提供する。

【解決手段】PLLは,基準クロックとフィードバッククロックとの位相差信号を遅延し,異なる時間遅延させた位相差信号に応じてチャージ電流を生成する複数のチャージポンプCPを有す。また当該複数のチャージポンプが生成するチャージ電流を加算して出力するチャージポンプ等化器と,ループフィルタと電圧制御発振器の理想特性を持ち,位相差信号の位相差を有する位相差デジタル値を入力して理想特性に基づいてレプリカ出力を生成するレプリカ回路10と,レプリカ出力と理想出力との誤差信号と前記位相差信号との相関値を平滑化してチャージポンプ係数を生成し,複数のチャージポンプそれぞれに負帰還する係数生成回路20−1とを有し、複数のチャージポンプはチャージポンプ係数に応じた電流値を持つチャージ電流をそれぞれ生成する。

(もっと読む)

発振器及び半導体集積回路装置

【課題】発振器の出力端子間に直接寄生する容量Cparaの大きさが無視できない場合でも温度特性を補償する発振器及び発振器を内蔵する半導体集積回路装置を提供する。

【解決手段】インダクタンス素子Lと、容量素子Cと、増幅器30と、をそれぞれ第1の端子と第2の端子との間に並列に接続し、インダクタンス素子と容量素子とによって生じる共振を増幅器によって増幅し、第1の端子と第2の端子とから出力する発振器であって、第1の端子と第2の端子との間にインダクタンス素子の寄生抵抗RLより抵抗値の大きな第1の抵抗素子Rcが第1の端子と第2の端子との間に容量素子と直列に接続されている。

(もっと読む)

半導体装置

【課題】クロック生成回路からクロック信号を受けるドライブ回路の経年劣化を抑制する。

【解決手段】半導体装置1は、クロック信号INT1−SIGを生成して出力するクロック生成回路2と、クロック生成回路2からクロック信号INT1−SIGを受けるドライブ回路3とを備え、クロック生成回路2は、クロック信号INT1−SIGを生成して出力ノード2aから出力するクロック出力モードと、出力ノード2aの電位をハイレベルに固定する第1のクロック停止モードと、出力ノード2aの電位をロウレベルに固定する第2のクロック停止モードとを有する。

(もっと読む)

半導体装置

【課題】レプリカ回路の精度を抜本的に向上する。

【解決手段】半導体装置10は、少なくともフィードバッククロック信号RCLK1に基づいて外部クロック信号CK,/CKを遅延させてなる内部クロック信号RLCLKを出力するDLL回路70と、内部クロック信号RLCLKに同期してデータを出力する複数の出力バッファ64aと、出力バッファ64aのレプリカであり、内部クロック信号RLCLKに同期してフィードバッククロック信号RCLK1を生成し、DLL回路70に供給する出力レプリカ73と、DLL回路70から内部クロック信号RLCLKを受け、複数の出力バッファ64a及び出力レプリカ73に伝送するクロックツリー72とを備え、クロックツリー72は、それぞれDLL回路70から複数の出力バッファ64a及び出力レプリカ73に至る内部クロック信号RLCLKの複数の伝送経路の信号線負荷が互いに実質的に等しくなるよう構成される。

(もっと読む)

半導体装置

【課題】CMOSトランジスタによって構成されたVCOを備えた半導体装置において、発振信号の発振振幅のばらつきの抑制および低消費電力化を実現する。

【解決手段】VCO30は、CMOSトランジスタによって構成されたLCタンクVCOと、VCOの発振周波数帯域から一の発振周波数を選択するための周波数選択信号を生成する自動周波数選択回路42と、VCOの制御電圧を生成するPLL32と、周波数選択信号に基づいて差動型のMOSトランジスタのゲートに供給するバイアス電圧を調整するバイアス回路50とを備える。

(もっと読む)

半導体集積回路および無線通信装置

【課題】小規模かつ低消費電力で発振信号を生成可能な半導体集積回路およびこれを用いた無線通信装置を提供する。

【解決手段】半導体集積回路は、デジタル制御発振器と、カウンタと、時間デジタル変換器と、加算器と、制御信号生成部と、を備える。時間デジタル変換器は、発振信号と参照信号との位相差に対応する第3のデジタル信号を生成する。前記時間デジタル変換器は、分周器と、複数のインピーダンス素子と、位相差検出部と、を有する。分周器は、前記発振信号を分周して複数の分周信号を生成する。複数のインピーダンス素子は、前記複数の分周信号を分圧して、前記発振信号を遅延させた複数の遅延信号を生成する。位相差検出部は、前記参照信号と、前記複数の遅延信号のそれぞれと、を比較することにより、前記参照信号と前記発振信号との位相差に対応する前記第3のデジタル信号を出力する。

(もっと読む)

半導体集積回路

【課題】 半導体集積回路の外部に接続される半導体チップのプロセス状態を検出して、マスク解除信号に対する制御信号のセットアップ時間またはホールド時間のマージンを大きくする。

【解決手段】 モニタモード中に、通常より低い参照電位を受信回路に供給して伝送信号の論理レベルを判定することで、半導体集積回路の外部に接続される半導体チップのプロセス状態を検出する。検出したプロセス状態に応じて可変遅延回路を制御し、内部同期信号および外部同期信号の少なくともいずれかの遅延時間を調整する。これにより、内部同期信号に応じて生成されるマスク解除信号に対する半導体チップからの制御信号のセットアップ時間またはホールド時間を、半導体チップのプロセス状態に拘わらず一定にできる。

(もっと読む)

位相調整回路及び位相調整方法

【課題】消費電力を低減し、かつ回路面積も小さい位相調整回路を提供すること

【解決手段】位相調整回路100は、複数の遅延素子回路121〜124をリング状に結合したVCO120を有するPLL発振回路100を備える。また位相調整回路100は遅延素子回路を所望の遅延量に応じた数(125〜127)だけ有し、入力信号に前記所望の遅延量を与える位相遅延回路200、210を備える。PLL発振回路100は基準クロックの入力に応じた基準信号に、基準信号の所定周期分の遅延を与えた発振信号をVCO120において生成する。PLL発振回路100は、基準信号と、発振信号に応じた信号と、が略同位相となるように算出された遅延量に応じた遅延制御信号を遅延素子回路121〜124、及び遅延素子回路125〜127の各々に対して入力する。

(もっと読む)

1 - 20 / 197

[ Back to top ]