Fターム[5J106LL00]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 図面 (361)

Fターム[5J106LL00]の下位に属するFターム

発振回路,VCO (115)

位相比較(弁別)回路 (81)

周波数比較(弁別)回路 (13)

フィルタ回路 (45)

同期化クロック制御回路 (17)

可変分周回路、可変カウンタ (21)

同期・非同期検出回路 (13)

機械的構造 (49)

Fターム[5J106LL00]に分類される特許

1 - 7 / 7

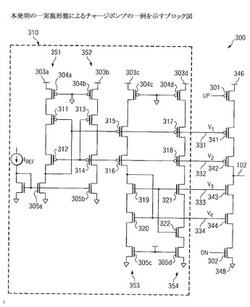

カスコードバイアスされたチャージポンプ

【課題】チャージポンプの線形動作範囲を広くする。

【解決手段】一実施形態によるチャージポンプは、アップ(UP)信号を受け取り、そのUP信号の受け取りに応答して正の電源から出力ノードに対応する出力電流を送るように動作可能な第1の入力トランジスタを含む。このチャージポンプは、ダウン(DN)信号を受け取り、そのDN信号の受け取りに応答して、第2の対応する出力電流を負の電源から出力ノードに送るように動作可能な第2の入力トランジスタをさらに含む。また、このチャージポンプは、第1の入力トランジスタと出力ノードとの間の第1の電流経路に配置された第1のカスコードトランジスタと第2のカスコードトランジスタを含み、第2の入力トランジスタと出力ノードとの間の第2の電流経路に配置された第3のカスコードトランジスタと第4のカスコードトランジスタを含む。このチャージポンプは、第1、第2、第3及び第4のカスコードトランジスタのゲートに結合した電流ミラーをさらに含む。

(もっと読む)

PLL回路

【課題】従来のPLL回路は、位相オフセットが発生する問題があった。

【解決手段】本発明にかかるPLL回路は、基準クロック信号と帰還クロック信号との位相差に基づきアップ信号及びダウン信号を出力する位相比較回路10と、アップ信号及びダウン信号のパルス幅を補正して補正アップ信号及び補正ダウン信号を出力するオフセット補正回路11と、補正アップ信号及び補正ダウン信号に基づいて出力電圧を上昇又は下降させる第1のチャージポンプ回路12と、当該出力電圧の電圧値に応じて発振周波数が制御される出力クロック信号を出力する電圧制御発振回路14とを有し、オフセット補正回路11は、基準クロック信号と帰還クロック信号との位相が揃っているときにチャージポンプ出力電圧が略一定の値となるように補正アップ信号及び補正ダウン信号のうち少なくとも一方のパルス幅を設定することを特徴とするものである。

(もっと読む)

位相変調器及びルビジウム原子発振器

【課題】クワッドレチャ・ハイブリッドを使用して、進相端子と遅相端子に可変リアクタ

ンス素子を接続することにより、所望する位相に変調すると共に、出力レベルの変動を最

小限に抑えた位相変調器を提供する。

【解決手段】この位相変調器11は、発振信号VIを発振する発振源24と、発振源24

から発振された発振信号VIを入力する入力端子aと、発振信号VIの位相に対して位相

が進む進相端子cと、発振信号VIの位相に対して位相が遅れる遅相端子bと、進相端子

cに現れる位相と遅相端子bに現れる位相とを合成して出力する出力端子dと、を有する

クワッドレチャ・ハイブリッド30と、可変容量素子C3と、可変容量素子C4と、出力

端子dと、を備えて構成されている。

(もっと読む)

チャージポンプ及びPLL回路

【課題】チャージポンプ回路のスイッチングトランジスタを大振幅の制御信号で駆動すると、ソース、ドレインの寄生容量、ゲート電極下のチャンネル電荷により、出力電流に乱れが生じる。特にチャージポンプの出力電流が小さい場合顕著になる。

【解決手段】電流源10,11の出力をスイッチングするための差動構成の差動スイッチング回路12,13を設け、差動スイッチング回路12,13を構成するトランジスタのゲートにかかる論理振幅を振幅制限/減衰回路14,15を用いて小さくすることで、寄生容量、チャンネル電荷による出力電流の乱れを改善する。

(もっと読む)

位相調整回路

【課題】データレートの高低にかかわらずデータ信号と遅延クロック信号との位相関係を最適に調整する位相調整回路を実現する。

【解決手段】離散的にデータ信号Dataとクロック信号CLKとの位相を調整する位相調整回路は、クロック信号CLKを遅延させて遅延クロック信号Rclkを生成する遅延線(10A)、データ信号Dataと遅延クロック信号CLKとの位相を比較する位相比較器(20)、位相比較器(20)の比較結果に基づいて、遅延制御信号SSxを出力する遅延制御部(30)、クロック信号CLKの周波数に基づいて、遅延制御信号RSxを出力する遅延制御部(40A)を備えている。ここで、遅延線(10A)は、制御信号に基づいて、クロック信号に対する遅延クロック信号の遅延量を決定する。

(もっと読む)

デジタルとアナログ制御を用いた電圧制御遅延ラインの遅延セル

【課題】デジタル制御方法とアナログ制御方法を混合して動作範囲を極大化する、デジタルとアナログ制御を用いた電圧制御遅延ラインの遅延セル回路を提供する。

【解決手段】本発明は、差動入力クロック信号が印加される差動入力トランジスタと、電源供給端に一方端が接続され、アナログ制御電圧に応答してファイン遅延量を調節するためのアナログ制御トランジスタ部と、前記アナログ制御トランジスタ部と前記差動入力トランジスタとの間に接続され、デジタルコードに応答してコース遅延量を調節するためのデジタル制御トランジスタ部とを備える。

(もっと読む)

クロック発生回路及びクロック発生方法

【課題】スペクトラム拡散クロックを発生し、参照クロック信号及び出力クロック信号の高精度な位相の制御を行うことが可能なクロック発生回路及びクロック発生方法を提供すること。

【解決手段】

入力分周部70は、入力クロック信号CLKRを50分周して、分周入力クロック信号CLKSを出力する。DLL回路80は、遅延制御信号DCS1、DCS2を求める動作を行う。変調回路40は、遅延制御信号DCS1、DCS2および変調制御回路50から出力される変調信号MODに応じて、分周入力クロック信号CLKSを変調し、変調クロック信号CLKNを出力する。位相比較器11は、変調クロック信号CLKN及び分周内部クロック信号CLKMの位相差を検知する。クロック生成部20は、位相比較器11の位相差信号に応じた周波数の出力クロック信号CLKOを生成する。

(もっと読む)

1 - 7 / 7

[ Back to top ]