Fターム[5J106LL01]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 図面 (361) | 発振回路,VCO (115)

Fターム[5J106LL01]に分類される特許

1 - 20 / 115

自励発振型D級アンプおよび自励発振型D級アンプの自励発振周波数制御方法

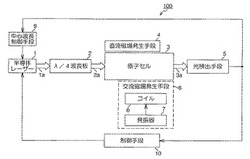

原子発振器

【課題】磁気量子数mF=0におけるEIT信号のピーク値を高くした原子発振器を提供する。

【解決手段】本発明の原子発振器100は、アルカリ金属原子に電磁誘起透過現象を発現させるための第1の共鳴光、及び第2の共鳴光を発生する半導体レーザー(光源)1と、半導体レーザー1から発生した共鳴光1aを円偏光するλ/4波長板2と、アルカリ金属原子が封入された原子セル3と、原子セル3から出射した共鳴光3aの強度を検出する光検出手段5と、アルカリ金属原子に所定の強度の直流磁場を与える直流磁場発生手段4と、直流磁場の強度に応じた所定の周波数の交流磁場をアルカリ金属原子に与える交流磁場発生手段8と、光検出手段5から出力された共鳴光の中心波長を制御する中心波長制御手段9と、アルカリ金属原子にEIT現象を発現させるように、第1の共鳴光と第2の共鳴光との周波数差を制御する制御手段10と、を備えて構成されている。

(もっと読む)

ディジタル制御発振装置および高周波信号処理装置

【課題】発振周波数遠方の雑音を低減することが可能なディジタル制御発振装置、ならびに高周波信号処理装置を提供する。

【解決手段】例えば、複数の単位容量ユニットCIU[1]〜CIU[k]を用いて分数容量を実現する。CIU[1]では、容量素子CFXp[1],CFXm[1]の一端がそれぞれ発振出力ノードOscP,OscMに接続される。一方、CIU[2]〜CIU[k]では、容量素子CFXp([2]〜[k]),CFXm([2]〜[k])の一端が固定電圧V6に接続される。CIU[1]〜CIU[k]の一方の容量素子の他端は共通接続され(SWFD)、他方の容量素子の他端も共通接続される(SWFS)。そして、CIU[1]〜CIU[k]内の各スイッチ(SWF1〜SWF3)のオン・オフは共通に制御される。

(もっと読む)

PLL回路

【課題】Trackingバンクの最小1bit以下の周波数分解能を実現でき、かつC/N特性の劣化を防止できるPLL回路を提供することを目的とする。

【解決手段】PLL回路101は、デジタル信号の値で周波数を離散的に調整し、微小周波数を1のアナログ信号の電圧値で調整し、所望の周波数の出力信号を出力する発振器10と、基準信号と発振器10の出力信号との位相差及び周波数差を表すデジタル値を出力する比較器11と、比較器11の出力するデジタル値を複数のデジタル信号として出力するループフィルタ44と、ループフィルタ44が出力する前記デジタル信号のうち発振器10で微小周波数の調整に対応する1のデジタル信号が直接入力され、入力されたデジタル信号をアナログ信号に変換するデジタルアナログ変換器13と、デジタルアナログ変換器13からのアナログ信号の高周波成分を除去するローパスフィルタ14と、を備える。

(もっと読む)

無線通信装置

【課題】周波数シンセサイザによる周波数信号を用いる無線通信装置の消費電力を低減する。

【解決手段】受信部が、受信した無線信号に基づく信号と周波数信号とを混合する第1ミキサと、当該第1ミキサの出力とローカル信号とを混合する第2ミキサと、当該第2ミキサの出力を復調して復調信号を生成する復調段とを含み、周波数シンセサイザが、制御入力電圧の変動に応じた周波数の周波数信号を生成するVCOと、当該VCOの出力周波数信号を分周して得られた信号と基準クロック信号との位相差に応じた電圧を制御入力電圧とするフィードバック回路と、からなり、当該VCOは、バイアス電流が大となるほど高い周波数で動作可能となる可変周波数発振器であって、当該バイアス電流が当該モード指定に応じて制御される無線通信装置。

(もっと読む)

位相同期回路および無線通信装置

【課題】周波数補正ミスをなくせ、電圧対周波数変換利得Kvcoを低く抑えることが可能で、PLL位相ノイズ設計を緩和できる位相同期回路および無線通信装置を提供する。

【解決手段】キャリブレーション部190は、電圧制御発振器184の出力発振信号の周波数をカウントするカウンタ回路191と、カウンタ回路のカウント結果を保持しておくための第1および第2の記憶回路193,194と、カウンタ回路とターゲット周波数を比較し大小を判定する比較回路195と、比較回路の結果を受けカウンタ回路のカウント結果と第1の記憶回路の保持結果を比較し、電圧制御発振器の容量バンクを制御する制御回路106と、電圧制御発振器にキャリブレーション電圧を生成し与える電圧生成回路197と、カウンタ回路のカウント結果と第1および第2の記憶回路の結果より演算を行い、演算結果に応じて電圧生成回路を制御する処理回路198と、を含む。

(もっと読む)

発振器アレー

【課題】周波数、位相差が同期された発振器アレーにおいて、構成の簡素化、低コスト化を実現すること。

【解決手段】発振器アレーは、1次元アレー状に接続されたN個(Nは2以上の自然数)のプッシュプッシュ発振器1と、プッシュプッシュ発振器1間にそれぞれ挿入された(N−1)個の非対称結合回路2と、によって構成されている。非対称結合回路2は、一方の端子Aからの信号入力に対する反射特性と、他方の端子Bからの信号入力に対する反射特性とが異なる非対称な特性を有した複共振接合回路である。端子Aから入力される信号は、その信号の大部分を一定の反射係数で反射されて再び端子Aから出力され、残りの一部分は透過して端子Bから出力され、周波数同期を行う。一方、端子Bから入力される信号は、反射係数が一定量変化されて反射され、端子Bから出力される。

(もっと読む)

CDR回路

【課題】入力データと再生クロックの確実な同期と再生クロックの適切なジッタ低減とを両立させる。

【解決手段】CDR回路は、入力データが遷移したときにパルスを出力するゲーティング回路2と、ゲーティング回路2の出力パルスのタイミングに合うように出力クロックの位相を調整するG−VCO3と、G−VCO3から出力されるクロックのタイミングに合うように出力クロックの位相を調整するVCO4と、入力データのデータ識別をVCO4から出力される再生クロックに基づいて行うフリップフロップ1と、G−VCO3の出力端子とVCO4の入力端子との間に設けられたバッファ増幅器6aとを備える。バッファ増幅器6aは、外部から入力される駆動力制御信号に応じて駆動力が調整される駆動力調整機能付きバッファ増幅器である。

(もっと読む)

CDR回路

【課題】入力データと再生クロックの同期を保ったまま、再生クロックの適切なジッタ量と適切なバースト応答時間とを両立させる。

【解決手段】CDR回路は、入力データが遷移したときにパルスを出力するゲーティング回路2と、ゲーティング回路2の出力パルスのタイミングに合うように出力クロックの位相を調整するG−VCO3と、G−VCO3から出力されるクロックのタイミングに合うように出力クロックの位相を調整するVCO4と、入力データのデータ識別をVCO4から出力される再生クロックに基づいて行うフリップフロップ1と、G−VCO3の出力端子とVCO4の入力端子との間に設けられたバッファ増幅器6aとを備える。バッファ増幅器6aの駆動力は、CDR回路のバースト応答時間が仕様の範囲内で最大となるように予め設定される。

(もっと読む)

温度特性調整データ生成方法

【課題】n(nは1以上の整数)次の関数で表現される温度特性を持った信号のn−1次の温度係数を調整する際に、n次の温度係数の影響を軽減し、且つコストの増大を抑えることができる、温度特性の調整データを生成する方法を提供する。

【解決手段】温度特性調整データ生成方法は、n(nは1以上の整数)次の関数で表現される温度特性を持った信号を生成する回路を有する半導体装置の温度特性を調整するデータ(803)を、プログラム処理装置(6、10)を用いて生成する方法であって、n+1よりも少ない数の温度における前記信号の値を、前記信号に関する目標値に所定の補正値を加えた値(601)に近づけるように温度特性を調整するデータを生成するデータ生成処理を含む。

(もっと読む)

CDR回路

【課題】MACからの制御信号なしでも瞬時に入力データとの同期を確立し、周波数安定度が高くジッタの少ない再生クロックを生成する。

【解決手段】CDR回路は、入力データ4が遷移したときにパルスを出力するゲーティング回路10と、ゲーティング回路10の出力パルスのタイミングに合うように再生クロック7の位相を調整することにより、入力データ4とタイミングの合った再生クロック7を出力するVCO11と、入力データ4のデータ識別を再生クロック7に基づいて行うフリップフロップ3と、ゲーティング回路10とVCO11との間に設けられた、所望のデータレート周波数の信号を通過させるバンドパスフィルタ40とを備える。

(もっと読む)

CDR回路

【課題】周波数安定度が高くジッタの少ない再生クロックを生成する。

【解決手段】CDR回路は、入力データ4が遷移したときにパルスを出力するゲーティング回路10と、位相同期ループ中に配置されたVCO12と、ゲーティング回路10の出力パルスのタイミングに合うように再生クロック7の位相を調整することにより、入力データ4とタイミングの合った再生クロック7を出力するG−VCO13と、入力データ4のデータ識別を再生クロック7に基づいて行うフリップフロップ3とを備える。入力データ4のデータレートと等しい周波数の参照クロック5またはVCO12の出力クロックは、注入信号9としてG−VCO13に入力される。

(もっと読む)

位相同期発振装置

【課題】 小さいばらつきで電圧制御回路から供給される温度補償された電圧によって制御される電圧制御発振器を介して接続された増幅器の出力電力を、精度良く増減させ出力端子から出力する位相同期発振装置を得る。

【解決手段】 発振周波数を制御する周波数制御電圧入力端子と発振電力を制御する電圧入力端子とを有する電圧制御発振器と、この電圧制御発振器から出力される高周波信号を増幅して出力する温度特性を有する増幅器と、温度センサを有し、この温度センサの出力信号で基準電圧から変化する電圧を前記電圧制御発振器の電圧入力端子に入力し、前記電圧制御発振器を介して前記増幅器の電力非飽和領域の電力を増減する電圧制御回路とを備えている。

(もっと読む)

可変インダクタ、電圧制御発振器、複合型PLL回路、フィルタ回路および増幅回路

【課題】制御電圧入力端子の個数を減少させることができる新規な可変インダクタならびにその新規な可変インダクタを備える電圧制御発振器、複合型PLL回路、フィルタ回路および増幅回路を提供する。

【解決手段】本発明の可変インダクタ5においては、複数のインダクタンス素子61、62、63、64におけるそれぞれの接続点とグランド10との間にそれぞれ接続された複数のスイッチダイオード7A、7B、7Cのそれぞれの一端側に対して、複数の定電圧入力端子8A、8B、8Cを介して、互いに異なる定電圧がそれぞれ供給されている。また、本実施形態の可変インダクタ5においては、複数のスイッチダイオード7A、7B、7Cにおけるそれぞれの他端側に対して、1個の制御電圧入力端子9を介して、制御電圧が供給されている。

(もっと読む)

送信回路、集積回路装置及び電子機器

【課題】安定したデータ送信ができる送信回路、集積回路装置及び電子機器等を提供すること。

【解決手段】送信回路100は、電圧制御発振回路190を有し、搬送波の信号を生成するPLL回路110と、送信データDTXに基づいて、電圧制御発振回路190の変調用制御電圧信号入力ノードNBに対して、変調用制御電圧信号VMを出力する変調用制御電圧生成回路120と、電圧制御発振回路190の出力信号を増幅するパワーアンプ210とを含む。変調用制御電圧生成回路120は、送信データ出力期間の前の擬似信号出力期間に、擬似制御電圧信号を変調用制御電圧信号VMとして出力する。

(もっと読む)

送信機および通信システム

【課題】周波数の変化に対応でき、且つクロストークに起因するジッターの低減を図ることができる送信機、および通信システムを提供する。

【解決手段】送信機2は、発振回路4と、送信部5とを備える。発振回路4は、基準クロックCKrefを入力して、同一の周期を有すると共に位相が互いに異なるN相(Nは2以上の整数)のクロックCK1〜CKNを生成して出力する。送信部5は、発振回路4から出力されたクロックCK1〜CKNを入力して、このクロックCKn(nは1以上N以下の各整数)にシリアルデータ信号Snを同期させて高速シリアル伝送線路Lnを介して受信機3に送信する。

(もっと読む)

PLL周波数シンセサイザ

【課題】電圧制御発振器のゲイン特性の変動を抑制する。

【解決手段】電圧制御発振器11は、インダクタ100と、微調整コンデンサ101pと、粗調整コンデンサ102pとを含み、発振クロックCKoutを生成する。分周器12は、発振クロックCKoutを分周して分周クロックCKdivを生成する。直流電圧供給回路13は、粗調整モードにおいて、直流電圧V13を制御ノードNiに供給するとともに発振電圧VPの直流値に応じて直流電圧V13の電圧値を変化させる。周波数帯域選択回路14は、粗調整モードにおいて、電圧制御発振器11の発振周波数帯域が目標周波数に対応する発振周波数帯域に設定されるように、基準クロックと分周クロックとの周波数差に基づいて粗調整コンデンサ102pの容量値を切り替える。発振制御回路15は、微調整モードにおいて、基準クロックと分周クロックとの位相差に応じて制御電圧VTを増減させる。

(もっと読む)

復調器および通信装置

【課題】高精度に復調処理を行う。

【解決手段】復調器30Aの局部発振器70は、変調器10から送信されて注入される変調信号SRFの局部発振周波数に局部発振信号SLOの周波数を同期させ、同期させた局部発振信号SLOをミキサ40に出力する。ミキサ40は、同期した局部発振信号SLOと変調器10から送信される変調信号SRFとを掛け算して復調信号SDMを生成する。このとき、局部発振信号SLOと周波数同期した変調信号SRFとの間の位相差に応じて復調信号SDMにDC成分が発生する。DC補正部50は、復調信号SDMのDC電圧Vdcを検出し、検出したDC電圧Vdcが予め設定されている基準電圧となるように補正する。

(もっと読む)

電圧制御発振器のための補償回路

【課題】電圧制御発振器のための補償回路を提供する。

【解決手段】電圧制御発振器(VCO)の電圧を制御するために使用され得る回路は、第1の比較器、第2の比較器、アキュムレータ、及び出力装置を備え得る。第1の比較器は、制御電圧が高電位側しきい値電圧より高い場合に第1のパルス信号を出力する。第2の比較器は、制御電圧が低電位側しきい値電圧より低い場合に第2のパルス信号を出力する。アキュムレータは、もし第1のパルス信号が受信されるならばスイッチ制御信号の値を増加させ、もし第2のパルス信号が受信されるならばスイッチ制御信号の値を減少させる。出力装置は、スイッチ制御信号の値に応じてVCOの制御電圧を補償する補償電圧を生成する。

(もっと読む)

サプライレギュレートされたフェイズロックループ(PLL)及び用いる方法

サプライレギュレートされたフェイズロックループ(PLL)が提供される。PLLは、サプライレギュレーティングループ、電圧制御発振器(VCO)、及びVCOのためのプログラマブルデカップリングキャパシタアレイを備える。VCOデカップリングキャパシタアレイのキャパシタンスは、NかけるCUNITに等しくなるように調整可能であり、NはN分周回路の乗算ファクタの現在の値であり、CUNITはデカップリングキャパシタアレイを製造するために選ばれたプロセス技術に対して特徴付けられたユニットキャパシタンスである。PLLが1つの周波数帯から他にスイッチするとき、VCOデカップリングキャパシタによって導入される高次ポールがPLL参照周波数をトラックし、PLLの動作安定性を改善する。  (もっと読む)

(もっと読む)

1 - 20 / 115

[ Back to top ]