Fターム[5J500AC26]の内容

増幅器一般 (93,357) | 目的、効果 (9,357) | 歪低減(直線性改善を含む) (1,554) | 位相歪の低減(位相補償を含む) (154)

Fターム[5J500AC26]に分類される特許

1 - 20 / 154

リニアライザ

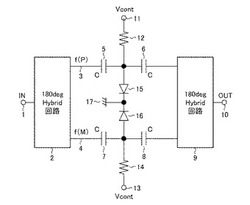

【課題】ダイオードから見るインピーダンスが変化しても、利得特性と位相特性の単調変化を実現することができるリニアライザを得ることを目的とする。

【解決手段】アノードが信号路3に接続されて、順方向に電圧が印加されているダイオード15と、アノードが信号路4に接続されて、順方向に電圧が印加されているダイオード16とを備え、ダイオード15のカソードとダイオード16のカソードとの接続点がバイアス接地用ビアホール17に接地されている。

(もっと読む)

チョッパ式増幅回路

【課題】従来のチョッパ式増幅装置は、チョッパクロックに同期したチョッパノイズを除去するために、チョッパノイズが重畳しない期間の電圧を保持しておき、保持しておいた電圧を出力するために、入力電圧と出力電圧の位相がずれてしまう。

【解決手段】出力側スイッチ回路18で復調した電圧を、チョッパクロックの反転前の値をチョッパクロックの反転後まで保持するサンプルホールド回路20,22で保持する。チョッパノイズの影響をサンプルホールド回路20,22で除去できる。前段チャージアンプと後段チャージアンプで増幅回路を構成することが好ましく、保持時間を短くすることができる。帰還抵抗を大きくすることで出力電圧の変動率を低減できる。5%以下の変動率とする抵抗値を用いることが好ましい。

(もっと読む)

誤差増幅回路及びスイッチングレギュレータ

【課題】位相補償回路を内蔵する誤差増幅回路と比較して、回路規模及び回路の消費電流を大きくすることなく、位相補償容量を外付けにすることができる誤差増幅回路及び当該誤差増幅回路を用いたスイッチングレギュレータを提供する。

【解決手段】所定の基準電圧Vref1と入力電圧Vfb1との誤差を増幅して出力する誤差増幅器12と、誤差増幅器12にバイアス電流Ibias1を供給する電流生成回路11とを含む集積回路10を備えた誤差増幅回路10aにおいて、集積回路10は、電流生成回路11に接続されたバイアス電流制御端子T1と、位相補償抵抗14を介して誤差増幅器12の出力端子T11に接続された位相補償端子T2とを備え、誤差増幅回路10aは、位相補償端子T2に接続された位相補償容量30を集積回路10の外部に備える。

(もっと読む)

増幅回路

【課題】ドレインバイアスノードの電位を変化させた場合に、信号通過位相の変化を抑制することを課題とする。

【解決手段】増幅回路は、一次側インダクタが入力端子に接続され、二次側インダクタの中点がゲートバイアスノードに接続されるトランスフォーマー回路(101)と、ゲートが二次側インダクタの一端に接続され、ドレインが第1の出力端子に接続される第1のトランジスタ(104)と、ゲートが二次側インダクタの他端に接続され、ドレインが第2の出力端子に接続される第2のトランジスタ(105)と、第1の出力端子及びドレインバイアスノード間に接続される第1のインダクタ(110)と、第2の出力端子及びドレインバイアスノード間に接続される第2のインダクタ(111)と、トランスフォーマー回路の二次側インダクタに並列に接続され、ドレインバイアスノードの電位に応じて容量値が変化する可変容量(301,302)とを有する。

(もっと読む)

増幅器の位相補償回路及び増幅回路

【課題】増幅器の位相補償精度を向上させることができる増幅器の位相補償回路を提供することを課題とする。

【解決手段】増幅器の位相補償回路は、入力端子及び第1のノード間に接続される第1の容量(404)と、前記第1のノード及び第1の増幅器の入力端子間に接続される第2の容量(405)と、ゲートが前記第1のノードに接続され、ソース及びドレインが第1の電位ノードに接続される第1の電界効果トランジスタ(406)と、前記入力端子の信号のエンベロープを検出するエンベロープ検出回路(411,412)と、前記エンベロープ検出回路により検出されたエンベロープを増幅し、前記第1のノードに出力する第2の増幅器(413)とを有する。

(もっと読む)

無線通信装置

【課題】消費電力を低減した無線通信装置を提供する。

【解決手段】送信信号をデジタル形式からアナログ形式に変換するD/A変換器12と、D/A変換器12から出力される送信信号を増幅して出力する増幅器14と、増幅器14から出力される増幅後の送信信号をアナログ形式からデジタル形式に変換するA/D変換器19と、増幅後の送信信号を受け、歪み補償を行う歪補償部5と、増幅後の送信信号における歪補償すべき帯域を検出する歪帯域検出部7とを備え、歪帯域検出部7で検出された歪補償すべき帯域に基づいて、D/A変換器12およびA/D変換器19のサンプリング周波数を制御する。

(もっと読む)

トランスインピーダンスアンプおよびトランスインピーダンスアンプ接続回路

【課題】群遅延特性の入力光パワー依存性を低減し、かつ、ESD耐性を有するトランスインピーダンスアンプを提供する。

【解決手段】入力端子から入力される入力電流のインピーダンス変換を行うトランスインピーダンスアンプTIAとして第一の電源端子VCCTIAと第二の電源端子VEETIAとを有し、第一の電源端子VCCTIAには第二の電源端子VEETIAよりも高い電圧が印加され、かつ、第一の電源端子VCCTIAと第二の電源端子VEETIAとの間に、トランスインピーダンスアンプTIAと並列の電流パスを形成する第一の回路素子が接続されている。該第一の回路素子は、第一のダイオードもしくはダイオード列からなっている。

(もっと読む)

電力増幅器のメモリ効果キャンセラ、無線送信機

【課題】電力増幅器のメモリ効果を補償するときの計算量の増加を抑制できるようにすること。

【解決手段】メモリ効果キャンセラ100は、遅延器61、遅延器62−1〜62−Q、遅延器63−1〜63−Q、減算器65、演算器70−0〜70−Q、乗算器72−0〜72−Q、加算器75、及び信号変換部76を備える。演算器70−0〜70−Qはそれぞれ、送信信号のサンプルx[n]〜x[n-Q]と、差分信号のサンプルΔx[n]〜Δx[n-Q] とに基づいて、電力増幅器51の既知の伝達関数Fに対する各時刻のサンプルによる偏微分値を算出する。各偏微分値は所定の重み係数α0〜αQをもって線形結合されて、電力増幅器51の出力信号y’[n]に対して、メモリ効果を補償するための補正信号Δy[n]が生成される。

(もっと読む)

増幅特性情報を有する電力増幅装置及びその方法とそれを用いた前置歪みシステム及びその方法

【課題】電力増幅装置の前置歪みシステム及びその方法を提供する。

【解決手段】アナログ入力信号をディジタル信号に変換するためのアナログ−ディジタル変換部510と、電力増幅装置からの増幅特性情報を前置歪み計算部に伝達するための通信制御部550と、上記通信制御部からの増幅特性情報と上記アナログ−ディジタル変換部からの入力信号に基づいて上記増幅特性情報の逆増幅特性情報を計算するための上記前置歪み計算部560と、上記前置歪み計算部からの逆増幅特性情報に従って上記アナログ−ディジタル変換部からのディジタル入力信号を前置歪みさせるための前置歪み部520と、上記前置歪み部からのディジタル入力信号をアナログ信号に変換するためのディジタル−アナログ変換部530と、上記ディジタル−アナログ変換部からの信号を電力増幅して出力し、上記通信制御部に上記増幅特性情報を伝達するための上記電力増幅装置540と、を含む。

(もっと読む)

増幅器、及び通信装置

【課題】 少ない回路規模で位相特性を補償できる増幅器及び通信装置を提供する。

【解決手段】 正相入力信号を増幅して正相出力信号を生成し、逆相入力信号を増幅して逆相出力信号を生成する増幅器であって、正相入力信号を増幅して第1正相信号を生成し、逆相入力信号を増幅して第1逆相信号を生成する第1増幅回路と、正相入力信号を増幅して第2正相信号を生成し、逆相入力信号を増幅して第2逆相信号を生成する第1増幅部と、正相入力信号を増幅して第3正相信号を生成し、逆相入力信号を増幅して第3逆相信号を生成する第2増幅部を有する第2増幅回路と、を備え、正相出力信号が、第1正相信号と第2正相信号との和であり、逆相出力信号が第1逆相信号と第2逆相信号との和である、又は正相出力信号が、第1正相信号と第3逆相信号の和であり、逆相出力信号が第1逆相信号と第3正相信号との和であることを特徴とする増幅器を提供する。

(もっと読む)

半導体集積回路装置及び送受信システム

【課題】入力信号に対する増幅器の出力信号の利得特性を線形化するために必要な回路の面積を低減できる半導体集積回路装置及び送受信システムを提供する。

【解決手段】半導体集積回路装置は、切り替え可能な複数の第1の利得特性を有し、入力信号に対して前記第1の利得特性を切り替えて中間信号を生成し、第2の利得特性を有する回路に前記中間信号を出力する線形化回路を備え、前記線形化回路は、少なくとも1つの第1の整流素子を有し、前記入力信号を線形化する線形化器と、前記第1の整流素子と逆極性の複数の第2の整流素子と、制御信号に基づき前記複数の第2の整流素子のうち少なくとも1つを選択する第1の切り替え部とを有し、前記線形化器に並列に接続され、前記線形化器による前記入力信号の線形化を抑制する線形化抑制器とを備える。

(もっと読む)

マルチバンド電力増幅器

【課題】 インピーダンス不整合をなくしたマルチバンド電力増幅器を提供する。

【解決手段】 マルチバンド電力増幅器11の増幅器12,13間には、これらを整合させる段間整合回路14を設ける。また、入力段の増幅器12の入力側に入力段整合回路15を設けると共に、出力段の増幅器13の出力側には出力段整合回路16を設ける。そして、制御回路17は、基地局BSからの周波数設定情報Spによって第1,第2の送信信号TX1,TX2の通信周波数f11〜f1m,f21〜f2nを特定し、この特定した通信周波数f11〜f1m,f21〜f2nに応じて段間整合回路14、入力段整合回路15および出力段整合回路16のインピーダンス値Zm,Zi,Zoを最適な値に調整する。

(もっと読む)

変調アグノスティック(AGNOSTIC)デジタルハイブリッドモード電力増幅器のシステム及び方法

広帯域通信システムにおいて高効率性及び高線形性を実現するRFデジタルハイブリッドモード電力増幅器システムが開示される。本発明は、RF領域内の電力増幅器を線形化する適応デジタル予歪の方法に基づく。本開示により、電力増幅器システムはフィールド再構成可能となり、マルチ変調スキーム(変調アグノスティック)、マルチキャリア及びマルチチャネルをサポートできる。その結果、デジタルハイブリッドモード電力増幅器システムは、ベースバンドI−Q信号情報をすぐに入手することができない基地局、リピータ及び屋内信号カバレージシステムなどの無線伝送システムに特に適している。 (もっと読む)

歪補償回路及び歪補償方法

【課題】各動作点において非線形歪の逆歪特性と遅延歪の逆歪特性とを独立したパラメータとして設定でき、信号レベルを変化させても、最適な歪補償を行えるようにする。

【解決手段】動作点パラメータ算出部52及び53で、入力信号の電力値を基に、非線形歪及び遅延歪に対する動作点パラメータを独立して設定する。非線形逆歪特性発生部54及び遅延逆歪特性発生部55で、動作点パラメータ算出部52及び53からの動作点パラメータに応じて、非線形逆歪特性及び遅延逆歪特性を発生させ、補償係数算出部56で補償係数を算出させ、複素乗算器57で入力信号に複素乗算する。非線形歪及び遅延歪に対する動作点パラメータを独立して設定できるので、信号レベルが変化した場合でも、非線形歪と遅延歪とを最適に補償することができる。

(もっと読む)

送信回路及び通信機器

【課題】AM/PM歪みを補償し、低歪みかつ高効率に動作する送信回路を提供する。

【解決手段】補償部22は、LPF14,15を通過したIPL、QPL信号のベクトルの大きさを示す振幅信号Mを算出することで、IP',QP'信号がLPF12,13を通過することによって発生する高周波信号Piの包絡線の変動を予測する。補償部22は、算出した振幅信号Mに基づいて、位相補償量θcompを算出し、位相信号θに位相補償量θcompを加算する。

(もっと読む)

増幅装置

【課題】増幅器の振幅歪み、位相歪みを補償する手段を備えることで、高効率で、かつ低歪みな増幅装置を得る。

【解決手段】変調波入力信号を増幅する高周波電力増幅器7と、前記変調波入力信号から包絡線信号を検出する第1の包絡線検出器3と、前記高周波電力増幅器の出力信号を検出する出力信号検出手段100と、前記出力信号検出手段の出力から包絡線信号を検出する第2の包絡線検出器101と、第1と第2の包絡線検出出力を比較して誤差を検出する比較器12と、前記比較器からの誤差信号をデルタ変調するデルタ変調器40と、前記デルタ変調器の出力を増幅するスイッチング増幅器5と、前記スイッチング増幅器の出力を帯域制限する低域通過フィルタ6とを備え、前記高周波電力増幅器7は、前記低域通過フィルタ6の出力を電源電圧として、前記変調波入力信号を増幅する。

(もっと読む)

トラフィックの存在下で自己補償するマルチポート増幅装置

少なくとも、出力としてN個の分配信号を供給する入力バトラーマトリックス(301)に接続された複数(N個)の入力経路と、入力として前記分配信号を受信し、出力として各々複素利得GiのN個の増幅および位相シフトされた信号を生成する複数(N個)の真空管増幅器(303)と、入力として前記増幅信号を受信し、出力としてN個の出力信号を生成する出力バトラーマトリックス(305)とを備えた、通信信号のマルチ分布増幅システムであって、位相誤差および振幅誤差がトラフィックの存在下で自己補償されることを特徴とするシステム。 (もっと読む)

送信機およびそれに使用可能な半導体集積回路

【課題】振幅成分ρと位相成分θを合成する送信機の振幅成分と位相成分の間の遅延不整合を、高速かつ高精度に校正する。

【解決手段】送信機は、振幅信号経路にデジタル・アナログ変換器(DAC)107とローパスフィルタ(LPF)108を有し、位相信号経路に位相成分をRF成分にアップコンバートする位相変調器109を有する。振幅信号経路の遅延校正器201に遅延校正動作時に入力がテスト入力信号210に供給され、遅延校正器201はDACの入力にテスト入力信号210、213を供給して、LPFのテスト出力信号212が生成される。遅延校正器201はテスト入力信号210に対するテスト出力信号212の遅延を検出して、遅延校正器201の入力からLPFの出力までの振幅信号遅延を校正して、振幅信号遅延と位相信号経路の位相変調器(109)の位相信号遅延の差を低減する。

(もっと読む)

位相補償回路

【課題】位相補償の必要な各種回路に適用でき、大容量の位相補償キャパシタや複雑な回路を必要とせずに実現できる位相補償回路などの提供。

【解決手段】この発明に係る位相補償回路20は、複数のトランジスタがカスコード接続されるカスコード増幅回路(カスコード増幅段)10に設けられ、カスコード増幅回路10の位相補償を行う。位相補償回路20は、バッファアンプ21とキャパシタ22とを備え、これらは直列接続されて直列回路を構成する。その直列回路の入力側はカスコード増幅回路10の出力端子12に接続され、直列回路の出力側はカスコード増幅回路10の位相補償端子13に接続される。バッファアンプ21は、ソースフォロワ回路に置き換えできる。

(もっと読む)

差動AB級増幅回路、駆動回路および表示装置

【課題】位相余裕を向上することのできる差動AB級増幅回路、駆動回路および表示装置を提供する。

【解決手段】差動AB級増幅回路は、第1差動増幅器(11)と、第2差動増幅器(12)と、AB級出力回路(80)とを具備する。第1差動増幅器(11)は、差動入力信号を増幅して第1の電圧範囲の第1信号を出力する。第2差動増幅器(12)は、差動入力信号を増幅して第2の電圧範囲の第2信号を出力する。AB級出力回路(80)は、第1信号および前記第2信号を差動入力として増幅し、位相補償用容量および位相補償用容量に流れる電流を制御する電流バッファ回路を備える。

(もっと読む)

1 - 20 / 154

[ Back to top ]