Fターム[5J500AC27]の内容

増幅器一般 (93,357) | 目的、効果 (9,357) | 歪低減(直線性改善を含む) (1,554) | 高調波歪の低減(スプリアス除去を含む) (133)

Fターム[5J500AC27]に分類される特許

1 - 20 / 133

無線基地局装置及び無線基地局装置の送信増幅器消費電力制御方法

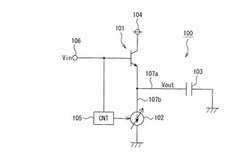

トランジスタ回路

【課題】少ない電流量で出力電圧の歪みを低減できるトランジスタ回路を提供する。

【解決手段】エミッタまたはソースと、コレクタまたはドレインと、これらエミッタまたはソース及びコレクタまたはドレイン間の電流量を制御する電圧が印加されるベースまたはゲートと、を備え、コレクタまたはドレインが容量性負荷103に接続されるバイポーラトランジスタまたはMOSトランジスタと、バイポーラトランジスタまたはMOSトランジスタのコレクタまたはドレインに接続され、電流を供給する機能付電流源102と、ベースまたはゲートに入力される電圧の大きさに応じて機能付電流源102の電流を制御するコントロール回路105と、によってトランジスタ回路を構成する。

(もっと読む)

増幅器

【課題】 携帯電話をはじめとする移動体通信用高周波電力増幅器などの増幅器において、受信帯雑音特性が良好で小型な増幅器を提供する。

【解決手段】 第一の周波数を中心周波数とする信号を増幅する増幅素子と、前記増幅素子の前段または後段に接続される整合回路と、前記増幅素子と前記整合回路の間に接続され、前記第一の周波数とは異なる第二の周波数を中心周波数とする信号を減衰させるフィルタ回路と、を備えたことを特徴とする。

(もっと読む)

EM級増幅器

【課題】高調波歪みを容易に低減させることのできるEM級増幅器を提供する。

【解決手段】本発明にかかるEM級増幅器は、主回路と、主回路に信号を入力する補助回路と、を有するEM増幅器であって、主回路は、プッシュプル構造を有することを特徴とする。この場合において、限定されるわけではないが、プッシュプル構造は、第一の主基礎回路と、第一の主基礎回路と同様な構造の第二の主基礎回路と、第一の主基礎回路と第二の主基礎回路に接続される負荷回路と、を有して構成される。

(もっと読む)

ディジタル・プリディストーション方式及び増幅装置

【課題】ディジタル・プリディストーション方式に関し、低次から高次まで高精度の歪補償を効果的に行うことが可能な技術を提案する。

【解決手段】

ダウンコンバータ6が、電力増幅部4からの信号の一部を分岐させた帰還信号をダウンコンバートし、A/D変換部7が、ダウンコンバータ6からの信号を入力信号のサンプリングレートより低いサンプリングレートでアナログからディジタルの信号に変換し、レート変換部8が、A/D変換部7からの信号のサンプリングレートを入力信号のサンプリングレートに変換し、低次歪算出部11が、レート変換部8からの信号に含まれる低次歪を算出し、高次歪生成部12が、低次歪算出部11により算出された低次歪から推定される高次歪をレート変換部8からの信号に付加し、歪補償制御部9が、高次歪生成部12からの信号と入力信号とを比較して、歪補償係数テーブル10を更新する。

(もっと読む)

スイッチングシステムおよびスイッチングシステムの制御方法

【課題】EMIを低減できるスイッチングシステムを提供する。

【解決手段】本発明は、スイッチングシステムを提供する。スイッチングシステムは、Hブリッジ、電流ルーターおよび制御回路を含む。Hブリッジは、第一出力ノードに結合される第一スイッチと第二スイッチおよび第二出力ノードに結合される第三スイッチと第四スイッチを含み、ロードは、第一出力ノードと第二出力ノード間に結合される。電流ルーターは、第一出力ノードと第二出力ノード間に結合される第一シャントスイッチと第二シャントスイッチを含む。制御回路は、第一制御信号を生成して、第一スイッチと第四スイッチを制御し、第二制御信号を生成して、第二スイッチと第三スイッチを制御し、第三制御信号を生成して、第一シャントスイッチを制御し、第四制御信号を生成して、第二シャントスイッチを制御する。

(もっと読む)

デブースト電流経路を有するマルチ線形性モードLNA

【課題】高利得、及び低電流消費と共に、非常に高い三次入力インターセプトポイント(IIP3)を有するLNAを提供する。

【解決手段】LNA222は、メイン電界効果トランジスタ(FET)302、キャンセルFET304、第1ソース・ディジェネレーション・インダクタ306、第2ソース・ディジェネレーション・インダクタ308、カスコード・トランジスタ310、及びLNA負荷312を含む。LNA負荷312は、並列に結合されたインダクタ314及びキャパシタ316を含むLCタンク回路である。

(もっと読む)

電力増幅装置

【課題】主信号の変調帯域と相互変調積の周波数範囲外となる周波数では高インピーダンスでスプリアス低減効果のある電力増幅装置を提供する。

【解決手段】実施形態によれば、入力信号を第1信号及び第2信号を含む伝送信号に電力増幅するFET103と、FET103から出力される伝送信号のインダクタ成分を低減する第1のデカップリング素子104と、FET103に対し駆動電力を供給する電源回路200と、電源回路200に対しFETの出力端子106から出力されるRF成分をカットする第2のデカップリング素子300と、第1のデカップリング素子104と第2のデカップリング素子300との間に接続され、第1信号の変調帯域とFETの出力信号における相互変調積の周波数領域では所定の第1インピーダンスで、第1信号の変調帯域と相互変調積の周波数領域外では第2インピーダンスを有するフィルタ400とを備える。

(もっと読む)

差動増幅器

【課題】出力電圧の出力精度に段差が発生していた。

【解決手段】電流源で駆動される第1、第2の差動対と、その電流源を駆動する第1の基準電流発生回路と、を備える第1の差動入力部と、電流源で駆動される第3、第4の差動対と、その電流源を駆動する第2の基準電流発生回路と、を備える第2の差動入力部と、前記第1、第2の差動入力部との出力に応じて、出力する出力部と、を有し、前記第1、第2の基準電流発生回路の第1、第2の電流経路上に接続される第1、第2のトランジスタを入力信号に応じて制御することで、前記第1、第2の差動入力部の出力を制御する差動増幅器。

(もっと読む)

信号変換回路ならびにそれを用いた増幅回路,送信装置および通信装置

【課題】 不要パルスの発生が抑制された信号変換回路ならびにそれを用いた増幅回路,送信装置および通信装置を提供する。

【解決手段】 第1信号S1がソース端子に、第2信号S2がゲート端子に入力されるトランジスタ7と、第1信号S1と第2信号S2とが入力されて、第1信号S1と第2信号S2との位相差の情報を有する第3信号S3を出力する第1回路5と、第1信号S1と第3信号S3とが入力されて、第1信号S1と第2信号S2との位相差に応じて第1信号S1の位相をシフトさせた位相を有する第4信号S4を出力する第2回路6と、ソース端子がトランジスタ7のドレイン端子に接続されているとともにゲート端子に第4信号S4が入力されて、第1信号S1と第2信号S2との位相差に応じてデューティ比が変化する第5信号S5をドレイン端子から出力するトランジスタ9とを有する信号変換回路とする。

(もっと読む)

電力増幅回路

【課題】電力増幅回路の周波数特性を広帯域化する。

【解決手段】それぞれが互いに異なる周波数(f1−fn)で整合が取られた差動プッシュプル増幅器(PA1−PAn)の出力を、二次インダクタ(L12−Ln2)で共通に合成して出力する。各差動プッシュプル増幅器は、差動信号入力端子にぞれぞれ接続される増幅器対で構成され、差動プッシュプル増幅器の出力にはキャパシタ(C1−Cn)とインダクタ(L11−L1n)の並列共振回路を接続し、共振周波数を変更して整合周波数を調整する。

(もっと読む)

歪補償装置、歪補償方法及び無線送信機

【課題】増幅器の出力信号に要求される規格を確実に満足する。

【解決手段】増幅器6の歪特性を補償する歪補償方法において、増幅器6に入力される入力信号と増幅器6から出力される出力信号のフィードバック信号との差分である誤差信号に所定の周波数特性を付与し、所定の周波数特性付与後の誤差信号に基づいて、増幅器6の歪特性を補償するための歪補償係数を演算し、演算した歪補償係数を用いて入力信号を歪補償処理する。

(もっと読む)

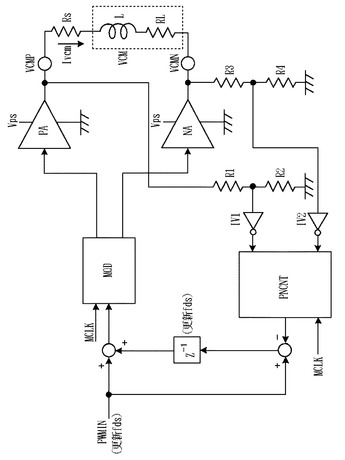

PWMアンプ

【課題】デットタイム歪みを補償したPWMアンプを提供する。

【解決手段】PWMアンプは、PWM入力信号を受け、デッドタイムを持つ第1駆動パルスと第2駆動パルスを形成するPWM駆動回路と、上記第1駆動パルスを受けて出力端子に第1出力電圧を出力させる第1出力素子と、上記第2駆動パルスを受けて上記出力端子に第2出力電圧を出力させる第2出力素子と、上記PWM入力信号と、かかるPWM入力信号に対応した上記第1出力素子と第2出力素子より形成された出力信号との誤差パルスを検出し、次に入力されるPWM入力信号に上記誤差パルスを加算させるデッドタイム補償回路とを有する

【選択図】図4  (もっと読む)

(もっと読む)

制御整合ステージを備える装置

【課題】比較的簡単な、制御整合ステージ、方法、およびプロセッサ・プログラム製品を提供する。

【解決手段】第1のステージに第2のステージを整合させるための制御整合ステージ10を備え、制御整合ステージは、第1のステージの出力信号から第1の信号と第2の信号とを導出するための導出手段11と、第1の信号と第2の信号の間の位相を検出するための検出手段12と、前記整合のために前記検出に応じて調整可能インピーダンス・ネットワーク14を制御するための制御手段13とを備える。

(もっと読む)

衛星信号生成ユニットによって生成された信号を増幅するためのシステム

【課題】スペクトル占有を制限できる増幅するシステムを提供する。

【解決手段】−有限インパルス応答を伴う第1の帯域通過デジタルフィルタF1および第1のデジタル/アナログコンバータCNA1を備える第1の経路V1と、−周波数置換手段MTFと、−増幅装置DAと、を備えるシステムにおいて、−有限インパルス応答を伴う第2の帯域通過デジタルフィルタF2、前記第2のデジタルフィルタF2の出力側に配置されたゲイン手段G、位相従属型の数値制御式発振器NCO、および第2のデジタル/アナログコンバータCNA2を備える第2の経路V2と、−前記第1および第2の経路V1、V2の信号を合計するための再結合装置Sと、をさらに備える。

(もっと読む)

プッシュプル増幅器

【課題】個々の単位増幅器で発生する高調波2foを抑圧して、スプリアスを低減することができるプッシュプル増幅器を得ることを目的とする。

【解決手段】単位増幅器2〜5の入力側整合回路として動作する平衡−不平衡変換回路11と、単位増幅器2〜5の出力側整合回路として動作する平衡−不平衡変換回路21とがバランを用いて構成されており、平衡−不平衡変換回路11におけるバラン12,13,14の配置と、平衡−不平衡変換回路21におけるバラン22,23,24の配置とが点対称である。

(もっと読む)

半導体装置

【課題】本発明は、半導体装置に含まれる増幅回路における入出力特性の線形性が劣化するのを抑えるとともに、増幅器自体における入出力特性の線形性が劣化するのを抑えることができる半導体装置を提供する。

【解決手段】本発明は、外部と接続する複数の端子を有する配線基板72に、半導体チップ71を実装してパッケージングしてある半導体装置である。半導体装置は、半導体チップ上に形成してある、少なくとも一つの差動増幅器61と、平衡信号線路を差動増幅器61と接続し、半導体チップ71上に形成してある、少なくとも一つのバラン62とを備える。差動増幅器61の接地配線と、バラン62の接地配線とは、半導体チップ71上に分離して形成してあり、差動増幅器61の一つの接地配線と配線基板72とを接続するボンディングワイヤ77の数が、バラン62の一つの接地配線と配線基板72とを接続するボンディングワイヤの77数より多い。

(もっと読む)

信号送信回路

【課題】消費電流の増大を防止しながら、高調波の発生を抑制する。

【解決手段】

信号送信回路は、単一周波数の信号を出力する発振器と、発振器から出力された信号又は外部から伝送された信号を増幅する増幅部と、増幅部から出力された信号の出力電流を制御する可変電流器を有する出力バッファ部とからなる増幅回路と、増幅回路から出力された信号から、この信号の高調波成分を抽出し、抽出された高調波成分のパワーに基づき、可変電流器の電流を制御する電流制御電圧を出力する飽和レベル制御回路と、発振器及び飽和レベル制御回路の電源を制御する電源制御回路とを備える。

(もっと読む)

増幅装置及び増幅方法

【課題】増幅後の出力信号の劣化を抑えること。

【解決手段】信号分離部21は入力信号から第1の信号及び第2の信号を分離する。第1の信号生成部22は、第1の信号を処理したときに生じるリンギングを抑圧可能な第1のキャンセル信号を第1の信号に基づいて生成する。第1の合成部23は第1の信号と第1のキャンセル信号とを合成する。第1の増幅部24は第1の合成部23の出力信号を増幅する。第2の信号生成部25は、第2の信号を処理したときに生じるリンギングを抑圧可能な第2のキャンセル信号を第2の信号に基づいて生成する。第2の合成部26は第2の信号と第2のキャンセル信号とを合成する。第2の増幅部27は第2の合成部26の出力信号を増幅する。第3の合成部28は第1の増幅部24の出力信号と第2の増幅部27の出力信号とを合成する。

(もっと読む)

トランスコンダクタンスアンプ及びそれを用いたGm−Cフィルタ

【課題】線形性能が優れたGmアンプ、このGmアンプを用いて高速動作が可能で、入力電圧範囲が広く、かつ線形性能の優れたGm−Cフィルタを提供する。

【解決手段】入力信号が端子17、18から供給され、ソース端子が電源端子に接続されるMOSトランジスタ11、12、同相制御信号がゲート端子から供給されるMOSトランジスタ13、14、出力信号を出力する出力端子対の平均電圧を一定にするためMOSトランジスタ13、14のゲート端子に同相制御信号を出力する同相制御アンプ15、入力信号を入力して、MOSトランジスタ11、12に入力される入力信号の大小に応じて基板電圧を制御する基板制御信号をMOSトランジスタ11、12の基板端子に供給する基板電圧制御回路21、22によってGmアンプを構成する。

(もっと読む)

1 - 20 / 133

[ Back to top ]