Fターム[5J500AF16]の内容

Fターム[5J500AF16]に分類される特許

1 - 20 / 331

高周波増幅器

高周波増幅器

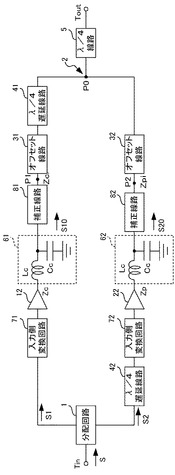

ドハティ増幅器

【課題】 単純な回路構成を有し、調整が容易なドハティ増幅器を提供する。

【解決手段】 第1の入力信号を増幅するキャリアアンプ12と、飽和出力電力がキャリアアンプと異なり、第2の入力信号を増幅するピークアンプ22とを有し、キャリアアンプは、第1のトランジスタと、第1のトランジスタと同一のパッケージ内に設けられた第1の内部変換回路とを含み、ピークアンプは、第2のトランジスタと、第2のトランジスタと同一のパッケージ内に設けられた第2の内部変換回路とを含み、第1及び第2の内部変換回路は、第1及び第2のトランジスタの出力インピーダンスを互いに異なる値に変換する。

(もっと読む)

CMOS集積回路及び増幅回路

【課題】入力トランジスタの構造を櫛形構造にしてゲート抵抗を抑えつつ、NFの増大を防ぐことが可能なCMOS集積回路を提供する。

【解決手段】トランジスタは、ゲート配線から櫛歯状に延びて形成され、信号入力端子からの入力信号が供給されるゲート電極と、ゲート配線に対向した位置に形成されるソース配線から、ゲート電極の櫛歯の間に1つ起きに櫛歯状に延びて形成される、接地端子に接続されたソース電極と、ゲート配線に対向した位置に形成されるドレイン配線から、ゲート電極の櫛歯の間のソース電極が存在しない箇所に櫛歯状に延びて形成される、電源端子に接続されたドレイン電極と、を備え、ゲート電極と、ソース電極またはドレイン電極とは、重なり合う領域が存在しないことを特徴とする、CMOS集積回路が提供される。

(もっと読む)

CMOS集積回路及び増幅回路

【課題】SOI基板にLNA回路を形成した場合や、バルクCMOSプロセスを用いてLNA回路を形成した場合に、NFの劣化の回避と高い線形性の達成とを実現することが可能なCMOS集積回路を提供する。

【解決手段】ゲート電極に信号入力端子が、ドレイン電極に電源端子が、ソース電極に接地端子がそれぞれ接続された電界効果トランジスタを備え、前記電界効果トランジスタはSOI(Silicon−On−Insulator)基板上に形成し、ボディ電位と、ソース電位以下の電位との間を、抵抗素子で接続することを特徴とする、CMOS集積回路が提供される。かかるCMOS集積回路を用いることで、NFの劣化の回避と高い線形性の達成とを実現することが可能となる。

(もっと読む)

増幅回路および受光回路

【課題】回路の小型化を図ること。

【解決手段】増幅回路100は、パッド111と、TIA150と、オンチップインダクタ130と、シャント容量140と、を1つのチップに備えている。パッド111には電流信号が入力される。TIA150は、入力された電流信号を電圧信号に変換して出力する。オンチップインダクタ130は、パッド111とTIA150との間に直列に接続されている。シャント容量140は、一端がオンチップインダクタ130とTIA150との間に接続され、他端がグランドに接続されている。

(もっと読む)

無線装置およびその製造方法

【課題】ICチップのプロセスばらつきによって高周波特性がばらついた場合でも、回路特性を最適化できるICチップを基板にフリップチップ実装する無線装置を提供する。

【解決手段】無線装置は、マイクロ波、ミリ波帯の電力増幅器用高周波ICチップ100、バンプ102、入力端子103、出力端子104、基板105、アンダーフィル106、プロセスばらつき検出部110を有する。プロセスばらつき検出部は、プロセスばらつきによる回路特性の変動量をモニタし、モニタされた回路特性の変動量を用いて、算出されたパラーメータを有するアンダーフィル106が、基板105とミリ波帯の電力増幅器用高周波ICチップ100との間に充填されることで、プロセスばらつき及びアンダーフィルの影響があっても、所望の回路特性が得られる無線装置を提供できる。

(もっと読む)

半導体装置、電子装置、車両、及び過熱検出方法

【課題】過熱検出回路の検出温度がばらつくことを抑制する。

【解決手段】コンパレータ170には、第1抵抗110と第1定電流源120の間の電圧Aと、ダイオード130と第2定電流源140の間の電圧Bが入力される。第1リーク電流源150は、ドレインが第1抵抗110と第1定電流源120の間に接続されており、ソース及びゲート電極が第1定電流源120と第2配線104の間に接続されている。第2リーク電流源160は、ドレインが第1配線102とダイオード130の間に接続されており、ソース及びゲート電極がダイオード130と第2定電流源140の間に接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】オン時における電流の迅速な立ち上がりを実現し、複雑な工程を経ることなく、n型HEMTとモノリシックにインバータを構成可能な半導体装置を得る。

【解決手段】第1の極性の電荷(ホール)供給層22aと、電荷供給層22aの上方に形成されており、凹部22baを有する第2の極性の電荷(ホール)走行層22bと、電荷走行層22bの上方で凹部22baに形成されたゲート電極29とを含むp型GaNトランジスタを備える。

(もっと読む)

半導体パッケージ、及び半導体パッケージの製造方法

【課題】高周波電力増幅器の汎用性を確保しつつ、低コスト化及び小型化が可能な半導体パッケージ(P)を提供すること。

【解決手段】接地導体(131)と、前記接地導体(131)の上部に設けられた2層の高周波基板(130)と、上層の前記高周波基板(130)を挟むように設けられた一対の導体(134)と、を含む、半導体パッケージ(P)が提供される。また、この半導体パッケージ(P)を含む高周波電力増幅器(100)が提供される。

(もっと読む)

安定化回路を備える半導体装置

【課題】ガン発振に伴う負性抵抗を抑制し、安定的かつ高効率の電力増幅を得るための安定化回路を備える半導体装置を提供する。

【解決手段】基板10と、基板上に配置され、ガン発振である高周波負性抵抗発振の発振周波数において負性抵抗を生ずる能動素子140と、基板上に配置され、能動素子のドレイン端子電極と出力端子との間に接続され、負性抵抗の絶対値に等しい抵抗値を有する抵抗Rと、抵抗Rに並列に接続され、高周波負性抵抗発振の発振周波数に同調するインダクタンスLとキャパシタンスCからなるタンク回路とからなる安定化回路120とを備え、安定化回路120は、発振周波数に、インダクタンスLとキャパシタンスCからなる共振周波数を同調することによって、発振周波数において、抵抗Rによって負性抵抗をキャンセルする半導体装置。

(もっと読む)

送信装置及びこの送信装置で使用される制御方法

【課題】EXCITERユニットの簡素化、コスト削減の実現を可能にする。

【解決手段】送信装置は、電力増幅部13と、送出部15と、冷却部27と、温度検出手段181と、出力電力検出手段182と、冷却制御手段183とを備えている。電力増幅部13は、伝送信号を電力増幅する。送出部15は、電力増幅部13の出力を伝送路へ送出する。冷却部17は、電力増幅部13を冷却する。温度検出手段181は、電力増幅部13の温度を検出する。出力電力検出手段182は、電力増幅部13の出力電力を検出する。冷却制御手段183は、温度検出手段181の検出結果及び出力電力検出手段182の検出結果に基づいて、冷却部17の冷却処理を制御する。

(もっと読む)

電力増幅器

【課題】本発明は、発振電力を吸収する抵抗の抵抗値を容易に制御できる電力増幅器を提供することを目的とする。

【解決手段】本願の発明に係る電力増幅器10は、複数のトランジスタセルが形成された半導体基板12と、該半導体基板上に形成された、該複数のトランジスタセルのドレイン電極40と、該半導体基板上に該ドレイン電極と接続されるように形成された、ドレインパッド42と、該半導体基板に、該ドレインパッドに沿って該ドレインパッドと接するように形成されたイオン注入抵抗44と、該半導体基板上に該イオン注入抵抗を介して該ドレインパッドと接するように形成されたフローティング電極46と、該半導体基板の外部に形成された出力整合回路16と、該ドレインパッドと該出力整合回路を接続する配線18a,18b,18c,18dと、を備える。

(もっと読む)

ドハティ増幅装置及び通信装置

【課題】ドハティ増幅装置の効率低下を防止する。

【解決手段】ドハティ増幅装置は、メインアンプを構成するメインアンプデバイス1と、ピークアンプを構成するピークアンプデバイス2と、メインアンプデバイス1及びピークアンプ2が実装された基板15とを有している。メインアンプデバイス1は、第1デバイス本体1c、第1入力端子1a、及び、第1出力端子1bを備え、第1入力端子1a及び第1出力端子1bが第1デバイス本体1cを挟んで対向して配置されている。ピークアンプデバイス2は、第2デバイス本体2c、第2入力端子2a、及び、第2出力端子2bを備え、第2入力端子2a及び第2出力端子2bが第2デバイス本体2cを挟んで対向して配置されている。ピークアンプデバイス2は、メインアンプデバイス1の位置に対して、メインアンプデバイス1の第1入力端子から第1出力端子に向かう入出力方向Dsにずれた位置に、実装されている。

(もっと読む)

高周波電力増幅器

【課題】レイアウト面積を増加させることなく、各トランジスタの負荷インピーダンスを均一にすることができる高周波電力増幅器を得る。

【解決手段】半導体チップ2上に、トランジスタ3a,3bと、トランジスタ3a,3bに隣接したコレクタパッド4a,4bとが設けられている。トランジスタ3a,3bとコレクタパッド4a,4bはそれぞれコレクタ配線6a,6bにより接続されている。半導体チップ2外に外部パッド8が設けられている。この外部パッド8に出力端子9が接続されている。コレクタパッド4a,4bと外部パッド8はそれぞれワイヤ10a,10bにより接続されている。コレクタパッド4aは、コレクタパッド4bよりも外部パッド8から遠い位置に配置されている。コレクタパッド4aから出力端子9までの電気長は、コレクタパッド4bから出力端子9までの電気長と同じである。

(もっと読む)

半導体電力増幅器

【課題】ビアホールの数を少なくしてもループ発振などの特性劣化が生じにくい半導体電力増幅器を提供する。

【解決手段】半導体電力増幅器は、ゲート電極Gと、ドレイン電極Dと、前記ゲートフィンガー電極に対向して配置されるソースフィンガー電極横手方向の両サイドに引き出される2つのソース電極Sと、を有するユニットFETと、前記ユニットFETが、前記ソース電極間を結ぶ略直線方向に複数個並列配置され、隣り合うユニットFET間に存在する2つのソース電極の両方を共通して高周波グランド面と接続する第1の接地インダクタンス値を有する第1のビアホール18Kと、隣り合うユニットFETが存在しない側のソース電極上に配置され、接地インダクタンスを等しくするために前記高周波グランド面に接続する第2の接地インダクタンス値を有する第2のビアホール18Dと、を有する。

(もっと読む)

半導体装置

【課題】消費電力が低減された半導体装置を提供することである。

【解決手段】入力電位および基準電位が入力される差動増幅器、利得段および出力電位が出力される出力段を有する半導体装置において、該出力段にオフ状態でのリーク電流が低いトランジスタを配置することで、該利得段から供給される電位が一定に保持される半導体装置である。また、オフ状態でのリーク電流が低いトランジスタとしては、酸化物半導体層を有し、且つ酸化物半導体層にチャネル形成領域を有するトランジスタを用いることである。

(もっと読む)

集積電力段

【課題】集積電力段において、入力電圧を集積電力段の一側面(例えば上面)で受け取り、出力電圧を集積電力段の反対側面(例えば底面)から出力する。

【解決手段】集積電力段は負荷段の上に位置する共通ダイを備え、共通ダイはドライバ段102及び電力スイッチ104を備える。電力スイッチは制御トランジスタ110及び同期トランジスタ112を含む。制御トランジスタのドレインD1が共通ダイの入力電圧を共通ダイの一側面(例えば上面)で受ける。制御トランジスタのソースS1が同期トランジスタのドレインD2に結合され、前記共通ダイの出力電圧を共通ダイの反対側面(例えば底面)で出力する。電力段の下にインターポーザ106を含めることができる。インターポーザは共通ダイの反対側面で共通ダイの出力電圧に結合される出力インダクタ118及び必要に応じ出力キャパシタ120を含む。

(もっと読む)

ドライバ集積化回路

【課題】プロセスの耐圧を超える電圧が出力でき、要求される装置性能(高速・高電圧)を満足するドライバ集積化回路の構成を提供する。

【解決手段】差動入力回路と、レベルシフト回路と、出力回路が、同一のプロセスで製造され、基板電位(サブ電位)が異なる、3つ以上のチップに分割配置されており、それぞれのチップの基板印加電圧が異なるように設定することにより、プロセス耐圧よりも大きい出力電圧を提供する。

(もっと読む)

光受信回路

【課題】受光素子の直近にインダクタンス素子を配置することなしに光受信回路を広帯域化する。

【解決手段】光受信回路は、光信号を電気信号に変換する受光素子3と、受光素子3のアノードと出力端子10との間を接続する電気線路4,6と、受光素子3のカソードを交流的に接地すると共に、カソードに直流バイアスを印加するバイアス分離回路5とを備える。電気線路4,6の特性インピーダンスは、出力端子10に接続される負荷抵抗7の抵抗値よりも高い。

(もっと読む)

1 - 20 / 331

[ Back to top ]