Fターム[5J500AH17]の内容

Fターム[5J500AH17]に分類される特許

1 - 20 / 774

正帰還増幅器およびインターポレーション回路

正帰還増幅器およびインターポレーション回路

D級増幅器

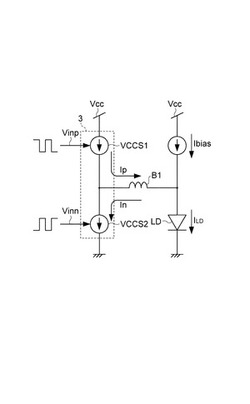

駆動回路、及び、光送信装置

【課題】変調信号の大きさ及び応答速度を向上可能な駆動回路及び光送信装置を提供する。

【解決手段】差動信号の入力に応じて発光素子LDの駆動電流を増減する駆動回路3である。差動信号の正相信号Vinpが入力される端子と、差動信号の逆相信号Vinnが入力される端子と、発光素子LDのアノードに接続されている端子と、正相信号Vinpが入力される端子に接続されている正相信号処理回路と、逆相信号Vinnが入力される端子に接続されている逆相信号処理回路と、アノードが接続されている端子に接続されている第1及び第2の電圧制御電流源回路を備える。第1の電圧制御電流源回路には、正相信号Vinpに対応する電圧及び逆相信号Vinnの逆相に対応する電圧が入力され、第2の電圧制御電流源回路には、逆相信号Vinnに対応する電圧及び正相信号Vinpの逆相に対応する電圧が入力される。

(もっと読む)

ダブルソースフォロア回路

【課題】電流源によって流れる電流量を増大させることなく、出力信号の立ち上り、立ち下りを高速化することができるダブルソースフォロア回路を提供する。

【解決手段】nMOSFET102を含むソースフォロア回路と、nMOSFET102とは極性が異なるpMOSFET101を含むソースフォロア回路と、nMOSFET102を含むソースフォロア回路、pMOSFET101を含むソースフォロア回路に入力信号を入力する入力端子111と、nMOSFET102を含むソースフォロア回路、pMOSFET101を含むソースフォロア回路から出力信号を出力する共通の出力端子112)と、を含むダブルソースフォロア回路を構成する。

(もっと読む)

D級増幅回路

【課題】D級増幅回路において、確実に電源パンピングの影響をキャンセルする。

【解決手段】第1スイッチ61がオン、第2スイッチ63がオフの時に、電源電圧VDDと接地間の電流をコンデンサ62に充電させ、第1スイッチ61がオフ、第2スイッチ63がオンの時に、コンデンサ62の電圧と基準電圧Vrとをコンパレータ64により比較する。コンパレータ64の出力をパワーリミット回路30に入力し、コンデンサ62の電圧が基準電圧Vrを超える場合には、PWM変調回路20からの出力信号のパルス幅を制限する。

(もっと読む)

オペアンプ補償回路

【課題】出力バッファを有するオペアンプA1であつて、オフセット電位を従来よりも抑えられるオペアンプ補償回路を提供する。

【解決手段】バッファの出力と接地間に、入力信号が接地から電源電圧まで変化されるMOSトランジスタT1を有し、あるいは、NチャンネルトランジスタTN1と、PチャンネルトランジスタTP1とを並列接続し、それぞれ入力信号と反転された入力信号が入力されている構成を有し、オフセット電位が接地となることを特徴とする。

(もっと読む)

出力回路及びそれを備えた増幅器

【課題】出力波形に付加される遅延の増大を抑制することが可能な出力回路を提供すること。

【解決手段】本発明にかかる出力回路は、高電位側電源端子と外部出力端子Voutとの間に設けられ、電源電圧VDD〜接地電圧VSS間の電圧範囲を振幅する一対の増幅信号の一方に基づいてソース−ドレイン間に流れる電流が制御される出力トランジスタMP11と、低電位側電源端子と外部出力端子Voutとの間に設けられ、一対の増幅信号の他方に基づいてソース−ドレイン間に流れる電流が制御される出力トランジスタMN11と、電源電圧VDDより低く接地電圧VSSより高い中間電圧VMLが供給されている低電位側電源端子と、出力トランジスタMP11のゲートと、の間に設けられ、出力トランジスタMP11のゲート電圧と中間電圧VMLとの電圧差に基づいて出力トランジスタMP11のゲートをクランプするクランプ用トランジスタMP12と、を備える。

(もっと読む)

駆動回路

【課題】消費電流が小さな駆動回路を提供する。

【解決手段】オフセット補償機能付き駆動回路190は、入力電位に応じたレベルの出力電位を出力するプッシュ型駆動回路160と、駆動回路160のオフセット電圧VOFを補償するオフセット補償回路とを備える。オフセット補償回路は、キャパシタ122およびスイッチS1〜S4を含む。スイッチS1,S2をオンしてキャパシタ122をオフセット電圧VOFに充電し、次にスイッチS3をオンしてVI+VOFを駆動回路160に与え、次いでスイッチS4をオンしてVO=VIとする。したがって、消費電流を低減し、オフセット電圧VOFを補償できる。

(もっと読む)

同相電圧帰還回路及び全差動演算増幅器

【課題】クロックフェイズの切り替わりにおける電圧スパイクの低減と共に出力電圧の収束速度の向上を図る。

【解決手段】第1及び第2の同相電圧検出器301,302は、ノンオーバーラップ期間が設定された2相クロックで駆動され、第1の同相電圧検出器301は、第1のクロック位相において充電動作し、第2のクロック位相において出力同相電圧の生成と電荷保持動作をし、第2の同相電圧検出器302は、第2のクロック位相において充電動作し、第1のクロック位相において出力同相電圧の生成と電荷保持動作をし、ノンオーバーラップ期間において、第1及び第2の同相電圧検出器301,302は、スイッチ35a〜35f、36a〜36fにより入力段及び出力段と電気的に分離され、同相電圧出力トランジスタのゲート・ソース間寄生容量により電荷保持動がなされる構成となっている。

(もっと読む)

スイッチングシステムおよびスイッチングシステムの制御方法

【課題】EMIを低減できるスイッチングシステムを提供する。

【解決手段】本発明は、スイッチングシステムを提供する。スイッチングシステムは、Hブリッジ、電流ルーターおよび制御回路を含む。Hブリッジは、第一出力ノードに結合される第一スイッチと第二スイッチおよび第二出力ノードに結合される第三スイッチと第四スイッチを含み、ロードは、第一出力ノードと第二出力ノード間に結合される。電流ルーターは、第一出力ノードと第二出力ノード間に結合される第一シャントスイッチと第二シャントスイッチを含む。制御回路は、第一制御信号を生成して、第一スイッチと第四スイッチを制御し、第二制御信号を生成して、第二スイッチと第三スイッチを制御し、第三制御信号を生成して、第一シャントスイッチを制御し、第四制御信号を生成して、第二シャントスイッチを制御する。

(もっと読む)

出力回路及びデータドライバ及び表示装置

【課題】高速動作に対応可能とし、消費電力を抑制可能とし面積も抑制可能とする出力回路の提供。

【解決手段】出力回路は、差動入力段10と出力増幅段20と増幅加速回路70を備え、増幅加速回路70は、入力対が入力端子1と出力端子2に夫々接続された差動対171、172と、第5の電源端子E5と前記差動対の出力対間にそれぞれ接続された負荷素子対174、175を備え、差動対171、172の入力電位差によって、差動入力段10の第2のカレントミラー40の入力が接続する第4のノードN4への電流供給を制御する第1の電流源回路176と、差動入力段10の第1のカレントミラー30の出力が接続する第1のノードN1への電流供給を制御する第2の電流源回路178を含む。

(もっと読む)

液晶表示装置の駆動回路

【課題】入出力間オフセット電圧を削減しつつ消費電流を削減する。

【解決手段】第1導電型の第1差動回路は、第1入力信号と出力信号とを差動入力信号とする。第1導電型の第2差動回路は、第2入力信号と出力信号とを差動入力信号とする。第2導電型の第3差動回路は、第1入力信号と出力信号とを差動入力信号とする。第2導電型の第4差動回路は、第2入力信号と出力信号とを差動入力信号とする。出力段回路は、第1乃至第4差動回路の出力に基づいて出力信号を出力する。差動増幅器は、上記第1乃至第4差動回路、出力段回路を具備し、制御信号に基づいて、第1乃至第4差動回路を形成するトランジスタのチャネル長とチャネル幅との比を変更する。

(もっと読む)

電流電圧変換回路

【課題】回路全体の耐圧を高めることができ、入力側に高い電圧が印加される場合であっても素子破壊を効果的に防止し、正常に動作させ得る電流電圧変換回路を提供する。

【解決手段】電流電圧変換回路1は、検出抵抗10を流れる電流に応じた信号であって且つ抵抗11及び抵抗12の抵抗値に応じた電圧信号を出力するように構成されている。この回路では、第3トランジスタTra1と第4トランジスタTrb1とが対をなし、第3トランジスタTra2と第4トランジスタTrb2とが対をなしている。そして、駆動電圧生成部20は、これら複数のトランジスタ対における各第3トランジスタと各第4トランジスタとの各共通接続部に対し、検出抵抗10の高電位側よりも低くグランドよりも高い駆動電圧を、グランド側のトランジスタ対となるにつれて印加電圧が低くなるように段階的に印加している。

(もっと読む)

イメージセンサー及びこれを備えるX線イメージセンシングモジュール

【課題】高品質のイメージが得られるイメージセンサーを提供する。

【解決手段】検出部で検出された電荷を増幅させ、入力端子、増幅端子、及び出力端子を含む電荷検出増幅部を備え、電荷検出増幅部は、入力端子と前記増幅端子との間に接続された第1キャパシタと、入力端子と前記増幅端子との間に接続された第1スイッチングユニットと、増幅端子と出力端子との間に接続された第2キャパシタと、出力端子と基準電圧端子との間に接続された第2スイッチングユニットと、を備えることを特徴とするイメージセンサー。

(もっと読む)

差動増幅器

【課題】出力電圧の出力精度に段差が発生していた。

【解決手段】電流源で駆動される第1、第2の差動対と、その電流源を駆動する第1の基準電流発生回路と、を備える第1の差動入力部と、電流源で駆動される第3、第4の差動対と、その電流源を駆動する第2の基準電流発生回路と、を備える第2の差動入力部と、前記第1、第2の差動入力部との出力に応じて、出力する出力部と、を有し、前記第1、第2の基準電流発生回路の第1、第2の電流経路上に接続される第1、第2のトランジスタを入力信号に応じて制御することで、前記第1、第2の差動入力部の出力を制御する差動増幅器。

(もっと読む)

受光回路

【課題】受光回路の消費電流を削減する。

【解決手段】一つの実施形態によれば、受光回路は、トランスインピーダンスアンプと出力回路が設けられる。トランスインピーダンスアンプは、フォトダイオード、帰還抵抗、及び第1のトランジスタが設けられる。フォトダイオードは、光信号を電気信号に変換する。帰還抵抗は、フォトダイオードと内部出力端子の間に設けられる。第1のトランジスタは、ゲートにフォトダイオードで光電変換された電気信号が入力され、ドレインが内部出力端子に接続される。出力回路は、第1のトランジスタと同一チャネル型であり、ゲートが内部出力端子に接続され、電流源負荷が接続されるとともにドレイン側から出力信号を出力する第2のトランジスタを含む。

(もっと読む)

差動入力を有する直交出力低雑音トランスコンダクタンス増幅器

【課題】差動入力を有する直交出力低雑音トランスコンダクタンス増幅器を提供する。

【解決手段】低雑音トランスコンダクタンス増幅器200は、差動RF入力信号を受信するように構成されたPMOSトランスコンダクタンス部110と、PMOSトランスコンダクタンス部に結合されたPMOSカスコード部130と、RF差動入力信号を受信するように構成されたNMOSトランスコンダクタンス部120と、NMOSトランスコンダクタンス部に結合されたNMOSカスコード部140と、を含み、PMOSカスコード部及びNMOSカスコード部は、差動直交出力信号gmpq、gmnq及び差動同相出力信号gmpi、gmniを提供する。RF信号を増幅するための方法は、差動RF入力信号を受信することと、差動RF入力信号を電流信号に変換することと、電流信号をバッファリングして差動直交出力信号及び差動同相出力信号を提供する。

(もっと読む)

電源回路

【課題】 広帯域無線通信を行う送信機に用いられ、電源変換効率を向上させることができる電源回路を提供する。

【解決手段】 入力信号をプッシュプル増幅方式で増幅するプッシュプル増幅部と、制御信号によりプッシュプル増幅部に提供する電源電圧の電圧レベルを複数の電源112〜115、116〜119の選択接続によって可変とする可変電源部と、制御信号として、入力信号に基づいて電源電圧の電圧レベルを制御するために複数の電源を選択する選択信号C1〜C8を出力するスイッチ制御部138と、可変電源部における複数の電源112〜115、116〜119の負荷が一定となるよう、選択信号による電源の選択先を変更するスイッチ制御信号変換部139とを備えた電源回路としている。

(もっと読む)

電源回路、電源回路の信号切替方法、帯電装置、画像形成装置

【課題】負荷の増加に伴い、駆動用ドライバをICの外付け素子として用いる場合でも、専用ICを新たに作成するまたは駆動用ドライバに対するプリドライバおよび端子を別途設けることなく、ICと出力端子を共用することで設計およびチップ製作にかかるコストを低減する。

【解決手段】入力信号2,3を切替選択信号22によって切り替え、出力信号13〜16を出力する信号切替ブロック12と、出力信号13〜16をそれぞれチャンネルの異なるスイッチング素子に入力する複数のD級アンプと、を備え、信号切替ブロック12は、複数のD級アンプを、負荷を駆動するための駆動用ドライバ、または外付けされた駆動用ドライバ回路に対するプリドライバとするかを前記切替選択信号により切り替える。

(もっと読む)

1 - 20 / 774

[ Back to top ]