Fターム[5J500AH25]の内容

Fターム[5J500AH25]の下位に属するFターム

可変抵抗 (287)

Tr又はダイオードで構成された抵抗 (17)

負性抵抗 (24)

Fターム[5J500AH25]に分類される特許

1 - 20 / 3,113

全差動型帰還増幅回路および電気機器

広帯域アンプ、広帯域信号通信回路および増幅方法

コンデンサマイクロホン用インピーダンス変換器およびコンデンサマイクロホン

増幅装置

スイッチングアンプ

自励発振型D級アンプおよび自励発振型D級アンプの自励発振周波数制御方法

電力増幅器

制御回路および位相変調器

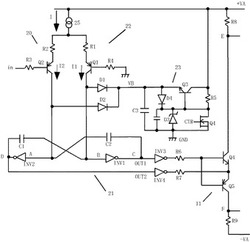

パルス幅変調回路およびスイッチングアンプ

【課題】 電源オフ状態に移行する際に、漏れ電流によって蓄積手段が充電され、2つの出力素子の入力が共にハイレベルになり、出力が共にローレベルになり、次に電源オン状態に移行する際に、パルス幅変調動作を開始することができないとい問題を解決でき、かつ、入力信号に正確に対応したパルス幅変調信号を出力することができるパルス幅変調回路を提供する。

【解決手段】 パルス幅変調回路20は、電源オン状態から電源オフ状態に移行する際に、オン状態に制御されることにより、漏れ電流の原因となる電源電圧V2を接地電位に瞬時に放電させ、0Vにさせるスイッチ手段Q4を備える。スイッチ手段Q4は、ダイオードD1、D2の各カソード側に接続されているので、電流I1、I2によってコンデンサC1、C2を充電する際に、コンデンサC1、C2から電気的に分離された状態になるので、C1、C2の充電に誤差を与えない。

(もっと読む)

トランスインピーダンスアンプ

【課題】入力電流の大きさに応じた量の電流を入力電流から分流することによりダイナミックレンジが拡大されたトランスインピーダンスアンプ(TIA)において、入力インピーダンスの変化を低減する。

【解決手段】TIA10は、光電流Iinの大きさに応じた出力電圧Voutを生成する。TIA10は、光電流Iinを出力電圧Voutに変換する利得可変増幅回路12と、光電流Iinが大きいほど大きな電流Icdを光電流Iinから分流する分流回路14と、光電流Iinが大きいほど利得可変増幅回路12の利得を小さくする利得調整回路20とを備える。

(もっと読む)

高周波増幅回路

【課題】 ステップ式可変減衰器を実装することなく、低雑音特性及び高飽和特性を確保しながら、温度変動に伴う利得変化を抑制することができる高周波増幅回路を得る。

【解決手段】 高周波信号を減衰させる可変減衰器と、半導体のバンドギャップに基づき温度比例電流及び温度固定電流を出力するバンドギャップリファレンス電流源回路と、前記温度比例電流及び前記温度固定電流を入力とし、温度に対して所定の傾きで変化する電圧を出力する可変減衰器制御電圧生成回路とを備え、前記可変減衰器制御電圧生成回路の出力電圧で前記可変減衰器の減衰量を制御する。

(もっと読む)

駆動回路、及び、光送信装置

【課題】変調信号の大きさ及び応答速度を向上可能な駆動回路及び光送信装置を提供する。

【解決手段】差動信号の入力に応じて発光素子LDの駆動電流を増減する駆動回路3である。差動信号の正相信号Vinpが入力される端子と、差動信号の逆相信号Vinnが入力される端子と、発光素子LDのアノードに接続されている端子と、正相信号Vinpが入力される端子に接続されている正相信号処理回路と、逆相信号Vinnが入力される端子に接続されている逆相信号処理回路と、アノードが接続されている端子に接続されている第1及び第2の電圧制御電流源回路を備える。第1の電圧制御電流源回路には、正相信号Vinpに対応する電圧及び逆相信号Vinnの逆相に対応する電圧が入力され、第2の電圧制御電流源回路には、逆相信号Vinnに対応する電圧及び正相信号Vinpの逆相に対応する電圧が入力される。

(もっと読む)

ダブルソースフォロア回路

【課題】電流源によって流れる電流量を増大させることなく、出力信号の立ち上り、立ち下りを高速化することができるダブルソースフォロア回路を提供する。

【解決手段】nMOSFET102を含むソースフォロア回路と、nMOSFET102とは極性が異なるpMOSFET101を含むソースフォロア回路と、nMOSFET102を含むソースフォロア回路、pMOSFET101を含むソースフォロア回路に入力信号を入力する入力端子111と、nMOSFET102を含むソースフォロア回路、pMOSFET101を含むソースフォロア回路から出力信号を出力する共通の出力端子112)と、を含むダブルソースフォロア回路を構成する。

(もっと読む)

増幅回路及び無線通信装置

【課題】NFを増大させること無く、CMOS LNA回路の非動作時に、CMOS LNA回路に電流を流さないような構成とすることが可能な、増幅回路を提供する。

【解決手段】ゲート電極に、受信された無線信号を入力する信号入力端子が、ドレイン電極に電源端子が、ソース電極に接地端子がそれぞれ接続された入力トランジスタと、信号入力端子と入力トランジスタのゲート電極との間に設けられる第1スイッチと、電源端子と入力トランジスタのドレイン電極との間に設けられる第2スイッチと、を備え、入力トランジスタのゲート電極には所定のバイアス電圧が印加され、無線信号の受信時には、第1スイッチと第2スイッチとを同時にオンにして、無線信号の送信時には、所定のバイアス電圧を入力トランジスタのゲート電極に印加したまま、第1スイッチと第2スイッチとを同時にオフにすることを特徴とする、増幅回路が提供される。

(もっと読む)

CMOS集積回路及び増幅回路

【課題】入力トランジスタの構造を櫛形構造にしてゲート抵抗を抑えつつ、NFの増大を防ぐことが可能なCMOS集積回路を提供する。

【解決手段】トランジスタは、ゲート配線から櫛歯状に延びて形成され、信号入力端子からの入力信号が供給されるゲート電極と、ゲート配線に対向した位置に形成されるソース配線から、ゲート電極の櫛歯の間に1つ起きに櫛歯状に延びて形成される、接地端子に接続されたソース電極と、ゲート配線に対向した位置に形成されるドレイン配線から、ゲート電極の櫛歯の間のソース電極が存在しない箇所に櫛歯状に延びて形成される、電源端子に接続されたドレイン電極と、を備え、ゲート電極と、ソース電極またはドレイン電極とは、重なり合う領域が存在しないことを特徴とする、CMOS集積回路が提供される。

(もっと読む)

オーディオ信号処理回路およびそれを用いた電子機器

【課題】オーディオ信号処理回路100のノイズを抑制する。

【解決手段】非反転アンプ14は、第3演算増幅器OA3および分圧回路R1、R2を含み、第1バッファ10の出力電圧を非反転増幅する。スイッチSW2は、第3演算増幅器OA3の出力端子とその反転入力端子の間に設けられる。制御回路20は、第2電源電圧VCC2が所定のしきい値電圧より低いときにスイッチSW2をオンし、第2電源電圧VCC2がしきい値電圧より高いときにスイッチSW2をオフする。

(もっと読む)

増幅回路

【課題】ノイズフィギュアの劣化を抑制しつつ、過入力信号を調整可能な上限電圧および下限電圧の範囲内に制限する。

【解決手段】入力トランジスタと、第1端が前記入力トランジスタのゲートに接続され、第2端がバイアス電圧に接続される抵抗素子と、前記入力トランジスタのゲートに接続され、前記入力トランジスタのゲートへの入力を、前記バイアス電圧を基準とする(調整可能な)上限電圧および下限電圧の範囲内に制限する保護回路と、を備える、増幅回路。

(もっと読む)

CMOS集積回路及び増幅回路

【課題】SOI基板にLNA回路を形成した場合や、バルクCMOSプロセスを用いてLNA回路を形成した場合に、NFの劣化の回避と高い線形性の達成とを実現することが可能なCMOS集積回路を提供する。

【解決手段】ゲート電極に信号入力端子が、ドレイン電極に電源端子が、ソース電極に接地端子がそれぞれ接続された電界効果トランジスタを備え、前記電界効果トランジスタはSOI(Silicon−On−Insulator)基板上に形成し、ボディ電位と、ソース電位以下の電位との間を、抵抗素子で接続することを特徴とする、CMOS集積回路が提供される。かかるCMOS集積回路を用いることで、NFの劣化の回避と高い線形性の達成とを実現することが可能となる。

(もっと読む)

D級増幅回路

【課題】D級増幅回路において、確実に電源パンピングの影響をキャンセルする。

【解決手段】第1スイッチ61がオン、第2スイッチ63がオフの時に、電源電圧VDDと接地間の電流をコンデンサ62に充電させ、第1スイッチ61がオフ、第2スイッチ63がオンの時に、コンデンサ62の電圧と基準電圧Vrとをコンパレータ64により比較する。コンパレータ64の出力をパワーリミット回路30に入力し、コンデンサ62の電圧が基準電圧Vrを超える場合には、PWM変調回路20からの出力信号のパルス幅を制限する。

(もっと読む)

スイッチング回路及び包絡線信号増幅器

【課題】複数のスイッチング素子にて増幅したPWM信号を低損失で合成し、変調信号を復調することが可能なスイッチング回路、及び該スイッチング回路を備える包絡線信号増幅器を提供する。

【解決手段】本発明の一実施形態のスイッチング回路33は、N個(Nは2以上の整数)のトランジスタM1〜Mnのスイッチングを制御するための各制御端子をN−1個のコイルL1を介して縦続接続する接続回路と、一端が直流電源に電気的に接続されるコイルL2の他端及びトランジスタM1〜Mnの各一端の間に各別に接続されたコイルL3とを備え、接続回路の入力端子に入力されるPWM信号にて、スイッチング素子M1〜Mnを順次スイッチングさせるようにしてある。また、スイッチング回路33は、コイルL2の一端側又は他端側に縦続接続されるように挿入されたトランジスタM0を更に備える。

(もっと読む)

1 - 20 / 3,113

[ Back to top ]