Fターム[5J500AH33]の内容

Fターム[5J500AH33]の下位に属するFターム

Fターム[5J500AH33]に分類される特許

1 - 20 / 1,197

スイッチングアンプ

スプリッタ回路およびチューナーシステム

自励発振型D級アンプおよび自励発振型D級アンプの自励発振周波数制御方法

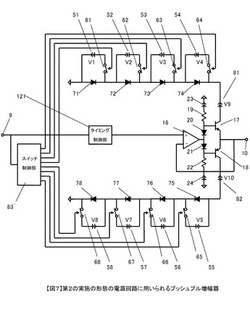

電源回路

【課題】 広帯域無線通信を行う送信機に用いられ、電源変換効率を向上させると共に、電圧レベル切替の遷移時間の影響を低減し、出力信号の歪特性を改善することができる電源回路を提供する。

【解決手段】 入力信号をプッシュプル増幅方式で増幅するプッシュプル増幅部と、制御信号によりプッシュプル増幅部に提供する電源電圧の電圧レベルを可変とする可変電源部と、入力信号に基づいて電源電圧の電圧レベルを制御する制御信号を出力するスイッチ制御部83′と、入力信号を特定の時間遅延させるタイミング制御部121を備え、スイッチ制御部83′が、制御信号の立ち上げの場合に、タイミング制御部121での遅延時間に対して電圧レベル切り替えの遷移時間に応じた早いタイミングで制御信号を立ち上げ、立ち下げの場合には遅延時間のタイミングで立ち下げる電源回路としている。

(もっと読む)

CMOS集積回路及び増幅回路

【課題】SOI基板にLNA回路を形成した場合や、バルクCMOSプロセスを用いてLNA回路を形成した場合に、NFの劣化の回避と高い線形性の達成とを実現することが可能なCMOS集積回路を提供する。

【解決手段】ゲート電極に信号入力端子が、ドレイン電極に電源端子が、ソース電極に接地端子がそれぞれ接続された電界効果トランジスタを備え、前記電界効果トランジスタはSOI(Silicon−On−Insulator)基板上に形成し、ボディ電位と、ソース電位以下の電位との間を、抵抗素子で接続することを特徴とする、CMOS集積回路が提供される。かかるCMOS集積回路を用いることで、NFの劣化の回避と高い線形性の達成とを実現することが可能となる。

(もっと読む)

D級増幅回路

【課題】D級増幅回路において、確実に電源パンピングの影響をキャンセルする。

【解決手段】第1スイッチ61がオン、第2スイッチ63がオフの時に、電源電圧VDDと接地間の電流をコンデンサ62に充電させ、第1スイッチ61がオフ、第2スイッチ63がオンの時に、コンデンサ62の電圧と基準電圧Vrとをコンパレータ64により比較する。コンパレータ64の出力をパワーリミット回路30に入力し、コンデンサ62の電圧が基準電圧Vrを超える場合には、PWM変調回路20からの出力信号のパルス幅を制限する。

(もっと読む)

CMOS集積回路及び増幅回路

【課題】入力トランジスタの構造を櫛形構造にしてゲート抵抗を抑えつつ、NFの増大を防ぐことが可能なCMOS集積回路を提供する。

【解決手段】トランジスタは、ゲート配線から櫛歯状に延びて形成され、信号入力端子からの入力信号が供給されるゲート電極と、ゲート配線に対向した位置に形成されるソース配線から、ゲート電極の櫛歯の間に1つ起きに櫛歯状に延びて形成される、接地端子に接続されたソース電極と、ゲート配線に対向した位置に形成されるドレイン配線から、ゲート電極の櫛歯の間のソース電極が存在しない箇所に櫛歯状に延びて形成される、電源端子に接続されたドレイン電極と、を備え、ゲート電極と、ソース電極またはドレイン電極とは、重なり合う領域が存在しないことを特徴とする、CMOS集積回路が提供される。

(もっと読む)

スイッチング回路及び包絡線信号増幅器

【課題】複数のスイッチング素子にて増幅したPWM信号を低損失で合成し、変調信号を復調することが可能なスイッチング回路、及び該スイッチング回路を備える包絡線信号増幅器を提供する。

【解決手段】本発明の一実施形態のスイッチング回路33は、N個(Nは2以上の整数)のトランジスタM1〜Mnのスイッチングを制御するための各制御端子をN−1個のコイルL1を介して縦続接続する接続回路と、一端が直流電源に電気的に接続されるコイルL2の他端及びトランジスタM1〜Mnの各一端の間に各別に接続されたコイルL3とを備え、接続回路の入力端子に入力されるPWM信号にて、スイッチング素子M1〜Mnを順次スイッチングさせるようにしてある。また、スイッチング回路33は、コイルL2の一端側又は他端側に縦続接続されるように挿入されたトランジスタM0を更に備える。

(もっと読む)

増幅器

【課題】 携帯電話をはじめとする移動体通信用高周波電力増幅器などの増幅器において、受信帯雑音特性が良好で小型な増幅器を提供する。

【解決手段】 第一の周波数を中心周波数とする信号を増幅する増幅素子と、前記増幅素子の前段または後段に接続される整合回路と、前記増幅素子と前記整合回路の間に接続され、前記第一の周波数とは異なる第二の周波数を中心周波数とする信号を減衰させるフィルタ回路と、を備えたことを特徴とする。

(もっと読む)

増幅回路及び無線通信装置

【課題】NFを増大させること無く、CMOS LNA回路の非動作時に、CMOS LNA回路に電流を流さないような構成とすることが可能な、増幅回路を提供する。

【解決手段】ゲート電極に、受信された無線信号を入力する信号入力端子が、ドレイン電極に電源端子が、ソース電極に接地端子がそれぞれ接続された入力トランジスタと、信号入力端子と入力トランジスタのゲート電極との間に設けられる第1スイッチと、電源端子と入力トランジスタのドレイン電極との間に設けられる第2スイッチと、を備え、入力トランジスタのゲート電極には所定のバイアス電圧が印加され、無線信号の受信時には、第1スイッチと第2スイッチとを同時にオンにして、無線信号の送信時には、所定のバイアス電圧を入力トランジスタのゲート電極に印加したまま、第1スイッチと第2スイッチとを同時にオフにすることを特徴とする、増幅回路が提供される。

(もっと読む)

電力増幅器

【課題】素子ばらつきや周波数特性に対して鈍感であり低損失な電力増幅器を得る。

【解決手段】入力端子INから入力した入力信号を増幅素子Tr1が増幅する。増幅素子Tr1の出力信号を増幅素子Tr2が増幅する。増幅素子Tr2の出力信号は出力端子OUTから出力される。増幅素子Tr2の出力と出力端子OUTとの間に整合回路M3が接続されている。増幅素子Tr1の出力と増幅素子Tr2の入力との間にスイッチSW1が接続されている。増幅素子Tr1の出力にスイッチSW2の一端が接続されている。整合回路M4の一端がスイッチSW2の他端に接続され、整合回路M4の他端が増幅素子Tr2の出力に直接に接続されている。

(もっと読む)

増幅回路

【課題】ノイズフィギュアの劣化を抑制しつつ、過入力信号を調整可能な上限電圧および下限電圧の範囲内に制限する。

【解決手段】入力トランジスタと、第1端が前記入力トランジスタのゲートに接続され、第2端がバイアス電圧に接続される抵抗素子と、前記入力トランジスタのゲートに接続され、前記入力トランジスタのゲートへの入力を、前記バイアス電圧を基準とする(調整可能な)上限電圧および下限電圧の範囲内に制限する保護回路と、を備える、増幅回路。

(もっと読む)

送信増幅器

【課題】低ひずみ、低雑音、且つ小形な送信増幅器を得る。

【解決手段】多段接続した増幅器のうちの少なくとも1段以上に、バイポーラトランジスタ3のコレクタ電極とベース電極との間に接続された抵抗9を備え、出力電源10からインダクタ8および抵抗9を介してバイポーラトランジスタ3のベース電極に入力バイアスを供給する増幅器を備える。

バイポーラトランジスタ3の動作条件を決める入力バイアスを、抵抗9と出力電源10とにより決定するので、バイアス回路によるひずみがバイポーラトランジスタ3に重畳されないため、低雑音な送信増幅器を実現することができる。

また、入力バイアスを供給するためだけにインダクタを設ける必要がないため、小形な送信増幅器を実現することができる。

(もっと読む)

高周波増幅器

【課題】ユニットセルの組み合わせで形成されるすべてのループ発振を抑制することができる高周波増幅器を提供する。

【解決手段】実施の形態に係る高周波増幅器は、入力された信号を分配する分配回路と、分配回路が分配した信号を増幅するFETセルと、分配回路とFETセルのゲート端子との間に直列に接続され、キャパシタと抵抗との並列回路から構成される安定化回路と、FETセルが増幅した信号を合成する合成回路とを備え、安定化回路をFETセルごとに配置する。

(もっと読む)

増幅回路および受光回路

【課題】回路の小型化を図ること。

【解決手段】増幅回路100は、パッド111と、TIA150と、オンチップインダクタ130と、シャント容量140と、を1つのチップに備えている。パッド111には電流信号が入力される。TIA150は、入力された電流信号を電圧信号に変換して出力する。オンチップインダクタ130は、パッド111とTIA150との間に直列に接続されている。シャント容量140は、一端がオンチップインダクタ130とTIA150との間に接続され、他端がグランドに接続されている。

(もっと読む)

EM級増幅器

【課題】高調波歪みを容易に低減させることのできるEM級増幅器を提供する。

【解決手段】本発明にかかるEM級増幅器は、主回路と、主回路に信号を入力する補助回路と、を有するEM増幅器であって、主回路は、プッシュプル構造を有することを特徴とする。この場合において、限定されるわけではないが、プッシュプル構造は、第一の主基礎回路と、第一の主基礎回路と同様な構造の第二の主基礎回路と、第一の主基礎回路と第二の主基礎回路に接続される負荷回路と、を有して構成される。

(もっと読む)

電力増幅回路および高周波モジュール

【課題】フィードバック制御を行っても、出力電力の低下を抑制できる電力増幅回路を実現する。

【解決手段】電力増幅回路を備える高周波モジュール10は、高周波電力増幅素子20、整合回路30、および駆動電源回路40を備える。高周波電力増幅素子20は、高周波増幅回路210、方向性結合器230を備える。方向性結合器230の主線路231の第1端は、高周波増幅回路210の後段増幅回路212の出力端子に接続されている。主線路231の第2端は、出力整合回路240を介して、高周波電力増幅素子20の高周波信号出力端子Poutに接続されている。後段増幅回路212の出力端子は、高周波電力増幅素子20

子20の第2駆動電源印加端子PV2にも接続されている。高周波信号出力端子Poutと高周波信号出力端子Poutとは、接続導体50で接続されている。

(もっと読む)

RFパルス信号生成用スイッチング回路、RFパルス信号生成回路、および物標探知装置

【課題】安定動作させながら、RFパルス信号の波形を高速に立ち下げることができるRFパルス信号生成用スイッチング回路を提供することにある。

【解決手段】ドレインスイッチング回路21は、n型からなる第1、第2、第3のFET211,212,213を備える。第1、第3のFET211,213のゲートには、制御パルスが印加され、ソースは接地されている。第1のFET211のドレインは、第2のFET212のゲートに接続し、第2のFET212のドレインには、駆動電圧Vdsが印加される。第2のFET212のソースと第3のFET213のドレインは接続され、接続点がパワーFET31のドレインに接続されている。第2のFET212のゲートソース間には、第2のFET212がオフ状態からオン状態へ遷移する際のゲート電圧を補償するための電荷を供給するコンデンサ215が接続されている。

(もっと読む)

高速入力インターフェース回路

【課題】高周波における入力インピーダンス整合が改善された、広帯域な高速入力インターフェース回路を提供する。

【解決手段】抵抗R1は、その一端が入力端子DTに接続され、他端がインダクタL1を介して第1の電源端子VCCに接続されている。また、抵抗R2は、その一端が入力端子DCに接続され、他端がインダクタL2を介して電源端子VCCに接続されている。また、抵抗R3は、その一端が入力端子DTに接続され、他端がインダクタL3を介して第2の電源端子VEEに接続されている。また、抵抗R4は、その一端が入力端子DCに接続され、他端がインダクタL4を介して電源端子VEEに接続されている。

(もっと読む)

電力増幅回路、および無線通信装置

【課題】回路面積を縮小しつつ、電力効率の向上を図ることが可能な電力増幅回路を提供する。

【解決手段】電力増幅回路は、シリコン基板上に集積された電力増幅回路である。電力増幅回路は、入力が第1の信号入力端子に接続された第1のアンプを備える。電力増幅回路は、入力が第2の信号入力端子に接続された第2のアンプを備える。電力増幅回路は、入力が前記第1のアンプの出力に接続され、出力が前記第2のアンプの出力に接続されたアンプ出力移相器を備える。電力増幅回路は、一端が電源に接続され、他端が前記アンプ出力移相器の出力に接続された一次側巻線と、一端が第1の信号出力端子に接続され、他端が第2の信号出力端子に接続された二次側巻線と、を有するトランスフォーマと、を備える。

(もっと読む)

1 - 20 / 1,197

[ Back to top ]