Fターム[5J500AK00]の内容

増幅器一般 (93,357) | 回路要素 (18,409)

Fターム[5J500AK00]の下位に属するFターム

演算増幅器(オペアンプ) (1,028)

差動増幅器 (1,173)

インピーダンス変換器(緩衝、バッファ) (308)

反転増幅器(インバータ) (390)

記号又は1本の抵抗の定電流源 (1,226)

その他の定電流源 (132)

記号の可変電流源 (128)

その他の可変電流源 (54)

カレントミラー (1,040)

定電圧発生回路 (216)

バイアス回路 (978)

共振回路、共振器 (109)

同調回路 (26)

遅延回路 (472)

移相器 (300)

電圧、電流比較器 (652)

レベルシフト回路 (119)

ホールド回路 (118)

リミッタ回路 (138)

クランプ回路 (51)

クリップ回路 (27)

減衰回路、アッテネータ (352)

ブートストラップ回路 (4)

時定数回路 (22)

加減算回路 (584)

I−V変換 (156)

電流検出器 (143)

整合器 (603)

微分回路 (12)

積分回路 (193)

発振回路 (358)

デジタル回路(パルス回路) (1,577)

フィルタ (1,427)

単一電源 (565)

複数電源 (153)

電源の切換え、可変電源 (118)

整流回路 (99)

変調器 (588)

復調器、検波器 (416)

チョッパ (20)

直流交流変換(インバータ) (3)

負性抵抗特性を持つ回路 (5)

特徴のあるアース回路 (12)

ジャック、プラグ、コネクタ (24)

スピーカ (516)

ヘッドホン、イヤホン (50)

マイク (49)

冷却装置 (28)

プリント基板 (90)

指示、表示 (15)

その他のマイクロ波要素 (616)

Fターム[5J500AK00]に分類される特許

1 - 20 / 926

広帯域アンプ、広帯域信号通信回路および増幅方法

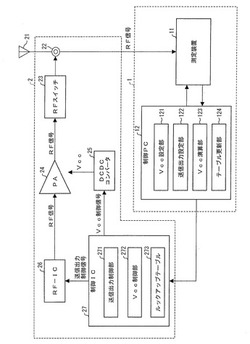

調整装置、通信装置の調整方法、プログラムおよび記録媒体

【課題】製造バラツキに関わらず、通信装置の電力効率を改善することができる調整装置を実現する。

【解決手段】本発明に係る調整装置1は、通信装置2のACLRを測定する測定装置11と、ワースト条件下での規定限界出力におけるACLRが許容値以下となる電源電圧を算出するVcc演算部123と、算出された電源電圧をDCDCコンバータ25の生成する電源電圧Vccの上限値として設定するテーブル更新部124とを備える。

(もっと読む)

オーディオ装置

【課題】本発明は、オーディオ装置において、スピーカの劣化を防止することを目的とするものである。

【解決手段】本発明は、音声入力端子4と、この音声入力端子4に接続されたPWM変調器7と、このPWM変調器7の出力側に接続された増幅器8と、この増幅器8の出力側に接続されたLCフィルタ9と、このLCフィルタ9の出力側に接続された音声出力端子10とを備え、前記LCフィルタ9にフィルタ電流検出器12、あるいは、スピーカ電流検出器を接続し、これらのフィルタ電流検出器、あるいは、スピーカ電流検出器に制御器13を接続し、この制御器13により前記増幅器8を制御する構成とした。

(もっと読む)

トランジスタ回路

【課題】少ない電流量で出力電圧の歪みを低減できるトランジスタ回路を提供する。

【解決手段】エミッタまたはソースと、コレクタまたはドレインと、これらエミッタまたはソース及びコレクタまたはドレイン間の電流量を制御する電圧が印加されるベースまたはゲートと、を備え、コレクタまたはドレインが容量性負荷103に接続されるバイポーラトランジスタまたはMOSトランジスタと、バイポーラトランジスタまたはMOSトランジスタのコレクタまたはドレインに接続され、電流を供給する機能付電流源102と、ベースまたはゲートに入力される電圧の大きさに応じて機能付電流源102の電流を制御するコントロール回路105と、によってトランジスタ回路を構成する。

(もっと読む)

トランスインピーダンスアンプ

【課題】入力電流の大きさに応じた量の電流を入力電流から分流することによりダイナミックレンジが拡大されたトランスインピーダンスアンプ(TIA)において、入力インピーダンスの変化を低減する。

【解決手段】TIA10は、光電流Iinの大きさに応じた出力電圧Voutを生成する。TIA10は、光電流Iinを出力電圧Voutに変換する利得可変増幅回路12と、光電流Iinが大きいほど大きな電流Icdを光電流Iinから分流する分流回路14と、光電流Iinが大きいほど利得可変増幅回路12の利得を小さくする利得調整回路20とを備える。

(もっと読む)

オーディオ信号処理回路およびそれを用いた電子機器

【課題】オーディオ信号処理回路100のノイズを抑制する。

【解決手段】非反転アンプ14は、第3演算増幅器OA3および分圧回路R1、R2を含み、第1バッファ10の出力電圧を非反転増幅する。スイッチSW2は、第3演算増幅器OA3の出力端子とその反転入力端子の間に設けられる。制御回路20は、第2電源電圧VCC2が所定のしきい値電圧より低いときにスイッチSW2をオンし、第2電源電圧VCC2がしきい値電圧より高いときにスイッチSW2をオフする。

(もっと読む)

電力増幅器

【課題】本実施例の一側面における電力増幅器はトランジスタの入力側と出力側の両方に高調波処理を行う整合回路を設けた場合でも発振が生じるのを抑止し、電力増幅器の安定動作を可能とすることを目的とする。

【解決手段】本実施例の一側面における電力増幅器は、基本波と高調波を含む入力信号を入力ノードで受けとり、入力信号の電力を増幅することにより出力信号を生成し、生成された出力信号を出力ノードから出力する増幅回路と、増幅回路の入力ノードに接続され、入力信号の高調波処理を行う入力整合回路と、増幅回路の出力ノードに接続され、出力信号の高調波処理を行う出力整合回路を含む。増幅回路は、入力信号の電力が所定値より大きい値からその所定値より小さい値に低下したとき、生成される出力信号に含まれる高調波の整合点における出力インピーダンスの位相を回転させる。

(もっと読む)

可変利得増幅システム

【課題】入力および出力オフセット補正機能を備えたCCD信号処理チャネルを提供する。

【解決手段】本可変利得増幅回路は、入力信号から不要の相関ノイズ成分を除去する相関二重サンプリング回路1202と、相関二重サンプリング回路の下流側に位置する第1プログラマブル利得増幅器104と、入力が前記第1プログラマブル利得増幅器の入力に接続され、出力が相関二重サンプリング回路の入力に接続され、入力信号のオフセットおよび相関二重サンプリング回路のオフセットのうちの少なくともいずれか一方のために第1オフセット補正を提供する第1オフセット補正回路500と、第1プログラマブル利得増幅器の下流側に位置するアナログ/ディジタル変換器106と、第1プログラマブル利得増幅器の下流側に位置し、第2オフセット補正を提供する第2オフセット補正回路502と、相関二重サンプリング回路の下流側であって、かつ、第1プログラマブル利得増幅器の上流側に位置する画素利得増幅器1204を備えている。

(もっと読む)

歪補償増幅器

【課題】簡素な構成で信号の歪を補償するとともに、信号の出力電力の損失を最小限に抑える。

【解決手段】歪補償増幅器100は、送信信号を生成するDPD処理部104と、DPD処理部104から出力された送信信号を増幅する高周波電力増幅部116と、高周波電力増幅部116から出力された送信信号が入力され、入力された送信信号をアンテナ118へ送るサーキュレータ112と、を備え、サーキュレータ112の漏れ信号をDPD処理部104へ送る。

(もっと読む)

D級増幅回路

【課題】D級増幅回路において、確実に電源パンピングの影響をキャンセルする。

【解決手段】第1スイッチ61がオン、第2スイッチ63がオフの時に、電源電圧VDDと接地間の電流をコンデンサ62に充電させ、第1スイッチ61がオフ、第2スイッチ63がオンの時に、コンデンサ62の電圧と基準電圧Vrとをコンパレータ64により比較する。コンパレータ64の出力をパワーリミット回路30に入力し、コンデンサ62の電圧が基準電圧Vrを超える場合には、PWM変調回路20からの出力信号のパルス幅を制限する。

(もっと読む)

高周波増幅器

【課題】ユニットセルの組み合わせで形成されるすべてのループ発振を抑制することができる高周波増幅器を提供する。

【解決手段】実施の形態に係る高周波増幅器は、入力された信号を分配する分配回路と、分配回路が分配した信号を増幅するFETセルと、分配回路とFETセルのゲート端子との間に直列に接続され、キャパシタと抵抗との並列回路から構成される安定化回路と、FETセルが増幅した信号を合成する合成回路とを備え、安定化回路をFETセルごとに配置する。

(もっと読む)

出力回路及びそれを備えた増幅器

【課題】出力波形に付加される遅延の増大を抑制することが可能な出力回路を提供すること。

【解決手段】本発明にかかる出力回路は、高電位側電源端子と外部出力端子Voutとの間に設けられ、電源電圧VDD〜接地電圧VSS間の電圧範囲を振幅する一対の増幅信号の一方に基づいてソース−ドレイン間に流れる電流が制御される出力トランジスタMP11と、低電位側電源端子と外部出力端子Voutとの間に設けられ、一対の増幅信号の他方に基づいてソース−ドレイン間に流れる電流が制御される出力トランジスタMN11と、電源電圧VDDより低く接地電圧VSSより高い中間電圧VMLが供給されている低電位側電源端子と、出力トランジスタMP11のゲートと、の間に設けられ、出力トランジスタMP11のゲート電圧と中間電圧VMLとの電圧差に基づいて出力トランジスタMP11のゲートをクランプするクランプ用トランジスタMP12と、を備える。

(もっと読む)

無線装置およびその製造方法

【課題】ICチップのプロセスばらつきによって高周波特性がばらついた場合でも、回路特性を最適化できるICチップを基板にフリップチップ実装する無線装置を提供する。

【解決手段】無線装置は、マイクロ波、ミリ波帯の電力増幅器用高周波ICチップ100、バンプ102、入力端子103、出力端子104、基板105、アンダーフィル106、プロセスばらつき検出部110を有する。プロセスばらつき検出部は、プロセスばらつきによる回路特性の変動量をモニタし、モニタされた回路特性の変動量を用いて、算出されたパラーメータを有するアンダーフィル106が、基板105とミリ波帯の電力増幅器用高周波ICチップ100との間に充填されることで、プロセスばらつき及びアンダーフィルの影響があっても、所望の回路特性が得られる無線装置を提供できる。

(もっと読む)

光受信回路用信号増幅器

【課題】受信した光信号を電流信号に変換する受光素子に接続される信号増幅器において、メインアンプの入力段の入力インピーダンスが無視できないときに設けられるレベル調整抵抗の影響を少なくし、広帯域の周波数特性と高い光受信感度特性とを得る。

【解決手段】信号増幅器は、電流信号を電圧に変換して出力するプリアンプと、少なくとも入力段が差動回路からなりプリアンプから出力された電圧信号を増幅するメインアンプと、プリアンプとメインアンプとの間に設けられ電圧信号が供給される2個以上のフォロワ回路と、プリアンプの出力とメインアンプの各入力との間の経路において各フォロワ回路ごとに設けられる抵抗値が等しい抵抗と、抵抗のうちの1つに対して一端が接続し、他端が接地されたコンデンサと、を備えている。コンデンサとそのコンデンサに接続する抵抗とによって、電圧信号の平均電位を検出するローパスフィルタが構成されている。

(もっと読む)

スイッチドキャパシタ積分器

【課題】演算増幅器の充電にかかる負荷を抑え、低消費電力化を実現できるスイッチドキャパシタ積分器を提供する。

【解決手段】演算増幅器122を含む積分器102、演算増幅器122の入力端子122aに信号を入力するスイッチドキャパシタ回路101、演算増幅器122の出力端子122cと接続する出力端子443を有するスイッチドキャパシタ回路103を含み、積分器102及びスイッチドキャパシタ回路101がサンプリング動作と積分動作とを繰返し、スイッチドキャパシタ回路103は、キャパシタ133、キャパシタ133をサンプル、ホールド動作させるスイッチング素子131、132を含み、スイッチング素子131、132がキャパシタ133を、積分動作中にホールド動作させる。

(もっと読む)

音声出力アンプ

【課題】 チャネルセパレーションの改善が可能なヘッドホンアンプ等の音声出力アンプを提供する。

【解決手段】 ヘッドホンアンプ100は、スピーカSPLおよびSPRを各々駆動するLチャネル用増幅回路100LおよびRチャネル用増幅回路100Rを具備する。Lチャネル用増幅回路100LおよびRチャネル用増幅回路100Rの各々は、負荷であるスピーカに供給する電流の経路上に介挿された電流検出抵抗R5を有し、当該増幅回路に与えられる音声入力信号の電圧値に比例した電圧を電流検出抵抗R5の両端間に発生させる電流制御部130を有する。このヘッドホンアンプ100では、Lチャネル音声入力信号ALおよびRチャネル音声信号ARの各電圧値に比例した各電流をスピーカSPLおよびSPRに供給することができるのでチャネルセパレーションを高めることができる。

(もっと読む)

信号変換回路ならびにそれを用いた増幅回路,送信装置および通信装置

【課題】 入力された信号の位相差が大きいときの出力電力の低下を抑制した信号変換回路を提供する。

【解決手段】 第1信号S1,第2信号S2,第1信号S1をφ1だけ遅延させた第3信号S3,第2信号S2をφ2(φ2=φ1+φ3)だけ遅延させた第4信号S4を出力する第1回路4と、第1信号S1,第2信号S2がソース端子,ゲート端子に入力されて第5信号S5を出力するトランジスタ7と、第3信号S3,第4信号S4がソース端子,ゲート端子に入力されて第6信号S6を出力するトランジスタ8と、第6信号S6をφ4(φ4≧0)だけ遅延させた第7信号S7をスイッチ回路57を介して出力し、第5信号S5をφ5(φ5=180°+φ1+φ4)だけ遅延させた第8信号S8を出力する第2回路5と、スイッチ回路57を制御する第3回路6と、第7信号S7,第8信号S8を加算する第4回路9とを有する信号変換回路とする。

(もっと読む)

高速入力インターフェース回路

【課題】高周波における入力インピーダンス整合が改善された、広帯域な高速入力インターフェース回路を提供する。

【解決手段】抵抗R1は、その一端が入力端子DTに接続され、他端がインダクタL1を介して第1の電源端子VCCに接続されている。また、抵抗R2は、その一端が入力端子DCに接続され、他端がインダクタL2を介して電源端子VCCに接続されている。また、抵抗R3は、その一端が入力端子DTに接続され、他端がインダクタL3を介して第2の電源端子VEEに接続されている。また、抵抗R4は、その一端が入力端子DCに接続され、他端がインダクタL4を介して電源端子VEEに接続されている。

(もっと読む)

RFパルス信号生成用スイッチング回路、RFパルス信号生成回路、および物標探知装置

【課題】安定動作させながら、RFパルス信号の波形を高速に立ち下げることができるRFパルス信号生成用スイッチング回路を提供することにある。

【解決手段】ドレインスイッチング回路21は、n型からなる第1、第2、第3のFET211,212,213を備える。第1、第3のFET211,213のゲートには、制御パルスが印加され、ソースは接地されている。第1のFET211のドレインは、第2のFET212のゲートに接続し、第2のFET212のドレインには、駆動電圧Vdsが印加される。第2のFET212のソースと第3のFET213のドレインは接続され、接続点がパワーFET31のドレインに接続されている。第2のFET212のゲートソース間には、第2のFET212がオフ状態からオン状態へ遷移する際のゲート電圧を補償するための電荷を供給するコンデンサ215が接続されている。

(もっと読む)

液晶表示装置の駆動回路

【課題】入出力間オフセット電圧を削減しつつ消費電流を削減する。

【解決手段】第1導電型の第1差動回路は、第1入力信号と出力信号とを差動入力信号とする。第1導電型の第2差動回路は、第2入力信号と出力信号とを差動入力信号とする。第2導電型の第3差動回路は、第1入力信号と出力信号とを差動入力信号とする。第2導電型の第4差動回路は、第2入力信号と出力信号とを差動入力信号とする。出力段回路は、第1乃至第4差動回路の出力に基づいて出力信号を出力する。差動増幅器は、上記第1乃至第4差動回路、出力段回路を具備し、制御信号に基づいて、第1乃至第4差動回路を形成するトランジスタのチャネル長とチャネル幅との比を変更する。

(もっと読む)

1 - 20 / 926

[ Back to top ]