Fターム[5J500AK01]の内容

Fターム[5J500AK01]に分類される特許

1 - 20 / 1,028

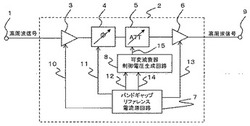

高周波増幅回路

【課題】 ステップ式可変減衰器を実装することなく、低雑音特性及び高飽和特性を確保しながら、温度変動に伴う利得変化を抑制することができる高周波増幅回路を得る。

【解決手段】 高周波信号を減衰させる可変減衰器と、半導体のバンドギャップに基づき温度比例電流及び温度固定電流を出力するバンドギャップリファレンス電流源回路と、前記温度比例電流及び前記温度固定電流を入力とし、温度に対して所定の傾きで変化する電圧を出力する可変減衰器制御電圧生成回路とを備え、前記可変減衰器制御電圧生成回路の出力電圧で前記可変減衰器の減衰量を制御する。

(もっと読む)

オーディオ信号処理回路およびそれを用いた電子機器

【課題】オーディオ信号処理回路100のノイズを抑制する。

【解決手段】非反転アンプ14は、第3演算増幅器OA3および分圧回路R1、R2を含み、第1バッファ10の出力電圧を非反転増幅する。スイッチSW2は、第3演算増幅器OA3の出力端子とその反転入力端子の間に設けられる。制御回路20は、第2電源電圧VCC2が所定のしきい値電圧より低いときにスイッチSW2をオンし、第2電源電圧VCC2がしきい値電圧より高いときにスイッチSW2をオフする。

(もっと読む)

電流出力回路

【課題】アイドリング電流の影響を受けることなく高精度に電流検出を行うことが可能な電流出力回路を小規模な回路で実現すること。

【解決手段】第1の増幅器と、第1の増幅器の出力を入力するプッシュプル形出力段と、プッシュプル形出力段の第1のトランジスタ及び第2のトランジスタに対して夫々カレントミラー接続した電流検出器の第3のトランジスタ及び第4のトランジスタと、第3のトランジスタのドレインを第1のトランジスタのドレインの電位と等しくするバッファ回路と、第4のトランジスタのドレインに接続された電流検出抵抗と、を備える。プッシュプル形出力段の増幅信号は、負荷を介して第1の増幅器の反転入力端子に接続される。この構成により、電流検出抵抗にアイドリング電流を流さないようにすることができる。

(もっと読む)

半導体装置

【課題】トランジスタは作製工程や使用する基板の相違によって生じるゲート絶縁膜のバラツキや、チャネル形成領域の結晶状態のバラツキの要因が重なって、しきい値電圧や移動度にバラツキが生じてしまう影響を排除する。

【解決手段】アナログ信号を入力するトランジスタ、及び定電流源としての機能を有するトランジスタのゲート・ソース間電圧又はしきい値電圧に応じた電圧を取得、保持し、後に入力される信号電位に上乗せすることで、トランジスタ間のしきい値電圧のバラツキやゲート・ソース間電圧のばらつきをキャンセルする半導体装置を提供する。ゲート・ソース間電圧又はしきい値電圧に応じた電圧の取得、保持には、トランジスタのゲート・ソース間及びゲート・ドレイン間に設けたスイッチ、及びゲート・ソース間に設けた容量を用いる。

(もっと読む)

スイッチドキャパシタ積分器

【課題】演算増幅器の充電にかかる負荷を抑え、低消費電力化を実現できるスイッチドキャパシタ積分器を提供する。

【解決手段】演算増幅器122を含む積分器102、演算増幅器122の入力端子122aに信号を入力するスイッチドキャパシタ回路101、演算増幅器122の出力端子122cと接続する出力端子443を有するスイッチドキャパシタ回路103を含み、積分器102及びスイッチドキャパシタ回路101がサンプリング動作と積分動作とを繰返し、スイッチドキャパシタ回路103は、キャパシタ133、キャパシタ133をサンプル、ホールド動作させるスイッチング素子131、132を含み、スイッチング素子131、132がキャパシタ133を、積分動作中にホールド動作させる。

(もっと読む)

オフセット電圧補償装置

【課題】オフセット電圧補償装置において、部品点数の増加を抑えながら、増幅器のオフセット電圧を補償して、センサ部の直流出力信号の真値を検出する。

【解決手段】オフセット電圧補償装置1は、電源2と接続され物理量を計測して出力信号に変換するセンサ部3と、センサ部3の入力を短絡する切替器4と、センサ部3の出力信号を増幅する増幅器5と、増幅器5の出力に基づいて電気量を演算する演算器6とを備える。演算器6は、センサ部3の入力を短絡していない時の増幅器5の出力から、短絡時の増幅器5の出力を減算して信号成分の差分を抽出する。次に、当該信号成分の差分と、センサ部3の抵抗値及び切替器4の抵抗値から定められる所定の係数とを用いて、センサ部3の出力信号の真値を検出する。

(もっと読む)

定電流回路

【課題】1または複数の他の定電流回路との間で共通インピーダンスを共有する定電流回路の出力電流に、他の定電流回路の出力電流に起因した誤差が生じることを防ぐ。

【解決手段】オペアンプと、当該オペアンプの出力端子にゲートが接続されドレインが当該定電流回路の出力端となる電界効果トランジスタと、この電界効果トランジスタのソースと共通インピーダンスとの間に介挿された抵抗と、を有する定電流回路に、共通インピーダンスおよび抵抗の共通接続点の電圧を第1の基準電圧とし、オペアンプの非反転入力端子には、第2の基準電圧と第1の基準電圧と電位差を所定の分圧比で分圧した電圧を印加し、同反転入力端子には、電界効果トランジスタのソースおよび抵抗の共通接続点の電圧と第3の基準電圧との電位差を所定の分圧比で分圧した電圧を印加する分圧回路を設ける。

(もっと読む)

対数/逆対数変換回路

【課題】温度補正を行なわなくても、逆対数変換した際に得られる出力信号が線形性を保つことができる対数/逆対数変換回路を提供する。

【解決手段】対数変換回路1の電流帰還用トランジスタTR2を通過した電流信号Iinを逆対数変換回路2に入力し、電流/電圧変換回路3でこの電流信号Iinをこれに対応した電圧値に変換した後、引算回路4で電流/電圧変換回路3の出力電圧と予め設定された基準電圧との差分を出力する構成とし、かつ引算回路4はその差分出力が電流信号Iinに比例した線形性をもつように回路定数を設定している。

(もっと読む)

音声出力アンプ

【課題】 チャネルセパレーションの改善が可能なヘッドホンアンプ等の音声出力アンプを提供する。

【解決手段】 ヘッドホンアンプ100は、スピーカSPLおよびSPRを各々駆動するLチャネル用増幅回路100LおよびRチャネル用増幅回路100Rを具備する。Lチャネル用増幅回路100LおよびRチャネル用増幅回路100Rの各々は、負荷であるスピーカに供給する電流の経路上に介挿された電流検出抵抗R5を有し、当該増幅回路に与えられる音声入力信号の電圧値に比例した電圧を電流検出抵抗R5の両端間に発生させる電流制御部130を有する。このヘッドホンアンプ100では、Lチャネル音声入力信号ALおよびRチャネル音声信号ARの各電圧値に比例した各電流をスピーカSPLおよびSPRに供給することができるのでチャネルセパレーションを高めることができる。

(もっと読む)

レギュレータ用半導体集積回路

【課題】 過電流保護のための出力電流−出力電圧特性として所望の特性が得られ、通常動作領域において負荷電流が多くなった場合にも過電流保護ポイントまで正常な出力電圧制御動作が行えるレギュレータ用の半導体集積回路を提供する。

【解決手段】 電圧入力端子と出力端子との間に接続された制御用トランジスタ(M1)によって流される出力電流に縮小比例した電流を流す電流監視用トランジスタ(M2)と、該電流監視用トランジスタに流れる電流を電圧に変換する電流−電圧変換手段(R3)とを備え、通常動作状態では前記電流監視用トランジスタに流れる電流を電流−電圧変換手段へ流さないようにし、電流監視用トランジスタに流れる電流が所定値以上になった場合には、電流監視用トランジスタに流れる電流を電流−電圧変換手段へ流し、該電流−電圧変換手段により変換された電圧に基づいて制御用トランジスタをオフさせるように過電流保護回路(13)を構成した。

(もっと読む)

半導体集積回路、それを備えた受信装置及び無線通信端末

【課題】増幅回路を速やかに正常動作に復帰させることが可能な半導体集積回路を提供すること。

【解決手段】本発明にかかる半導体集積回路は、容量素子C1T,C1Bを介してそれぞれ供給される第1及び第2電圧信号の電位差を増幅し、第1及び第2増幅信号を出力する全差動増幅回路OPA1と、第1増幅信号を全差動増幅回路OPA1の反転入力端子に帰還する抵抗素子RFBTと、第2増幅信号を全差動増幅回路OPA1の非反転入力端子に帰還する抵抗素子RFBBと、所定電圧VBを生成する電圧生成部50と、電圧生成部50によって生成された所定電圧VBを、全差動増幅回路OPA1のそれぞれの入力端子に伝達する抵抗素子RBT,RBBと、を備える。

(もっと読む)

基準電圧発生回路

【課題】小規模の付加回路により、基準電圧の温度特性を簡易な調整によって十分に改善することができる基準電圧発生回路を提供する

【解決手段】バイポーラトランジスタ106、バイポーラトランジスタ106と並列に接続されるバイポーラトランジスタ107、バイポーラトランジスタ107のエミッタに一端が接続される抵抗素子104、バイポーラトランジスタ106のベース電位と、バイポーラトランジスタ107のベース電位との差分によって生じる差電圧を発生させる抵抗素子109、バイポーラトランジスタ106のエミッタ電位と抵抗素子104の他端の電位とが等しくなるように動作する演算増幅器105によって基準電圧発生回路を構成し、抵抗素子109が生成する差電圧が、温度によって変化する。

(もっと読む)

オーディオ信号処理回路およびそれを用いた電子機器

【課題】オーディオ信号処理回路100のノイズを抑制する。

【解決手段】第1バッファ10の電源端子には、第1電源からの第1電源電圧VCC1が供給される。第2バッファ12の電源端子には、第1電源からの第1電源電圧VCC1が供給される。非反転アンプ14の電源端子には、第2電源電圧VCC2が供給される。起動電圧源16は、その電源端子に第2電源電圧VCC2を受け、起動電圧VSTARTを生成する。制御回路20は、第2電源電圧VCC2が所定のしきい値電圧より低いときにスイッチSW1をオンし、第2電源電圧VCC2がしきい値電圧より高いときにスイッチSW1をオフする。

(もっと読む)

センサ信号処理装置

【課題】簡単な構成で入力オフセット電圧の温度依存性が小さいセンサ信号処理装置を提供する。

【解決手段】センサ用電源として第1の電源電圧V´ccを供給されて動作し、センサ出力Vs1、Vs2を出力するセンサ部100と、信号処理用電源として第2の電源電圧Vccを供給されて動作し、センサ出力Vs1、Vs2が入力される差動対を使用する差動増幅部を有して信号処理を行なう信号処理部200と、を有してセンサ信号処理装置1を構成する。この第1の電源電圧V´ccは、信号処理部200の差動増幅部250の入力電圧範囲の下限領域に設定される。

(もっと読む)

増幅回路およびA/D変換器

【課題】最小限の構成を用いて、演算増幅器の入出力端子間の寄生容量に起因する増幅回路の演算誤差を補償し、高精度の増幅率を得る。

【解決手段】増幅回路10は、一方の端子が演算増幅器A1の反転入力端子に、他方の端子が演算増幅器A1の反転出力端子に接続された容量CP5と、一方の端子が演算増幅器A1の非反転入力端子に、他方の端子が演算増幅器A1の非反転出力端子に接続された容量CN5とを備えている。

(もっと読む)

差動増幅回路

【課題】正常動作する入力信号電圧範囲を広げることが可能な差動増幅回路を提供する。

【解決手段】差動信号が入力され、該差動信号を構成する2つの信号の電圧の差を増幅して出力する差動増幅回路であって、差動信号を構成する2つの信号の平均電圧を検出する平均電圧検出回路2と、平均電圧検出回路2で検出した平均電圧を基準として正負の電源電圧を生成する電源電圧発生回路3と、電源電圧発生回路3で生成した正負の電源電圧を正電源、負電源として用い、差動信号を構成する2つの信号の電圧の差を増幅して出力する差動増幅回路本体4と、を備えたものである。

(もっと読む)

差動増幅回路

【課題】正常動作する入力信号電圧範囲を広げることが可能な差動増幅回路を提供する。

【解決手段】差動信号が入力され、該差動信号を構成する2つの信号の電圧の差を増幅して出力する差動増幅回路であって、差動信号を構成する2つの信号の平均電圧を検出する平均電圧検出回路2と、差動信号を構成する2つの信号のそれぞれに対応するように設けられ、差動信号を構成する一の信号を、平均電圧検出回路2で検出した平均電圧と等しい電圧降圧して出力する2つの電圧シフト回路3,4と、2つの電圧シフト回路3,4のそれぞれから出力される2つの信号の電圧の差を増幅して出力する差動増幅回路本体5と、を備えたものである。

(もっと読む)

抵抗の調整機能を有する演算回路

【課題】MOSスイッチによる抵抗の調整機能を有する演算回路において、面積の増加を最小限に留め、かつ、非常に簡易な方法でMOSスイッチの寄生容量の影響を抑える演算回路を提供する。

【解決手段】MOSスイッチ21−23のゲートやバックゲートに、調整対象の抵抗11−13よりも数倍以上大きな抵抗31−33、61を設けることにより、寄生容量でできる極とほぼ同じ周波数にゼロが発生し、寄生容量の影響を抑えることができる。この抵抗には、絶対値バラつきや温度特性、相対バラつきやノイズ等の特性は要求されないため、用いるプロセスで最もシート抵抗の高い抵抗を細い幅で作成すればよく、面積の増加量は少ない。また、抵抗は容量よりも微細化が容易であるため、今後更にプロセスの微細化が進んでも本発明を変わらず使用できる。

(もっと読む)

RFパルス信号生成用スイッチング回路、RFパルス信号生成回路、および物標探知装置

【課題】安定動作させながら、RFパルス信号の波形を高速に立ち下げることができるRFパルス信号生成用スイッチング回路を提供することにある。

【解決手段】ドレインスイッチング回路21は、n型からなる第1、第2、第3のFET211,212,213を備える。第1、第3のFET211,213のゲートには、制御パルスが印加され、ソースは接地されている。第1のFET211のドレインは、第2のFET212のゲートに接続し、第2のFET212のドレインには、駆動電圧Vdsが印加される。第2のFET212のソースと第3のFET213のドレインは接続され、接続点がパワーFET31のドレインに接続されている。第2のFET212のゲートソース間には、第2のFET212がオフ状態からオン状態へ遷移する際のゲート電圧を補償するための電荷を供給するコンデンサ215が接続されている。

(もっと読む)

電子回路およびその制御方法

【課題】ドレインアイドル電流のドリフトを直接補償すること。

【解決手段】入力信号が入力するゲートと、出力信号が出力するドレインとを有するFETを含む電子回路の制御方法であって、前記FETのゲートに前記入力信号が入力してからの時間t経過後における前記入力信号x(t)に対応するドレインアイドル電流の変化量ΔIdq(t)を算出するステップS10と、前記変化量ΔIdq(t)を補償するためのゲートバイアス電圧Vgを算出するステップS12と、前記ゲートバイアス電圧を前記FETのゲートに印加するステップS14と、を含むことを特徴とする電子回路の制御方法。

(もっと読む)

1 - 20 / 1,028

[ Back to top ]